Fターム[5F033QQ00]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095)

Fターム[5F033QQ00]の下位に属するFターム

露光 (971)

エッチング (29,543)

リフトオフ (276)

研磨 (4,337)

エネルギービームの照射 (929)

不純物導入、イオン注入 (1,611)

選択導電化、絶縁化によるパターン形成 (22)

合金化処理(熱処理を含む) (771)

熱処理 (5,181)

冷却(自然冷却は除く) (23)

酸化処理 (296)

窒化処理 (195)

清浄化 (1,803)

空気、大気に晒さない連続処理 (330)

外力を加えて形状を変化させるもの (66)

Fターム[5F033QQ00]に分類される特許

81 - 100 / 741

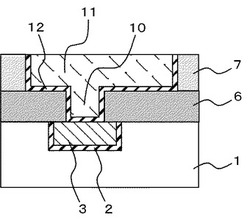

半導体装置および半導体装置の製造方法

【課題】機械的強度および密着力に優れた低誘電率の層間絶縁層を有する半導体装置を提供すること。

【解決手段】基板上に形成された、SiO2骨格を含む第1の多孔質層6と、第1の多孔質層6の直上に形成された、SiO2骨格を含む第2の多孔質層7と、第1の多孔質層6に埋め込まれたビア10と、第2の多孔質層7に埋め込まれた配線11と、を有し、第1の多孔質層6の孔密度x1は40%以下であり、第2の多孔質層7の孔密度x2は、(x1+5)%以上である半導体装置を提供する。

(もっと読む)

半導体デバイス製造方法

【課題】バリア金属膜とCVD法によって形成される金属導体膜である銅膜との間の密着性に優れた半導体デバイスの製造方法を提供すること。

【解決手段】基板上に直接にまたは絶縁体膜を介してバリア金属膜を形成する工程と、該バリア金属膜上にCVD法によって銅膜を形成する工程とを含む半導体デバイス製造方法において、該バリア金属膜を形成する工程と該銅膜を形成する工程との間に、加熱条件下アンモニア、水素、またはシランのうちの少なくともいずれか1つを含む第1の還元性ガスに暴露する工程と、該銅膜を形成する工程の後に、加熱条件下第2の還元性ガスに暴露する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】生産性の低下を抑制しつつ、配線部分の抵抗の増大を抑制することができるとともに、電気的なリークの発生を抑制することのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】層間絶縁膜としてポーラス状の低誘電率膜を有する半導体装置を基板上に形成する半導体装置の製造方法であって、前記基板に前記低誘電率膜を形成する低誘電率膜形成工程と、エッチングにより前記低誘電率膜にトレンチ又はホールを形成するエッチング工程と、前記トレンチ又はホール内に、ニトロ化合物のプラズマを作用させて前記低誘電率膜のエッチングにより露出された面を改質する改質工程と、前記トレンチ又はホール内に導体を充填する導体形成工程と、を具備している。

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】、基材の表面を冷却したまま溶媒を除去しない場合に比べ、パターンが精度良く形成されるパターン形成装置を提供する。

【解決手段】基材20を冷却する基材冷却手段22と、前記基材冷却手段によって冷却された前記基材の表面に、パターン形成材料、及び溶媒を含む組成物18を付与して該組成物のパターンを描画するパターン描画手段24と、前記基材の表面に描画された前記組成物のパターンから該基材を冷却したまま前記溶媒を除去する溶媒除去手段26と、を有するパターン形成装置10。溶媒除去後、加熱を行って分散剤を除去する加熱手段28を備えてもよい。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

配線基板およびその製造方法

【課題】配線電極の幅が小さく、かつ厚みの大きい配線電極である、配線電極の断面形状について、所望のアスペクト比の配線電極を有する配線基板およびその製造方法を提供する。

【解決手段】この発明にかかる配線基板10は、絶縁基板12と、該絶縁基板12上に配線電極22が形成された配線基板であって、絶縁基板12上に保護膜14を形成し、レーザー光16の照射により保護膜14に保護膜14の厚さ以下の幅を有する配線パターン溝18を形成し、該配線パターン溝18に導電性ペースト20を埋め込んで、該導電性ペースト20の塗膜を形成する。そして、絶縁基板12上に形成された保護膜14を除去することにより絶縁基板12上に、所望のアスペクト比を有する配線電極22が形成された配線基板10が得られる。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、下層配線としてCu配線を含む多層配線と、前記Cu配線を形成するために用いられるCuアクセサリとが形成された半導体基板を、ポリイミド膜で覆う工程と、前記多層配線の最上層配線の表面および前記Cuアクセサリの表面を露出させる工程と、前記半導体基板をCu腐食防止剤の蒸気にさらして、前記最上層配線の表面および前記Cuアクセサリの表面にCu腐食防止膜を形成する工程と、前記最上層配線の表面に形成されたCu腐食防止膜を選択的に除去する工程と、前記Cuアクセサリの表面にCu腐食防止膜が形成された状態で、前記ポリイミド膜をベーク処理する工程とを有する。

(もっと読む)

低k誘電体と導電材料との接着改善

【課題】銅ダマシン配線上への誘電体層の形成において、導電材料と誘電体層間の密着性を向上する半導体装置の製造方法を提供する。

【解決手段】オルガノシロキサンからなる第2誘電体層118に、TaNからなる金属バリア層124とCuからなる導電性金属特徴部126を形成する。平坦化後アンモニアプラズマ処理還元により表面の酸化物を除去する。連続して真空を破壊せずに、トリメチルシランからなる有機ケイ素化合物を導入し、プラズマプロセスによりSiCN膜130を形成し、さらに連続してSiC膜132を堆積する。酸化物の除去から誘電体層の形成までインサイチュで行うことが可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

回路基板の製造方法、タッチパネル、電気光学装置、電子機器

【課題】互いに交差し、絶縁膜を介して前記絶縁膜上を配線するブリッジ配線の導通不良の原因の絶縁膜のしみ上がりを防ぐ。

【解決手段】互いに交差する複数の配線と、前記複数の配線の交差部において、前記配線間に形成される絶縁層とを含む回路基板の製造方法であって、基板配線形成工程と、絶縁層を形成する絶縁層形成工程と、前記絶縁層の表面に前記基板配線に交差するブリッジ配線を形成するブリッジ配線形成工程とを含み、前記絶縁膜形成工程は、前記絶縁膜の材料を含む機能液を液滴として吐出する液滴吐出工程を含み、前記機能液はレベリング剤を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

紫外線硬化型インクジェット記録用インク、それから得られた絶縁膜、電子素子及び電子素子の製造方法

【課題】 合成樹脂基板及び電極の両方に対するレベリング性に優れ、平滑性及び絶縁性に優れた硬化膜が得られる紫外線硬化型インクジェット記録用インク、それから得られた絶縁膜、電子素子及び電子素子の製造方法を提供する。

【解決手段】 エネルギー線硬化性化合物、光重合開始剤、及び表面張力調整剤を含有し、硬化性を有さないポリマーを含まず、25℃における粘度が100mPa・sec以下、表面張力が22〜35mN/m、かつインク硬化膜の体積抵抗率1013Ω・cm以上であり、絶縁破壊強度1.2MV/cm2以上である、絶縁膜を形成するためのソルベントフリー紫外線線硬化型インクジェット記録用インク、それを硬化してなる絶縁膜等を提供する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写によるマスクパターンの倒れ、マスクパターンの接触を抑制する。

【解決手段】シリコン基板1上に、第1のTEOS酸化膜2、シリコン窒化膜3、第1のアモルファスシリコン膜4、第2のTEOS酸化膜5を積層形成する。レジストによるパターニングでTEOS酸化膜5を第1幅D1の中間パターン5aに加工し、スリミング処理をして第2幅D2の芯材パターン5bを形成する。第2のアモルファスシリコン膜6を形成してスペーサ処理をすることで側壁膜6aを形成し、芯材パターン5bを除去して孤立したマスクパターン6bを得る。下地に同じアモルファスシリコン膜4を用いるので、マスクパターン6bの倒れや接触の発生を抑制できる。

(もっと読む)

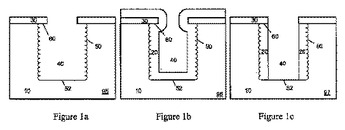

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

81 - 100 / 741

[ Back to top ]