Fターム[5F033QQ00]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095)

Fターム[5F033QQ00]の下位に属するFターム

露光 (971)

エッチング (29,543)

リフトオフ (276)

研磨 (4,337)

エネルギービームの照射 (929)

不純物導入、イオン注入 (1,611)

選択導電化、絶縁化によるパターン形成 (22)

合金化処理(熱処理を含む) (771)

熱処理 (5,181)

冷却(自然冷却は除く) (23)

酸化処理 (296)

窒化処理 (195)

清浄化 (1,803)

空気、大気に晒さない連続処理 (330)

外力を加えて形状を変化させるもの (66)

Fターム[5F033QQ00]に分類される特許

21 - 40 / 741

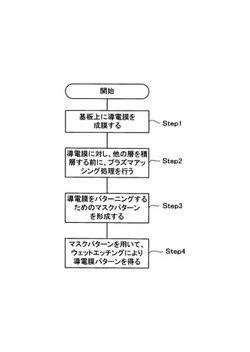

導電膜パターンの形成方法

【課題】信頼性の高い導電膜パターンの製造方法を提供する。

【解決手段】本発明に係る導電膜パターンの製造方法は、基板10上に導電膜21を成膜し、導電膜21の表面に対して他の層を積層する前に、酸素をプラズマ化したプラズマアッシング処理を施し、表面処理した導電膜21上に、当該導電膜21をパターン形成するためのマスクパターン30を形成する。次いで、マスクパターン30を用いて導電膜21をウェットエッチングによりパターン形成する。基板10は、半導体基板であることが好ましい。導電膜パターンは、例えば、配線、電極パッド等である。

(もっと読む)

プラズマ処理方法及びプラズマアッシング装置

【課題】Low-k膜を有する試料のプラズマアッシング処理において、高速にアッシング処理を行いつつ、Low-k膜に対する膜ダメージを抑制または低減する処理方法を提供する。

【解決手段】Low-k膜15を有する試料をプラズマ処理するプラズマ処理方法において、前記試料をプラズマエッチングする工程と、炭化水素系ガスであるメタン(CH4)ガス19と希ガスであるアルゴン(Ar)ガスとからなる混合ガスを用いて、プラズマエッチング工程でプラズマエッチングされたレジストマスク13、炭素ハードマスク14、反応生成物16が付着したLow-k膜15を有する試料を、メタン(CH4)ガス19からの炭素(C+)ラジカル18と水素(H+)ラジカル19により、プラズマアッシングする工程を有するプラズマ処理方法である。

(もっと読む)

アルミニウム体を備えた基体の製造方法

【課題】基体上に成膜特性(反射率、及び密着性)に優れた膜状のアルミニウム体を形成することができるアルミニウム体を備えた基体の製造方法を提供する。

【解決手段】基体をプラズマ処理するプラズマ処理工程と、プラズマ処理された基体上に、アミン化合物と水素化アルミニウムとの錯体及び有機溶媒を含有するアルミニウム体形成用組成物を塗布して、上記基体上に上記組成物からなる塗布層を形成させる塗布工程と、上記塗布層に加熱および光照射の少なくともいずれか一方を行うことにより、膜状のアルミニウム体を形成させるアルミニウム膜形成工程と、を含むアルミニウム体を備えた基体の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】精密なエッチング制御を必要とすることなく、ビアホール構造を形成することを可能とするとともに、エッチング後の洗浄を容易にする。

【解決手段】半導体装置において、第1の基板11と、第1の基板表面に形成された素子領域12,13と、素子領域と接続され、第1の基板11上に形成された電極14,15,16と、第1の基板11と積層される第2の基板17と、第2の基板17を貫通し、電極上に配置されるビアホール18a,18b,18cと、ビアホール内に形成される金属層19a,19b,19cと、を備える。

(もっと読む)

膜の製造方法および表示装置の製造方法

【課題】微細な貫通孔を有する膜を形成することが可能な膜の製造方法、およびこの方法を用いた表示装置の製造方法を提供する。

【解決手段】第1パターンおよび第2パターンを有する凹版を用いて、第1パターンの膜を基材へ形成する第1転写工程と、第1パターンの膜上に第2パターンの膜を形成して、基材上に貫通孔を有する膜を形成する第2転写工程とを備えた膜の製造方法。基板に、TFT,絶縁膜および有機EL素子を順に形成する工程を含み、絶縁膜を形成する工程は、第1パターンおよび第2パターンを有する凹版を用いて、第1パターンの膜を基材へ形成する第1転写工程と、第1パターンの膜上に第2パターンの膜を形成して、基材上に貫通孔を有する膜を形成する第2転写工程とを備えた表示装置の製造方法。

(もっと読む)

半導体基板内の埋込ボイドを検出するための方法

【課題】半導体基板内又は基板上に形成された構造内の埋込ボイドを検出するための方法を提供する。

【解決手段】構造を形成するための少なくとも1つの処理ステップを実施する工程と、基板の質量M1を測定する工程と、熱処理を実施する工程と、基板の質量M2を測定する工程と、前記実施した熱処理の前後で測定した基板の質量の差を計算する工程と、前記質量の差を所定値と比較することにより、前記構造内の埋込ボイドの存在を推測する工程とを含む。

(もっと読む)

電子部材の製造方法

【課題】従来の方法では凹版印刷および平板印刷に向かなかったインクであっても、凹版印刷および平板印刷で印刷することの可能な電子部材の製造方法を提供する。

【解決手段】下記の関係式(1)、(2)を満たす電子材料層および粘着材料層を積層してなる積層インクが、凹版を用いて基材の表面に直接転写される。これにより、電子材料層が凹版印刷に向かない性質を有している場合であっても、粘着材料層の性質を活かして、電子材料層を含む積層インクを基材上に滲みなく印刷することができる。

E2<E3<E1またはE1<E3<E2…(1)

|E1−E2|>|E3−E2|…(2)

E1:版面の表面自由エネルギー

E2:電子材料層の表面自由エネルギー

E3:粘着材料層の表面自由エネルギー

(もっと読む)

パターン形成装置およびパターン形成方法

【課題】基板表面に塗布液を塗布して硬化させることにより基板表面に所定のパターンを形成するパターン形成技術において、パターンのさらなる微細化・高アスペクト化を可能とする技術を提供する。

【解決手段】吐出ノズル523から基板Wに吐出される隔壁形成用塗布液の側面部に対して集中的に、ライトガイド533の下端に設けたレンズ534で収束された光を照射する。塗布液の側面部が他の部分に先んじて硬化することで、表面張力によって表面が丸くなったり塗布液が広がるのを抑制することができるため、薄く均一で側面部が急峻に立ち上がる隔壁Bを形成することができる。

(もっと読む)

パターン転写方法

【課題】エッチングを行わずに残膜除去処理を行うことが可能なパターン転写方法を提供する。

【解決手段】実施形態のパターン転写方法では、被加工基板上に光反応性樹脂を形成する。さらに、前記方法では、凹凸パターンを有する透明基板と、前記凹凸パターンの表面の一部に形成された遮光膜と、を備えるモールドを前記光反応性樹脂に押印する。さらに、前記方法では、前記モールドが前記光反応性樹脂に押印された状態で、前記モールドを介して前記光反応性樹脂に光を照射する。さらに、前記方法では、前記光反応性樹脂に光を照射した後に、前記モールドが前記光反応性樹脂に押印された状態で、前記光反応性樹脂を加熱する。さらに、前記方法では、前記光反応性樹脂の加熱後に、前記モールドを前記光反応性樹脂から離型する。さらに、前記方法では、前記モールドの離型後に、前記光反応性樹脂を洗浄液で洗浄する。

(もっと読む)

半導体装置

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置100を、第1半導体部と、第2半導体部とを備える構成とする。第1半導体部には、接合界面側の表面に形成されかつ第1の方向に延在する第1電極16を設ける。そして、第2半導体部には、接合界面で第1電極16と接合されかつ第1の方向と交差する第2の方向に延在する第2電極26を設ける。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

誘電フィルム及び材料における疎水性を回復する方法

【課題】誘電率の増加、シラノールの増加、または有機部分の減少、の少なくとも一つによって損傷した、基体上のシリカ誘電フィルムの損傷を回復する。

【解決手段】基体上のそのような損傷シリカ誘電フィルムを表面改質組成物と接触させて、該損傷シリカ誘電フィルムの誘電率の減少、該損傷シリカ誘電フィルムの誘電率のシラノールの減少、該損傷シリカ誘電フィルムの誘電率の有機部分の増加、の1つ以上をもたらす。このとき、該損傷シリカ誘電フィルムに疎水性を与える。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

シリカ系被膜の形成方法及び電子部品

【課題】密着性に優れ、電気的信頼性の高いシリカ系被膜の硬化物が得られるシリカ系被膜の形成方法を提供する。

【解決手段】本発明のシリカ系被膜の形成方法は、下記一般式(1)で表される化合物を含むシラン化合物を加水分解縮合して得られるシロキサン樹脂と、光酸発生剤及び光塩基発生剤からなる群より選択される少なくとも1種と、シロキサン樹脂を溶解可能な溶媒と、オニウム塩と、を含有する感光性樹脂組成物を基板上に塗布して被膜を得る工程と、パターンマスクを介して被膜を露光する工程と、露光する工程の後に被膜を加熱する工程と、加熱する工程の後に被膜の未露光部を現像によって除去する工程と、除去する工程の後に残存する被膜に紫外線を照射して、パターンを有するシリカ系被膜を得る工程と、を備える。

(もっと読む)

電極構造及びその製造方法

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

銅配線の形成方法、配線基板の製造方法および配線基板

【課題】銅粒子の酸化、燃焼を防止し、銅配線の導電性を向上させるとともに経時劣化を抑えることができる銅配線の形成方法、配線基板の製造方法および配線基盤を提供することを目的とする。

【解決手段】粒子径が100nm以下の炭素被膜銅粒子14を、基板10上に配線パターンを形成するパターン形成工程と、配線パターンを酸素プラズマ処理する酸素プラズマ処理工程と、配線パターンを還元プラズマ処理する還元プラズマ処理工程と、を有することを特徴とする銅配線の形成方法、配線基板の製造方法および配線基板である。

(もっと読む)

銅配線の形成方法、配線基板の製造方法および配線基板

【課題】銅配線の導電性を向上させるとともに、経時変化による劣化を抑制することができ銅配線の形成方法、配線基板の製造方法および配線基板を提供することを目的とする。

【解決手段】粒子径が100nm以上の銅粒子14を分散させた分散液12を塗布し、基板10上に配線パターンを形成するパターン形成工程と、配線パターンを150℃未満の温度で乾燥を行なう乾燥工程と、乾燥工程後の配線パターンを加圧する加圧工程と、加圧工程後の配線パターンを加熱する加熱工程と、加熱工程後の配線パターンを還元処理する還元処理工程と、を有することを特徴とする銅配線の形成方法、配線基板の製造方法および配線基板である。

(もっと読む)

処理方法および記憶媒体

【課題】低誘電率膜のダメージ回復処理を行う際に、比誘電率やリーク電流値を低く維持しつつ内部の水分を除去することができる処理方法を提供すること。

【解決手段】被処理基板に形成された、表面部分にダメージ層を有する低誘電率膜に回復処理を施すにあたり、その分子が、低誘電率膜のダメージ層の内部に浸透できる程度に小さく、ダメージ層内の水分を除去することが可能な第1処理ガスと、ダメージ層の表面に疎水性で緻密な改質層を形成する第2処理ガスとを低誘電率膜のダメージ層に作用させる。

(もっと読む)

21 - 40 / 741

[ Back to top ]