Fターム[5F033RR05]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 窒化物 (4,436)

Fターム[5F033RR05]の下位に属するFターム

SiN (4,133)

Fターム[5F033RR05]に分類される特許

21 - 40 / 303

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

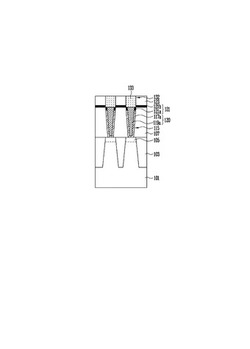

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】半導体素子の第1領域と接続される表面電極17、および通路12の少なくとも一部に、半導体素子の第2領域と接続される第1金属配線18を形成する。その後、はんだ29が実装されない通路12bに形成する第1保護膜25の高さが、はんだ29が実装される通路12aに形成する第1保護膜25の高さよりも高くなるように、注入器32を用いて第1保護膜25を通路12に塗布する。続いて、表面電極17および第1保護膜25の上に金属層27、28を形成してはんだ29が実装されない通路12bに形成した第1保護膜25が金属層27、28から露出するように、はんだ29が実装されない通路12bに形成した第1保護膜25の一部および金属層27、28を切削する。

(もっと読む)

半導体装置の製造方法

【課題】金属コンタクトを安定に形成できる半導体装置の製造方法を提供する。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

(もっと読む)

チップの製造方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】選択メタルキャップを用いることなしに、生産性の高いエアギャップ配線を形成する。

【解決手段】ウエハ14上の絶縁膜200にCuダマシン配線210を形成する第1の工程と、ウエハ14上に第1のバリア膜220を形成する第2の工程と、後続する接続孔242を開口する工程において、接続孔242の孔底部244に露出するCu配線206と隣接する絶縁膜200、及び最小寸法スペースの3倍以上の幅をもつ幅広スペース200aを保護するように、第1のバリア膜220をパターニングする第3の工程と、第1のバリア膜220をマスクとして絶縁膜200を除去する第4の工程と、ウエハ14上に第2のバリア膜224を形成する第5の工程と、Cu配線206間にエアギャップ232を残しつつ絶縁膜230を形成する第6の工程と、を有する。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

電子デバイス及びその製造方法

【課題】高性能及び高機能で、高周波特性に優れ、コストダウンに有効な絶縁構造を持つ電子デバイス及びその製造方法を提供する。

【解決手段】半導体基板1は、その厚み方向に伸びる縦孔30を有している。絶縁物充填層3は、縦孔30内にその内周面を覆うように充填してなる環状層である。縦導体2は、絶縁物充填層3によって囲まれた領域20内に充填された凝固金属体でなる。絶縁充填層3は、有機絶縁物又はガラスを主成分とする無機絶縁物と、ナノコンポジット構造のセラミックとを有する層である。ナノコンポジット構造のセラミックは、常温比抵抗が1014Ω・cmを超え、比誘電率が4〜9の範囲にある。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】生産性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、積層構造体MLと、選択ゲート電極SGと、半導体ピラーSPと、記憶層48と、内側絶縁膜42と、外側絶縁膜43と、選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、電極間絶縁膜62と、を有する。選択ゲート電極は、積層構造体と積層された複数の選択ゲート導電膜71と、選択ゲート導電膜間絶縁膜72と、を有する。半導体ピラーは、積層構造体及び選択ゲート電極を第1方向に貫通する。記憶層は、電極膜と半導体ピラーとの間に、内側絶縁膜は、記憶層と半導体ピラーとの間に、外側絶縁膜は、記憶層と電極膜との間に、選択ゲート絶縁膜は、選択ゲート導電膜と半導体ピラーとの間に設けられる。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

回路基板及びその製造方法

【課題】配線抵抗が低く配線間の絶縁性の高い回路基板及びその製造方法を提供する。

【解決手段】基板上に、Cuを含む導電性材料の配線構造体を形成し、配線構造体の表面に、Cu−N結合を有する絶縁性の拡散防止膜を形成した後、拡散防止膜が形成された配線構造体を覆うように、絶縁膜を形成する。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

低k誘電体と導電材料との接着改善

【課題】銅ダマシン配線上への誘電体層の形成において、導電材料と誘電体層間の密着性を向上する半導体装置の製造方法を提供する。

【解決手段】オルガノシロキサンからなる第2誘電体層118に、TaNからなる金属バリア層124とCuからなる導電性金属特徴部126を形成する。平坦化後アンモニアプラズマ処理還元により表面の酸化物を除去する。連続して真空を破壊せずに、トリメチルシランからなる有機ケイ素化合物を導入し、プラズマプロセスによりSiCN膜130を形成し、さらに連続してSiC膜132を堆積する。酸化物の除去から誘電体層の形成までインサイチュで行うことが可能である。

(もっと読む)

半導体デバイス及びマスク設計方法

【課題】アクティブフィーチャの容量カップリングを低減する。

【解決手段】本発明は、研磨ダミーフィーチャパターンの無差別な配置ではなく、研磨ダミーフィーチャパターンの選択的な配置を使用する。トポグラフィ変化の低周波数(数百ミクロン以上)及び高周波数(10ミクロン以下)の両方が検討された。研磨ダミーフィーチャパターンは半導体デバイス及び半導体デバイスの作製に使用される研磨条件に特に適合されている。集積回路をデザインする場合にはアクティブフィーチャの研磨効果が予測可能である。研磨ダミーフィーチャパターンが例図とに配置された後、局部的な(デバイスの全てではなく一部)レベルにおいて、及びさらに広域的なレベル(全デバイス、デバイスとは、レチクルフィールド、或いはさらにはウェハ全体に対応する)平坦性が検査される。

(もっと読む)

21 - 40 / 303

[ Back to top ]