Fターム[5J055EZ00]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211)

Fターム[5J055EZ00]の下位に属するFターム

積分回路、CR時定数回路 (122)

微分回路 (16)

定電流素子、定電流回路 (454)

カレントミラー回路 (261)

1、2石の増幅回路 (960)

オペアンプ、演算増幅器 (260)

比較器(デジタル、アナログ) (565)

シュミット回路 (46)

ゲート、トランスファーゲート (670)

マルチプレクサ (275)

フィルター、濾波器、共振回路 (166)

整流回路 (20)

クランプ、リミッタ (97)

スナバ回路 (31)

ブートストラップ回路 (94)

プリチャージ (38)

レベルシフト (258)

整合、インピーダンス変換 (20)

プルアップ、プルダウン (113)

変調、復調器、PWM (119)

A/D、D/A変換器 (155)

論理素子(INVは除く) (1,593)

CPU (177)

特定のIC、LSI (6)

機械要素 (139)

遅延素子、回路、デレイライン (226)

電源回路、特徴がある定電圧回路 (631)

2種以上のクロックを用いるもの (1)

機能的なダイオード (205)

表示装置、LED (102)

Fターム[5J055EZ00]に分類される特許

61 - 80 / 391

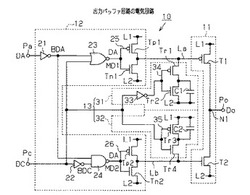

出力バッファ回路

【課題】ハイ・インピーダンスにする際に発生する電源ノイズを低減させる出力バッファ回路を提供する。

【解決手段】出力バッファ回路10は、データ信号DA及び制御信号DCに基づいて、PMOSトランジスタT1をオンからオフさせNMOSトランジスタT2をオフからオンさせて出力端子Poを第1状態に、PMOSトランジスタT1をオフからオンさせNMOSトランジスタT2をオンからオフさせて出力端子Poを第2状態に、又、両トランジスタT1,T2をオフさせて出力端子Poをハイ・インピーダンスとなる。そして、オフ時間制御回路部13によって、第1状態又は第2状態からハイ・インピーダンスにする制御信号が入力された時、オンからオフさせるためにPMOSトランジスタT1又はNMOSトランジスタT2のゲートに供給される信号の立ち上がり波形又は立ち下がり波形を緩やかにする

(もっと読む)

半導体集積回路装置およびその試験方法

【課題】初期不良を効率的に排除する。

【解決手段】端子11a、11mと、端子11a、11m間を直列形態で接続する第1〜第2n+1(nは1以上の整数)の抵抗素子(抵抗素子群12)と、第1の抵抗素子の一端が接続される端子11aを第0のノードとし、第2n+1の抵抗素子の他端が接続される端子11mを第2n+1のノードとし、第i(i=1〜2nの整数)の抵抗素子の他端および第i+1の抵抗素子の一端の接続点を第iのノードとし、第0〜第2n+1のノードのいずれか一点を選択して出力可能とする選択回路14と、第2k(k=0〜nの整数)のノードを全て短絡可能とするスイッチ群15aと、第2k+1のノードを全て短絡可能とする第2のスイッチ群15bと、を備える。第2kのノード、第2k+1のノードを全て短絡状態とし、その後、端子11a、11m間に所定の電圧を一時的に印加する。

(もっと読む)

パルス幅変調回路および電圧帰還型D級増幅回路

【課題】出力負荷を駆動する電圧帰還型D級増幅回路の周波数特性を改善する。

【解決手段】入力信号のPWM変調を行なう比較回路(26A,26B)に、PWMキャリアとなる三角波(TOSC)を与える三角波信号発生器(30)に対し、三角波の勾配を補正する三角波補正回路(32)を設ける。三角波(TOSC)のスルーレート(勾配)を出力回路駆動用指令値(COMPOUTP,COMPOUTM)のデューティが50%近傍となる領域において小さくする。

(もっと読む)

PWM制御ソレノイド駆動装置および半導体集積回路装置

【課題】 PWM制御によってソレノイドを駆動する駆動装置において、設定により、ソレノイドを駆動する電流のディザ信号が歪むことによって駆動電流の中心値ずれが発生するのを抑制したPWM制御ソレノイド駆動装置あるいはそれを共通の半導体基板上に一体形成して成る半導体集積回路装置を提供する。

【解決手段】 スイッチ用MOS300と、ソレノイド600と、電流モニタ用抵抗700と、フライバックダイオード800とを含んで構成される駆動対象のソレノイド装置を駆動するソレノイド駆動装置として、基準鋸波発生器100と、比較器200と、ソレノイド電流制御信号発生回路400と、PI制御回路500と、信号振幅調整回路900と、ディザ信号歪み検出回路1000とを備えたPWM制御によるソレノイド駆動装置を構成する。

(もっと読む)

クロック切替回路

【課題】従来のクロック切替回路では、高速なクロック信号の切替に対応することができない問題があった。

【解決手段】本発明のクロック切替回路は、基本クロックCLKを分周した分周クロックC101〜C10nを生成する分周回路10と、クロック選択信号CNTに応じて出力選択信号SELを出力する出力選択信号生成回路20と、出力選択信号SELに応じて出力するクロックを切り替える出力選択回路30と、を有し、分周回路10は、分周クロックC101〜C10nの1周期の開始からの基本クロックCLKのクロック数を示す分周カウント値S101〜S10nを出力し、出力選択信号生成回路20は、分周カウント値S101〜S10nのうち現選択クロックに対応した分周カウント値に基づき切替前後の分周クロックの開始タイミングが一致するタイミングで出力選択信号SELの値を切り替える。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】電源電圧を変更することなく、広い温度範囲でリーク電流を抑えて動作する半導体装置を提供する。

【解決手段】しきい値電圧が第1電圧である第1トランジスタを含む高VT部7と、しきい値電圧が第1電圧よりも低い第2電圧である第2トランジスタを含む低VT部8と、温度を測定し、温度が所定の温度より高い高温状態であるか、温度が所定の温度よりも低い低温状態であるかを判定し、高温状態を示す信号又は低温状態を示す信号を出力する温度検知部6と、高温状態を示す信号、又は低温状態を示す信号を受信し、高温状態を示す信号に基づいて高VT部7を動作させ、低温状態を示す信号に基づいて低VT部8を動作させる制御を行う制御部9とを具備する。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

スイッチング制御回路

【課題】同時スイッチングノイズを低減するスイッチング制御回路を提供する。

【解決手段】本発明のスイッチング制御回路は、入力端子1、出力端子2及びスイッチング素子を有する出力回路10と、出力回路10のスイッチング素子の制御端子に接続され、出力回路10の出力信号が変化する期間において、入力信号を制御する第1の回路20と、第1の回路20の制御端子に接続され、出力回路10の出力信号が変化する期間において、第1の回路20に流れる電流を制御する制御信号を生成する第2の回路30と、を備えている。

(もっと読む)

パルス発生回路

【課題】電源オフした直後に電源を再投入しても正常にパルス生成動作を再開できるようにすること。

【解決手段】このパルス発生回路は、第1のDフリップフロップ回路11のセット端子及びリセット端子をそれぞれコンデンサC11,C12を介してグラウンド又は電源に接続し、第1のDフリップフロップ回路11のQ出力端子とセット端子間及びQバー出力端子とリセット端子間にそれぞれ第1の抵抗R11,R12を接続し、前記セット端子、リセット端子、Q出力端子又はQバー出力端子のうちのいずれかの端子とグラウンド間に第2の抵抗RGを接続している。また、第1のDフリップフロップ回路11のQ出力端子を第2のDフリップフロップ回路20のクロック端子に接続し、第2のDフリップフロップ回路20のデータ端子及びセット端子を電源に接続し、第2のDフリップフロップ回路20のQバー出力端子とリセット端子間に第3の抵抗R2を接続した。

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

高周波電源装置

【課題】安定したパルス高周波電力を供給することができる高周波電源装置1を提供する。

【解決手段】高周波電源装置1は、パルス高周波電力の出力電圧を検出して包絡線検波を行い、その検波信号をサンプルホールド部6によりサンプリングし、サンプリング電圧Vsを高周波電力生成部3にフィードバックしてパルス高周波電力Poutの制御を行う。サンプルホールド部6は、サンプルホールド信号のオン期間中、検波信号Paをサンプリング電圧Vsとして出力し、サンプルホールド信号のオフ期間中、サンプルホールド信号がオンからオフへ切り替るタイミングの検波信号Paの電圧レベルをホールドして、サンプリング電圧Vsとして出力する。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、クロスオーバー電圧の変動幅が増大するという問題があった。

【解決手段】本発明にかかる半導体集積回路は、差動入力の一方に基づいて第1及び第2の信号を生成するプリドライバ4cと、差動入力の他方に基づいて第3及び第4の信号を生成するプリドライバ回路4dと、VDDとVSSとの間に設けられ、第1の信号に基づいて制御されるMN4と、第2の信号に基づいて制御されるMP4と、からなる出力回路5aと、VDDとVSSとの間に設けられ、第3の信号に基づいて制御されるMN8と、第4の信号に基づいて制御されるMP8と、からなる出力回路5bと、VDDに応じた第1の制御信号を生成する制御信号生成回路6と、を備える。さらに、プリドライバ4cは、第1の制御信号に基づいて第1の信号を制御し、第2のプリドライバ4dは、第1の制御信号に基づいて第3の信号を制御する。

(もっと読む)

CV変換回路

【課題】超小型に形成されて容量値および容量変化が非常に微小なセンサ容量素子の容量変化を、高効率かつ高精度に電圧変化に変換させて検出する。

【解決手段】センサ容量素子Csの静電容量を、スイッチドキャパシタ型負帰還回路を有する演算増幅器11によって電圧変換するCV変換回路であって、その負帰還回路は、演算増幅器11の出力端子と反転入力端子間に直列に接続された第1,第2の容量素子C1,C2と、その容量素子C1,C2の中間接続点bに一方の電極端子が接続された第3の容量素子C3と、この容量素子C3の他方の電極端子を演算増幅器11の出力端子または基準電位に接続する切り換えスイッチ回路Sw1,Sw2を有し、このスイッチ回路の接続位置によって等価的な帰還容量値を可変設定する。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

ドループ補正ピークホールド回路

【課題】ピークホールド回路において、ドループを抑制してピーク電圧を長時間保持できるドループ補正ピークホールド回路を提供すること。

【解決手段】ピークホールド回路のホールドコンデンサC1は、一端をダイオードD1のカソードに接続し、他端をドループ補正回路20に接続してある。ドループ補正回路20は、ホールドコンデンサC2の保持電圧を、増幅回路A3において極性を反転してホールドコンデンサC1に印加する。即ちドループ補正回路20は、ホールドコンデンサC1にその保持電圧と逆極性のドループ補正電圧を印加する。ドループ補正電圧の印加によりホールドコンデンサC1のドループを長時間抑制できる。

(もっと読む)

高周波スイッチ及び受信回路

【課題】簡単な構成でセルフミキシング信号の発生を低減する高周波スイッチ及びこれを用いた受信回路を提供する。

【解決手段】ゲート端子が入力端子側に接続され、ドレイン端子が出力端子側に接続され、ソースが接地された電界効果トランジスタと、前記電界効果トランジスタのゲート端子側に接続されるゲートバイアス電圧調整手段とドレイン端子側に接続されるドレインバイアス電圧調整手段の少なくともいずれか一方を備え、前記ゲート端子と入力端子との間及び前記ドレイン端子と出力端子との間の少なくともいずれか一方に整合回路を備え、導通状態における反射特性と前記遮断状態における反射特性とが略等しくなるように、スイッチを構成している。

(もっと読む)

表示装置駆動回路

【課題】チップサイズを大きくすることなく、出力アンプ毎に最適な駆動能力を設定することができる表示装置駆動回路を提供することである。

【解決手段】本発明にかかる表示装置駆動回路は、異なる基準電位を有する少なくとも2つのバイアス配線11a、11bと、階調信号14aに基づきバイアス配線11a、11bのうちの一つを選択するセレクタ12aと、セレクタ12aにより選択されたバイアス配線の基準電位が供給されると共に、表示信号を生成し当該表示信号をデータ線に供給する出力アンプ13aと、を有する。

(もっと読む)

導通切替回路、導通切替回路ブロック、及び導通切替回路の動作方法

【課題】リアクタンスによる挿入損失を生じさせずに、高周波信号の漏洩を防止できる、導通切替回路、導通切替回路の動作方法、及び導通切替回路ブロックを提供する。

【解決手段】第1MOSFETと、第1ノードを介して前記第1MOSFETと接続された第2MOSFETと、前記第1ノードに接続された第1制御端子とを具備する。前記第1MOSFETと前記第2MOSFETとは、オン時に前記第1ノードを介して電気的に直列に接続されるように設けられる。前記第1制御端子は、前記第1MOSトランジスタと前記第2MOSFETとがオフ状態であるときに、前記第1ノードに対して、前記第1MOSFET及び前記第2MOSFETに生じる容量が少なくなるような電圧を印加する。

(もっと読む)

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

出力回路およびモータ駆動装置

【課題】パワートランジスタの誤動作を防止する。

【解決手段】パワートランジスタM1は、出力端子POUTと電源端子PVCCの間に設けられる。プリドライバ10は、電源端子PVDDと第2端子P2の間に直列に接続され、制御信号S1に応じて相補的にオン、オフが制御されるハイサイドトランジスタM2およびローサイドトランジスタM3を含み、2つのトランジスタの接続点の電位を、パワートランジスタM1の制御端子に出力する。定電圧回路20は、第2端子P2を所定の電圧VL(=Vref)に安定化させる。定電圧回路20の出力トランジスタM4は、第2端子P2と接地端子PGNDの間に設けられる。差動アンプ24は、第2端子P2の電位VLが所定の目標値Vrefに近づくように、出力トランジスタM4の制御端子の電圧Vg4を調節する。フィードバックキャパシタC1は、第2端子P2と出力トランジスタM4の制御端子の間に設けられる。

(もっと読む)

61 - 80 / 391

[ Back to top ]