Fターム[5J056CC00]の内容

論理回路 (30,215) | 構成要素(回路) (5,601)

Fターム[5J056CC00]の下位に属するFターム

定電流源 (480)

ミラー回路、カレントミラー回路 (296)

電源回路 (715)

遅延回路 (349)

フィルタ回路 (82)

積分回路 (27)

微分回路 (11)

比較器 (432)

オペアンプ (171)

シュミット回路 (34)

クランプ回路 (62)

リミッタ回路 (17)

双安定回路(フリップフロップ、ラッチ) (577)

単安定回路 (17)

非安定回路、発振回路 (126)

カウンタ (157)

シフトレジスタ (106)

プリチャージ回路 (44)

ディスチャージ回路 (10)

レベルシフト回路 (574)

ダーリントン (1)

エミッタホロワ (6)

オープンコレクタ (3)

ソースホロワ (26)

オープンドレイン (10)

ドット論理、ワイヤード論理 (8)

表示回路 (13)

昇圧回路(ブートストラップ) (120)

ポンプ回路 (36)

Fターム[5J056CC00]に分類される特許

1,081 - 1,091 / 1,091

長いオンチップバスの動作

テクノロジの縮尺度のために、オンチップ相互接続は幅が狭くなってきており、このような相互接続の高さは、幅に線形に比例しない。これにより、隣接配線とのカップリング容量が増加し、クロストークが高くなる。それはまた、配線の受信側におけるRC応答の不十分さに起因する性能の不十分さに繋がり、非常にノイズの多い環境では、故障の原因になることさえある。受信機スイッチング閾値がバスラインにおいて検出されたノイズに応じて調整される適応閾値構成が提案される。これらのノイズレベルは、フロントエンド処理(トランジスタ性能)とバックエンド処理(金属抵抗、容量、幅及びスペーシング)の両方に依存する。従って、回路は、プロセス変動を自動的に補償する。  (もっと読む)

(もっと読む)

センタタップ終端回路及びセンタタップ終端回路を有するプリント配線板

【課題】差動信号伝送線路の終端回路において、センタタップ終端回路を形成することにより差動インピーダンスが変動するため、コモンモード電流成分が発生し放射ノイズが発生する。

【解決手段】差動信号伝送線路の往路伝送線路と復路伝送線路の間に、同じ抵抗値の2つの抵抗を直列に接続し、2つの抵抗の接続部とプリント配線板のGNDとの間に、キャパシタを接続したセンタタップ終端回路において、往路伝送線路と復路伝送線路を一定の間隔で配線し、抵抗とキャパシタは往路伝送線路と復路伝送線路の外側に配置し、接続部は往路伝送線路と復路伝送線路と立体的に交差するように形成する。これにより、差動信号のtr/tf特性をほぼ一致させ、スキューの発生も防止することができる。また、差動インピーダンスの不整合がなく、高品質の信号波形を保つ事ができるため、放射ノイズの発生を大幅に抑制することができる。

(もっと読む)

差動信号伝送線路の終端回路

【課題】差動信号伝送線路の終端回路において、ディファレンシャルモード信号及びコモンモード信号に対して、整合センタータップ終端回路を実現しする。また、センタータップ終端回路を単一部品で構成する事により、実装面積を縮小するとともに、部品・実装コストの削減も達成する。

【解決手段】差動信号伝送線路における2つの線路の差動インピーダンスの約1/2である抵抗値を有する第1、第2の抵抗素子を、受信側ICの入力端に直列にして接続し、第1、第2の抵抗素子の中点とプリント配線板のGNDとの間に、第3の抵抗素子と第1のコンデンサ素子を直列に接続する。また、これらの抵抗素子とコンデンサ素子からなるセンタータップ終端回路部品をチップ抵抗部品に、電極、抵抗皮膜、誘電体皮膜を層状に重ね合わせる事により形成して、単一部品で実現する。

(もっと読む)

電子回路装置、電子デバイスパッケージおよび伝送線路の終端方法

【課題】本発明は、高速動作周波数の信号伝送に対して、終端回路の反射ノイズ防止機能を十分に発揮できる電子回路装置を提供することを課題とする。

【解決手段】信号入力バッファ17の信号入力回路が、基板やケーブルなどの伝送線路部の配線13上で終端される構成ではなく、出力側電子デバイス部に設けられた信号出力バッファ11が、終端されずに、基板やケーブルなどの伝送線路部の配線13を介して入力側電子デバイス部に設けられた信号入力バッファ17に直接回路接続される。更にその回路接続部から終端回路用配線16を介して、入力側電子デバイス部付近で終端抵抗15により終端される。

(もっと読む)

高速信号伝送システム

【課題】本発明は、2GHz以上の高速なLSIチップと接続され、該LSIチップと信号のやり取りをするチップ外線路に数十GHz帯ディジタル高速信号を通すことである。

【解決手段】本発明の高速信号伝送システムは、トランジスタキャリアのポンプアップ、ポンプダウンを自動的に行うデバイス構造、受信情報をフィードバックし、送信側で波形調整する遺伝的アルゴリズム回路の挿入、トランジスタから出て行く配線の伝送線路化、回路のコモン電源を排除した構成を作る。上記チップ外線路の送端または終端側の一方で基準電位を確認するため電源またはグランドへの接続を有するが、該基準電位を確認した送端または終端側の反対側の終端または送端では電源またはグランドへの接続を有さない。

(もっと読む)

集積回路のための入力/出力特徴付けチェーン

【課題】集積回路の入力又は出力を特徴付ける入力/出力特徴付けレジスタを提供すること。

【解決手段】本発明による集積回路(11)の入力/出力特徴付けレジスタ(10)は、ノーマル・データ入力(18)と、特徴付けデータ入力(20)と、ラッチ制御入力、ラッチ・データ入力(41)及びラッチ・データ出力(42)を有するデータ・ラッチ(30)とを含む。ノーマル・データ入力と特徴付けデータ入力とは、マルチプレクサ(32及び34)により、ラッチ・データ入力まで、ラッチ・データ出力と多重化される。

(もっと読む)

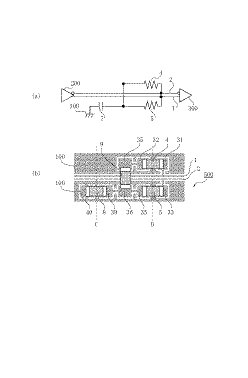

ノイズ低減高周波回路

【課題】 伝送線路の特性を問わず、常にノイズフィルタの諸元上の阻止域でノイズ除去効果を発揮させる。

【解決手段】 抵抗3および電源4からなる終端回路により伝送線路1のインピーダンス整合が図られるため、伝送線路1に電流・電圧の定在波が生じない。一般に定在波の発生は、その周波数におけるノイズフィルタのノイズ除去効果を減殺するものであるから、電流レベル・電圧レベルの変化のないフラットな特性を得ることで、伝送線路1の特性を問わず、ノイズフィルタ2の諸元上の阻止域でノイズ除去効果を発揮させることができる。

(もっと読む)

低消費電力テスト回路

【課題】 この発明は、スキャンF/Fを使用した半導体装置のテストにおいて、消費電力を低減した低消費電力テスト回路を提供することを課題とする。

【解決手段】 この発明は、スキャンF/F11,12と遅延要素14との間に、テスト動作時又はテスト動作におけるスキャン動作時にのみスキャンデータを遅延要素14に与えるゲート回路13を挿入して構成される。

(もっと読む)

半導体回路

【課題】 半導体回路において、回路動作の履歴により動作速度が変化しないようにすること、寄生バイポーラトランジスタがオンするのを防止すること、及び設計データの共通化を図ること。

【解決手段】 電界効果形トランジスタのボディーと電源とを抵抗(RBMP1,RBMN1)を介して接続する。

【効果】 本発明を用いると、切り換わり後、ボディーの電位が初期状態に復帰するので、上記課題を解決できる。

(もっと読む)

半導体集積回路装置

【課題】 入力回路の簡素化と製品管理の取り扱いを簡便にしつつ、実質的な低消費電力化及び素子の微細化に適合して安定した入出力伝達特性を実現できる入力回路を備えた半導体集積回路装置を提供する。

【解決手段】 外部端子から供給される入力信号を受ける差動増幅回路に第1と第2の動作電圧を第1と第2のスイッチMOSFETを介して供給するようにし、バイアス電圧発生回路により上記入力信号が上記第1と第2の動作電圧の中心電圧付近にあるときに上記第1と第2スイッチMOSFETをオン状態にし、その入力信号が継続的に一定期間上記第1電圧又は第2電圧にあるときには、それに対応した出力信号を形成すべく上記第1又は第2スイッチMOSFETのいずれか一方をオン状態に他方をオフ状態にする制御電圧を形成し、上記第1動作電圧と第2動作電圧に対応した第1振幅の入力信号と、上記第1動作電圧と第2動作電圧の間の所定の中間電圧に対応した第2振幅の入力信号の双方の供給を可能とする。

(もっと読む)

入力回路及び半導体集積回路装置

【課題】外部信号に応答した内部信号を生成する入力回路であって、増幅時に発生する外部信号のエッジから内部信号の立ち上がりエッジ及び立ち下がりエッジの相対的な遅延を改善する。

【解決手段】差動回路は、外部信号DQS ,DQと基準電圧Vref がそれぞれ入力される一対のNMOSトランジスタTN1,TN2を備え、外部信号DQS ,DQと基準電圧Vref に基づいて一対のNMOSトランジスタTN1,TN2にそれぞれ流れる電流に応じて、外部信号DQS ,DQに応答した内部信号dqsz,dqz を出力する。電流調整回路としてのNMOSトランジスタTN4は、外部信号DQS ,DQに対する内部信号dqsz,dqz のレベルに応答して差動回路の電流量を調整すべくオンオフ動作する。

(もっと読む)

1,081 - 1,091 / 1,091

[ Back to top ]