Fターム[5F103DD01]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出物質 (905) | 3−5族化合物 (251)

Fターム[5F103DD01]の下位に属するFターム

BN (1)

GaAs (30)

GaAsP (2)

GaAlAs (13)

GaAlAsP (2)

GaP (2)

GaInP (4)

GaInSb (4)

InP (11)

InSb (4)

InGaAsP (5)

Fターム[5F103DD01]に分類される特許

21 - 40 / 173

蒸着法における成膜条件の評価方法、および蒸着装置

【課題】蒸着法における効率的な成膜条件の評価方法と、そのための蒸着装置とを提供する。

【解決手段】真空容器50内に収められた基板200の主面の第1の領域を蒸着源60へ露出しかつ第2の領域を遮蔽するように第1のシャッター10Aを配置しながら、第1の成膜条件によって第1の領域の上に第1の薄膜が成膜される。次に、基板200の主面の第2の領域の少なくとも一部を蒸着源60へ露出しかつ第1の領域の少なくとも一部を遮蔽するように第2のシャッター10Bを配置しながら、第2の成膜条件によって第2の領域の上に第2の薄膜が成膜される。第1および第2の薄膜の特性が評価される。

(もっと読む)

原料供給装置及び成膜装置

【課題】MBE成膜装置において、フェイスアップ状態で被処理体の表面に化合物半導体よりなる薄膜を形成することができる原料供給装置を提供する。

【解決手段】化合物半導体の製造に用いる原料を供給する原料供給装置62において、鉛直方向に延びて外周面が液体を流下させることができるような表面である液体流下面90になされた原料保持体64と、原料保持体の高さ方向の途中に設けられて原料の液体である原料液体を貯留すると共に濡れ性によって原料液体を液体流下面90に沿って流下させる原料液体貯留部66と、原料保持体内に設けられて、原料液体貯留部を原料が濡れ性を発揮するように加熱すると共に原料保持体の先端部を原料液体の蒸発温度まで加熱する加熱手段68とを備える。

(もっと読む)

AlxGa1−xN結晶基板

【課題】大型で転位密度の低いAlxGa1-xN結晶基板を提供する。

【解決手段】本AlxGa1-xN結晶基板は、気相法によるAlxGa1-xN結晶(0<x≦1)の成長方法で得られたAlxGa1-xN結晶10の表面13を加工することにより得られる平坦な主面31を有するAlxGa1-xN結晶基板30であって、結晶成長の際、その雰囲気中に不純物を含めることにより、AlxGa1-xN結晶10の主成長平面11に複数のファセット12を有するピット10pが少なくとも1つ存在している状態でAlxGa1-xN結晶10を成長させることにより、AlxGa1-xN結晶10の転位を低減し、ピット10p底部から主成長平面11に対して実質的に垂直方向に伸びる線状転位集中部10rの密度が105cm-2以下であり、結晶成長後において主成長平面11の総面積に対するピット10pの開口面10sの総面積の割合が30%以上である。

(もっと読む)

III族−窒化物のGe上への形成

【課題】良好な結晶品質を有するGaN層のようなIII族−窒化物が得られる方法で形成されたIII族−窒化物/基板構造と、少なくとも1つのそのような構造を含む半導体デバイスを提供する。

【解決手段】基板1の上に、例えばGaN層5のような、III族−窒化物層の堆積または成長を行う方法であり、基板1は、少なくともGe表面3、好適には六方対称を有する。この方法は、基板1を400℃と940℃の間の窒化温度に加熱するとともに、基板1を窒化ガスの流れに露出させる工程と、続いて、100℃と940℃の間の堆積温度で、Ge表面3の上に、例えばGaN層5のようなIII族−窒化物を堆積する工程を含む。

(もっと読む)

III族窒化物半導体光素子、III族窒化物半導体光素子を形成する方法、III族窒化物半導体膜を成長する方法及びエピタキシャル基板

【課題】p型III族窒化物半導体の電気特性を向上できるIII族窒化物半導体光素子を提供する。

【解決手段】窒化ガリウム系半導体領域15及び窒化ガリウム系半導体領域19は、基板13の主面13a上に設けられる。窒化ガリウム系半導体領域19は、p型ドーパントとしてマグネシウムを含むIII族窒化物半導体膜21を有しており、III族窒化物半導体膜21は、III族構成元素としてアルミニウムを含む。III族窒化物半導体膜21の酸素濃度は、1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の酸素濃度は、1.5×1018cm−3以下の範囲にある。また、III族窒化物半導体膜21の水素濃度は1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の水素濃度は1.5×1018cm−3以下の範囲にある。

(もっと読む)

ラジカル源

【課題】高密度なラジカルを生成することが可能なラジカル源を実現すること。

【解決手段】ラジカル源は、SUSからなる供給管10と、供給管10に接続する熱分解窒化ホウ素(PBN)からなる円筒状のプラズマ生成管11を有している。プラズマ生成管11の外側には、円筒形のCCP電極13が配置されていて、CCP電極13よりも下流側には、プラズマ生成管11の外周に沿って巻かれたコイル12を有している。供給管10とプラズマ生成管11との接続部における供給管10の開口には、セラミックからなる寄生プラズマ防止管15が挿入されている。

(もっと読む)

分子線エピタキシー装置

【課題】ラジカル源によるラジカルの照射によって成膜するMBE装置において、成膜速度を向上させること。

【解決手段】MBE装置は、真空容器1と、真空容器1の内部に設けられ、基板3を保持し、基板3の回転、加熱が可能な基板ステージ2と、基板3表面に分子線(原子線)を照射する分子線セル4A〜Cと、基板3表面に窒素ラジカルを供給するラジカル源5と、を備えている。ラジカル源5は、SUSからなる供給管10と、供給管10に接続するプラズマ生成管11を有している。プラズマ生成管11の外側には、円筒形のCCP電極13が配置されていて、CCP電極13よりも下流側には、プラズマ生成管11の外周に沿って巻かれたコイル12を有している。供給管10とプラズマ生成管11との接続部における供給管10の開口には、セラミックからなる寄生プラズマ防止管15が挿入されている。

(もっと読む)

赤外LED用のエピタキシャルウエハおよび赤外LED

【課題】特性を向上できる赤外LED用のエピタキシャルウエハおよび赤外LEDを提供する。

【解決手段】赤外LED用のエピタキシャルウエハ1cは、主表面11aと、主表面11aと反対側の裏面11bとを有するAlxGa(1-x)As層(0≦x≦1)を含むAlyGa(1-y)As基板(0≦y≦1)と、AlxGa(1-x)As層の主表面11a上に形成され、かつ活性層を含むエピタキシャル層20とを備える。AlxGa(1-x)As層において、主表面11aのAlの組成比xは、裏面11bのAlの組成比xよりも低い。AlxGa(1-x)As層において、主表面11aの不純物濃度は、裏面11bの不純物濃度よりも高い。

(もっと読む)

成膜装置及び成膜方法

【課題】 坩堝の側面に原料融液が這い上がった状態で成膜を行うと、形成された薄膜の厚さの均一性が低下してしまう。

【解決手段】 チャンバ内に基板ホルダが配置されている。坩堝の内部に蒸発源が収容される。坩堝の開口部が、基板ホルダに保持された基板に向けられている。第1の加熱装置が坩堝を加熱する。測定装置が、坩堝の深さの1/2の深さよりも浅い位置の、坩堝の温度に依存する物理量を測定する。回転機構が坩堝を回転させる。制御装置が、測定装置による測定結果に基づいて、回転機構を制御する。

(もっと読む)

分子線源セル

【課題】分子線源セルを破損させることなく、かつ均一な空間強度分布を維持できるAl用分子線源セルを提供する。

【解決手段】蒸発させる原料を収容するルツボ10と、ルツボ10の側面を囲んで該ルツボ10を加熱する分子線源ヒータ部12と、を備え、ルツボ10は、上端において環状の開口部16が設けられた有底円筒状の容器と、該容器の開口部16の全周に渡って外向きに配置され、分子線源ヒータ部12の外側まで張り出したツバ11と、を有することを特徴とする分子線源セル1。

(もっと読む)

量子ドットの製造方法及び光半導体装置の製造方法

【課題】MBEによりInP基板上に等方的な形状の量子ドットを形成することのできる量子ドットの製造方法を提供する。

【解決手段】MBE法により量子ドットを形成する量子ドットの製造方法において、InP基板上にIII−V族化合物半導体をエピタキシャル成長させ下地結晶層を形成する下地結晶層形成工程と、前記下地結晶層上にIII−V族化合物半導体からなる量子ドットを形成する量子ドット形成工程と、前記量子ドット上にIII−V族化合物半導体をエピタキシャル成長させ埋込結晶層を形成する埋込結晶層形成工程と、を有し、前記下地結晶層及び前記埋込結晶層を形成する材料と、前記量子ドットを形成する材料とは異なる組成または異なる組成比の材料であって、前記量子ドットは、砒素を含む材料により形成されるものであって、前記量子ドット形成工程において、前記砒素は砒素分子線発生装置よりAs2分子を含む状態で供給されることを特徴とする量子ドットの製造方法により上記課題を解決する。

(もっと読む)

発光素子

【課題】発光効率を向上させた発光素子を提供する。

【解決手段】

本発明の発光素子は、結晶成長面を有する単結晶基板12であって、結晶成長面12は複数の凸部12aと、複数の凸部12a同士の間にそれぞれ設けられ、かつ複数の凸部12aから離隔する位置に設けられる凹部12bと、を備える単結晶基板12と、単結晶基板12上に設けられ、複数の凸部12aのうち、一対の互いに隣接する凸部12aと、当該一対の凸部12a同士の間に位置する凹部12bにおいて、凹部12bと一対の凸部12aとの間に位置する両結晶成長面から一対の凸部12a同士の間に向かって延びる複数の転位16を、一対の凸部12a同士の間で結合させた光半導体層13と、を有する。

(もっと読む)

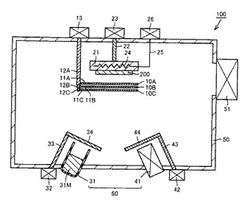

スパッタリング装置及びスパッタリング方法

【課題】基板ホルダの基板以外の領域の表面に成膜材料が付着するのを防止することができ、基板上に成膜される膜の品質及び生産性を向上させることができるスパッタリング装置を提供する

【解決手段】真空排気可能な真空容器1と、真空容器1の内部に配設され、基板8をその処理面を下方へ臨ませて保持する保持機構30、31を備えた基板ホルダ40と、基板ホルダ40の直下に基板8に対向させて配置され、放電用電力が供給されるカソード電極10と、カソード電極10の基板側に支持されたターゲット16と、を備え、基板ホルダ40は、基板以外の領域の表面温度を基板8上に成膜する成膜材料の分解または蒸発温度以上に加熱する加熱機構60、61を有する。

(もっと読む)

半導体装置の製造方法

【課題】サファイア基板上に高品質なIII族窒化物を結晶成長させ、高品質な半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】直接窒化されたサファイア基板2上のAlN層にラジカル源5から窒素ラジカル又は窒素イオンを含む気体を所定時間照射する。その後、成長させるIII族窒化物の構成元素からなるターゲット3aに窒素雰囲気中でパルスレーザ光を照射するPLD(パルスレーザ堆積)法によってIII族窒化物を結晶成長させることにより、極めて高品質なN極性結晶を得ることができる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】薄膜トランジスタ用半導体層の材料として、高い正孔移動度を示すp形半導体多結晶薄膜を、かつ、低い成膜温度でのプラスチック基板上への成膜をも行うことのできるp形半導体多結晶薄膜を、提供する。

【解決手段】ガラスまたはプラスチックまたはステンレス基板のような非結晶質または多結晶基板1上に、該基板の温度を300℃以下とし、成長膜へのガリウム(Ga)、アンチモン(Sb)、及びヒ素(As)原子のそれぞれの供給量JGa,JSb,及びJAsを、JSb<JGa<JAs+JSbを満たすような値として、Ga,Sb,及びAs原子を同時供給して真空蒸着により成膜してなる、Sb組成yが0.5<y<1を満たすp形GaSbyAs1-y多結晶薄膜6を形成する製造方法による。

(もっと読む)

半導体エピタキシャルウェハの製造方法、半導体エピタキシャルウェハ及び半導体素子

【課題】MBE法又はMOCVD法により半導体基板上に半導体薄膜をエピタキシャル成長させる際に、半導体薄膜の特性を変えることなく、残留キャリアを低濃度に制御する技術を提供する。

【解決手段】半導体基板上に半導体薄膜をエピタキシャル成長させてなる半導体エピタキシャルウェハの製造方法において、半導体薄膜をエピタキシャル成長させる際、同時にアルミニウム(Al)をドープする。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

量子ドット構造製造方法および量子ドット構造

【課題】 従来よりも発光波長が広い波長領域で均一に分布している量子ドット構造を製造する方法を提供する。

【解決手段】本発明では、量子ドット構造を以下の手順で製造する。

まず、基板11を用意する。次に、基板11上に、量子ドット13を設ける。次に、量子ドット13よりも低く、かつ表面拡散が抑制されるように基板11上に薄膜14を堆積する。

最後に、量子ドット13のうち、薄膜14から露出した部分を除去する。

(もっと読む)

III族窒化物半導体積層構造体

【課題】高度の結晶性を有し、特に直径100mm以上の大型基板を用いる場合でも全面均一に平坦なAlN結晶膜シード層を用いることにより、結晶性の良いGaN系薄膜を得、信頼性の高い高輝度のLED素子等を得る。

【解決手段】サファイア基板上にシード層としてスパッター法で堆積されたAlN結晶膜を有し、該シード層上にIII族窒化物半導体からなる、n型半導体層、発光層およびp型半導体層を積層してなるIII族窒化物半導体積層構造体において、該シード層のAlN結晶膜中の酸素含有量が0.1原子%以上5原子%以下であり、AlN結晶膜は結晶粒界の間隔が200nm以上であり、かつ最終p型半導体層であるp−コンタクト層のロッキングカーブ半値幅が(0002)面と(10−10)面でそれぞれ60arcsec以下および250arcsec以下であることを特徴とするIII族窒化物半導体積層構造体。

(もっと読む)

半導体素子の製造方法

【課題】広い範囲で制御された組成比を有し、結晶性が優れる化合物半導体の膜を用いた半導体素子を製造する方法を提供する。

【解決手段】基板上にn型半導体およびp型半導体を含むように積層して構成された半導体素子の製造方法であって、異なるIII族元素による少なくとも2つのターゲット(第1ターゲット21および第2ターゲット22)を、V族元素を含むガスによりスパッタリングして、基板110上にIII−V族の化合物半導体の膜を形成する工程を含む。

(もっと読む)

21 - 40 / 173

[ Back to top ]