Fターム[5F140BG11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762) | ゲート側壁材料 (3,458)

Fターム[5F140BG11]の下位に属するFターム

SiO (1,611)

PSG、BSG、BPSG (16)

SiN (1,528)

多結晶Si (32)

高融点金属珪化物(高融点金属を含む) (10)

空隙 (15)

Fターム[5F140BG11]に分類される特許

41 - 60 / 246

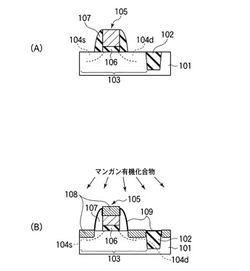

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISトランジスタとPMISトランジスタの閾値電圧を同時に低減できる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板10に形成された第1の活性領域10a上に高誘電体を含む第1のゲート絶縁膜17aと、金属材料を含む第1のゲート電極18aとを形成し、基板10に形成された第2の活性領域10b上に高誘電体を含む第2のゲート絶縁膜17bと、金属材料を含む第2のゲート電極18bとを形成する工程と、第1のゲート絶縁膜17aの端部と第2のゲート絶縁膜17bの端部とに負の固定電荷を導入する工程と、第1のゲート絶縁膜17aの端部を除去する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタを有する半導体装置において、p型のエクステンション拡散層の浅接合化を進めた場合でも、p型のエクステンション拡散層が高抵抗化されることを抑制する。

【解決手段】半導体装置は、半導体基板1に形成されたp型MISトランジスタpTrを備えた半導体装置である。p型MISトランジスタpTrは、第1の活性領域1a上に形成された第1のゲート絶縁膜2aと、第1のゲート絶縁膜2a上に形成された第1のゲート電極3aと、第1の活性領域1aにおける第1のゲート電極3aの側方下の領域に形成されたp型のエクステンション拡散層5aと、第1のゲート電極3aの側面上に形成された第1のサイドウォールスペーサ11Aとを備えている。第1のサイドウォールスペーサ11Aは、負の電荷が帯電した帯電サイドウォール6aと、帯電サイドウォール6aの上に形成された第1のサイドウォール10Aとを有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

半導体装置

【課題】メタル電極/high−kゲート絶縁膜からなるゲート構造において、半導体特性や信頼性の劣化をおこさせることなく、サイドウォールを形成したゲート構造を有する半導体装置の提供。

【解決手段】半導体基板1上に設けられた、high−k誘電体材料からなるゲート絶縁膜2と、ゲート絶縁膜2の上に設けられたメタル電極3と、メタル電極3の側壁を覆い、ゲート絶縁膜2を挟んで半導体基板1と対向配置された酸化防止膜4と、ゲート絶縁膜2と酸化防止膜4とを覆うように、半導体基板上に設けられたサイドウォール5とを含むゲート構造。

(もっと読む)

MISトランジスタ

【課題】ゲート電極とソース/ドレイン電極間で電気的短絡を起こし難いMISトランジスタを得る。

【解決手段】サイドウォール15を二重構造とする。バッファ層13は窒化酸化シリコンで形成され、バッファ層13の上に窒化シリコン層14が形成される。このサイドウォール15をマスクとしてシリサイド膜10を形成する。バッファ層13は窒化酸化シリコンのみならず、酸化シリコンで形成されてもよい。シリサイド膜はコバルトシリサイドでも、ニッケルシリサイドでもよい。窒化シリコン層14はバッファ層13よりも大きい応力を持つ。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

複数のトランジスタゲートの形成方法、および少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートの形成方法

少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートを形成する方法は、異なる幅を有する基板上に第一および第二のトランジスタゲートを形成するステップを含み、第一の幅は第二の幅よりも狭い。材料は、第一および第二のゲート上を含む基板上に堆積される。エッチングチャンバー内で、材料は、第一および第二のゲートの双方の上からエッチングされ、第一のゲートの導電性材料を露出し、第二のゲート上に支持された材料の厚さを減少させ、材料によって被覆された第二のゲートをそのまま残す。エッチング後に、エッチングチャンバー内のそのままの位置で、基板は少なくとも300℃の基板温度で金属を含むプラズマに対して暴露され、第二のゲートの仕事関数と比較して、第一のゲートの仕事関数を改変するために、第一のゲートへと金属を拡散させる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属ゲート電極表面を低温で金属絶縁膜に変え、デバイスの、すなわち、回路・システムの信頼性を向上するデバイス構造、および、その製作方法を提供することを目的とする。

【解決手段】 本発明の半導体装置は、MOSデバイスのゲート電極を金属を用いて形成し、その側壁を金属絶縁膜に改質し、デバイスの信頼性を向上したことを特徴とする。また、良質な金属絶縁膜を、低温で形成したことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程においてストレッサー膜などから発生する水素によるp型MOSトランジスタの駆動力低下を防止する。

【解決手段】半導体装置は、n型活性領域13B上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16Bと、ゲート絶縁膜15及びゲート電極16Bの側面に形成された内側サイドウォール17及び外側サイドウォール20Bと、p型ソースドレイン領域21Bと、内側サイドウォール17の側面及び外側サイドウォール20Bの側面における少なくとも底部に形成され、水素に対してバリア性を有する絶縁性の水素バリア膜23とを備える。

(もっと読む)

41 - 60 / 246

[ Back to top ]