Fターム[5F033JJ00]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060)

Fターム[5F033JJ00]の下位に属するFターム

コンタクト層なし、上層配線と一体形成 (1,607)

半導体(基板を除く) (666)

金属及びその合金(シリサイドを除く) (14,566)

シリサイド (585)

化合物 (4,106)

透光性導電膜材料 (308)

超伝導材料 (3)

Fターム[5F033JJ00]に分類される特許

81 - 100 / 219

半導体素子の金属構造物再形成方法

【課題】コンタクトプラグ、及び金属配線のような金属構造物に欠陥が発生して再形成工程を処理する場合、コンタクトホールが過度に露出されてホールが大きくなる現象を防止できる金属構造物の再形成方法を提供する。

【解決手段】本発明に従う金属構造物の再形成方法は、コンタクトプラグを含む絶縁層の上に形成された第1金属層、第1金属層の上に形成された金属配線層、金属配線層上に形成された第2金属層を含む金属構造物の再形成方法に関するものであって、第1ウェットエッチング工程を処理して金属配線層の下を除外した第1金属層及び第2金属層を除去するステップと、第2ウェットエッチング工程を処理して金属配線層を除去するステップと、第1平坦化工程を処理して残存した第1金属層及び絶縁層の表面を平坦化するステップと、を含む。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置

【課題】溶剤乾燥や熱硬化のための熱処理工程を用いずに形成した欠陥の少ない絶縁層を有する薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置を提供すること。

【解決手段】バンプ107と、バンプ107により貫通される層間絶縁層105とを含む薄膜トランジスタにおいて、バンプ107がフッ素化合物を含み、層間絶縁層105がフィルム状ホットメルト接着剤の加熱圧着により形成され、バンプがフッ素化合物を含み、フッ素含有量が、0.01wt%以上5wt%以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

フィールド酸化物上で終端する見かけの金属接点線を使用してリバースエンジニアリングに対して保護された集積回路及びこれを製造するための方法

【課題】リバースエンジニアリングに対して保護された集積回路及びこれを製造する方法の提供。

【解決手段】半導体基板の接点領域を限定する開口を有する前記半導体基板上に配置されたフィールド酸化物層4と、前記接点領域内に位置する前記フィールド酸化物の部分の上に配置されたメタルプラグ接点7と、前記メタルプラグ接点に接続された金属10とを備える。前記メタルプラグ接点が、前記フィールド酸化物層の前記部分と接触しており、そして、前記フィールド酸化物層の前記部分は、前記メタルプラグ接点を前記接点領域から絶縁していることを特徴とする半導体デバイス。

(もっと読む)

ウェハの金属材料埋込装置及びウェハの金属材料埋込方法

【課題】 容易に貫通穴を埋めることができ、環境負荷を小さくする。

【解決手段】 テーパ状の貫通穴を有するウェハの貫通穴の開口の径が小さい側の主面を把持し、貫通穴の開口の径が大きい側から、貫通穴に球状の金属材料を埋め込むウェハの金属材料埋込装置であって、ウェハの表面を吸引把持する第一の吸引部と、ウェハの貫通穴から金属材料を吸引する第二の吸引部とを有する把持本体部と、第一の吸引部と第二の吸引部とに配管を介して接続される吸引手段と、配管を流れる流体の流量と圧力とを検出する検出手段と、金属材料が吸引されて貫通穴を塞ぐことで変化した流量と圧力の値が所定の値となっているか否かを判定する判定手段と、判定手段によって値が所定の値であると判定された場合に把持本体部で吸引している前記ウェハからはみ出て入る金属材料を所定の加圧平面に押し当てる加圧手段と、を備えて構成される。

(もっと読む)

ウェハの金属材料埋込装置及びウェハの金属材料埋込方法

【課題】 容易に貫通穴を埋めることができ、環境負荷を小さくする。

【解決手段】 貫通穴が設けられたウェハの貫通穴の開口の径が小さい側の主面を把持し、前記貫通穴の開口の径が大きい側から貫通穴に金属材料を埋め込むウェハの金属材料埋込装置であって、枠状に形成される第一の吸引部と、貫通穴から金属材料を吸引し第一の吸引部に嵌め込まれる第二の吸引部とを有する把持本体部と、第一の吸引部に沿って形成され、流路と吸引穴と第三の貫通孔とが形成されたアダプター部と、吸引穴に接続される吸引手段と、吸引配管の流量と圧力とを検出する検出手段と、金属材料が吸引されて変化した流量と圧力の値が所定の値となっているか否かを判定する判定手段と、所定の値であると判定された場合に把持本体部で吸引しているウェハからはみ出て入る金属材料を所定の加圧平面に押し当てる加圧手段と、第三の貫通孔接続される吐出手段と、を備えて構成される。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

集積回路装置及びその製造方法

【課題】絶縁体上にもグラファイト層を容易に形成することができる集積回路装置及びその製造方法を提供する。

【解決手段】絶縁基板1上に触媒層2を形成し、その上にサポート層3を形成しておく。触媒層2としてCo層を形成し、サポート層としてTiN層を形成する。これらは、例えばスパッタリング法により形成する。次いで、アセチレンを含む原料ガスを用いて熱CVD処理を行う。この結果、触媒層2が絶縁基板1及びサポート層3に挟み込まれているが、カーボン原料はサポート層3を透過して触媒層2まで到達するので、グラファイト11が絶縁基板1と触媒層2との間に成長する。

(もっと読む)

電子又は電気機械部品及びナノ素子用の基板

本発明は、少なくとも一つの電子又は電気機械部品(708)及び一つ以上のナノ素子を支持するための基板であって、ベース支持部(301)と、触媒システム(302)と、障壁層(303)と、単結晶Si、Ge又はこれらの物質の混合物製の電子又は電気機械部品を収容するための層(304)とを備えた基板に関する。触媒システム(302)は、電子又は電気機械部品を収容することができる層(304)に接触することなく、ベース支持部(301)を覆い、障壁層(303)は触媒システム(302)と電子又は電気機械部品を収容することができる層(304)との間に挟まれている。障壁層(303)はベース支持部(301)と接触しない。  (もっと読む)

(もっと読む)

スルホールビアのための炭素ベース材質を備えた半導体デバイス

【解決手段】

半導体デバイスにおいて、デバイスの基板を通って延びるスルホールビアが炭素含有材質に基いて形成されてよく、それにより高温プロセスに対する優れた適合性がもたらされる一方で、ドープされた半導体材質等と比較して優れた電気的な性能ももたらされる。従って幾つかの例示的な実施形態では、スルホールビアは臨界的な回路要素を形成するために用いられる任意のプロセスステップに先立ち形成されてよく、それにより対応する半導体デバイスのデバイスレベルに対するスルホールビア構造の任意の干渉を実質的に回避することができる。その結果、高度に効果的な三次元集積化スキームを実現することができる。

(もっと読む)

有機電界発光表示装置の配線修理構造及びその修理方法

【課題】配線間のショート欠陥を容易に修理できるようにした有機電界発光表示装置の配線修理構造及びその修理方法を提供すること。

【解決手段】第1配線20及び第2配線40の間で発生したショート欠陥を修理する有機電界発光表示装置の配線修理構造において、第1配線20とのショート欠陥部分が切断されて切断された部分が残りの部分と断絶された第2配線40と、第2配線40と隣接するように配置され、ショート欠陥部分と隣接した一領域が切断されて切断された部分が残りの部分と断絶された第3配線50と、第2配線40が第3配線50の切断された部分を通じて電気的な連結状態を維持するように第2配線40の残りの部分と第3配線50の切断された部分を電気的に連結する第1リペアパターンRP1と、を備える。

(もっと読む)

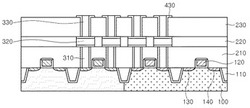

TFTアレイ基板の製造方法

【課題】簡単な工程で画素電極とコンタクトホールとを形成するTFTアレイ基板の製造方法を提供する。

【解決手段】絶縁膜を成膜する工程と、絶縁膜の上に導電膜を成膜する工程と、導電膜をパターニングして開口が設けられた画素電極を形成する工程と、開口が設けられた画素電極をエッチングマスクとしてエッチング法により絶縁膜に開口と連通するコンタクトホールを形成する工程と、を有することを特徴とするTFTアレイ基板の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】不純物イオン注入時に、実効注入ドーズ量の場所によるばらつきが生じるのを防ぐ。

【解決手段】レジスト膜152をマスクとして半導体層(108)の所定の領域(112)に不純物イオンを注入する工程を含む半導体装置の製造方法であって、所定の領域に不純物イオンを注入するためにレジスト膜に開口部を形成する際に使用するレチクル領域全体に対する開口部の割合を示すマスクデータ率が第1の基準値未満の場合に、所定範囲の領域以外の領域に、ダミーイオン注入領域142を設け、レチクルのマスクデータ率が第1の基準値以上の第2の基準値より大きくなるようにする。

(もっと読む)

導体または半導体基板上に堆積させたカーボンナノチューブマットの製造方法

【課題】酸化層の前堆積を行うことなく、導体または半導体材料上に高密度のカーボンナノチューブマットを製造する方法を提供する。

【解決手段】拡散バリア520、拡散バリア上にアモルファスシリコン層530、アモルファスシリコン層上に金属層を含む触媒複合体を導体または半導体基板510上に堆積させる。次いで前記金属層に酸化処理を行い、最後に、酸化処理された金属層からカーボンナノチューブマット580を成長させる。

(もっと読む)

カーボンナノチューブを利用した半導体素子の配線形成方法およびその方法により製造された半導体素子

【課題】高い電流密度を持つカーボンナノチューブを利用した半導体素子の配線形成方法、およびその方法により製造される超高集積度の半導体素子を提供する。

【解決手段】半導体素子の電極120表面を前処理して活性化させる段階と、電極の活性化した表面122上に絶縁層130を形成した後、電極の活性化した表面の一部を露出させるために絶縁層を貫通するコンタクトホール132を形成する段階と、コンタクトホールを通じて電極の活性化した表面に炭素が含まれているガスを供給して前記電極の活性化した表面からカーボンナノチューブ140を成長させて配線を形成する段階と、を具備する半導体素子の配線形成方法およびその方法により製造された半導体素子。

(もっと読む)

カーボンナノチューブ系材料の先端部形成方法

【課題】CNT系材料と他の導電体との低接触抵抗を実現でき、あるいは他の導電体との接触に高い信頼性が確保できる技術を提供する。

【解決手段】凹所に設置され、その凹所上の空間にその先端部が突き出たCNT系材料のその突き出た先端部に、酸化性物質であるまたは酸化性物質を発生しうるガス状物質を接触させつつ、活性エネルギー線を照射する。

(もっと読む)

集積回路のシールリング構造

【課題】

デジタル回路によるデジタル雑音結合を低減できる、改良されたIC(集積回路)チップのシールリング構造を提供する。

【解決手段】IC用のシールリング構造は、ICの周辺に沿って設けられ、少なくとも第一部分と、アナログ及び/またはRF(無線周波数)回路ブロックに対向して同アナログ及び/またはRF回路ブロックを雑音から遮蔽するように設けられる第二部分に分けられたシールリングと、第二部分の下に位置し、P型基板の中に設けられるP+領域と、P+領域を囲み、第二部分の導電壁の下で横方向に延びるSTI(シャロートレンチアイソレーション)構造とを含む。

(もっと読む)

半導体パッケージ

【課題】異方性導電材料により貫通孔内電極の導通部分を形成することにより、信頼性の高い半導体パッケージを提供する。

【解決手段】半導体基板1に形成した貫通孔2の内部を異方性導電材料12により充填し、貫通孔2の上部で半導体基板1に設けられた配線層5と異方性導電材料12とを接続し、貫通孔2の下部に導電部材8の一部を挿入して、該導電部材8と異方性導電材料12とを接続することにより配線層5と導電部材8とを電気的に接続する。これにより貫通孔2の側壁構造に影響されない導通経路を貫通孔2の中央部に設けることができる。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

半導体デバイスの製造方法およびビア不良率予測システム

【課題】半導体デバイスのビアの不良率を高精度に予測するモデル、ならびにこの不良率予測モデルに基づく不良率予測工程を有する半導体デバイスの製造方法および不良率予測システムを提供する。

【解決手段】ビア不良率予測工程を有する半導体デバイスの製造方法であって、前記ビア不良率予測工程は、複数のビアチェーンTEGの不良率を計測するステップS101と、前記ビアチェーンTEGのビア間距離と前記不良率との関係に基づいてビア不良率予測モデル関数を算出するステップS102と、前記半導体デバイスの実際のレイアウトにおいて、各ビアについて最短隣接ビアを決定し、前記各ビアと前記各ビアに対応する前記最短隣接ビアとの間の最短隣接距離を算出するステップS110と、前記ビア不良率予測モデル関数と前記最短隣接距離とに基づいて前記各ビアの不良率を予測するステップS115とを有する。

(もっと読む)

81 - 100 / 219

[ Back to top ]