Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,001 - 2,020 / 2,405

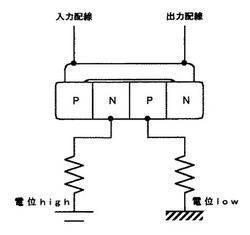

交差ゲート型一時記憶素子

【課題】多数のMOS−FETを使用する既存の一時記憶回路の回路基板上の専有面積と動作電力における不利益を解消し、電子回路中に使用する素子数を削減した記憶素子の提供。

【解決手段】電子演算回路の一時記憶のための電位信号保持に、交差ゲート型一時記憶素子を採用する。N−P−N−Pダイオードの、両端のP、N各半導体と導通するように、そして中間部のP、N各半導体と絶縁してゲート端子を接着した素子の、中間部のP半導体にlow電位、N半導体にhigh電位を入力する配線を接続し、ゲート端子に入出力配線を接続する。

(もっと読む)

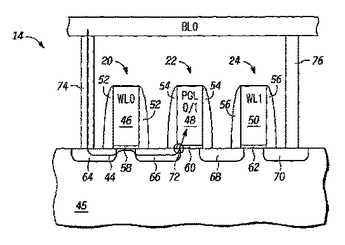

一回限りプログラム可能なメモリ及びそれを動作させる方法

一度限りプログラム可能(OTP)メモリ(10)は高密度化のため2ビットセルを有する。各セル(14)は2つの選択用トランジスタ(20、24)とそれらの間に直列接続されたプログラム可能トランジスタ(22)とを有する。プログラム可能トランジスタ(22)は2つの独立した記憶箇所(72)を有する。一方はゲート(48)と第1のソース/ドレイン領域(66)との間、他方はゲート(48)と第2のソース/ドレイン領域(68)との間である。記憶箇所(72)は、ソース/ドレイン(66、68)がゲート(48)と重なるゲート誘電体(60)部分であり、それらにプログラム電流(44)を選択的に流すことによって独立にプログラムされる。プログラム電流(44)はプログラムされる記憶箇所(72)のインピーダンスの大きさを3桁以上、恒久的に低減させるのに十分な大きさ及び期間を有する。プログラム電流(44)の大きさは、他の回路要素の損傷を回避するために制限され、好ましくは少なくとも部分的にプログラム用トランジスタ(22)のゲート(48)に負電圧を印加することによって誘起される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 優れたトランジスタ特性を有するDRAMが高い集積度で形成された半導体装置を提供する。

【解決手段】 半導体基板(1)に設けられたトレンチと、前記トレンチの内壁下側に設けられたキャパシタ絶縁膜と、前記トレンチの内壁上側に設けられたカラー絶縁膜(9)と前記トレンチ内に埋め込まれたストレージ電極(10)とを有するトレンチキャパシタ、半導体基板に設けられたMOSトランジスタ、および、前記MOSトランジスタのソース/ドレイン拡散領域(18)の一方と前記トレンチキャパシタの前記ストレージ電極とを接続するシリサイド膜(16)を有する半導体装置である。前記カラー絶縁膜は上部に導電膜(20)を有し、前記導電膜は、隔離絶縁膜(19)によって前記半導体基板、前記ストレージ電極、および前記カラー絶縁膜から隔離されていることを特徴とする。

(もっと読む)

メモリ

【課題】メモリセルサイズを小さくすることが可能なメモリを提供する。

【解決手段】このメモリは、ダイオード11を含む複数のメモリセル12と、複数のビット線9と、ビット線9と交差するように配置され、メモリセル12に含まれるダイオード11のカソードおよびワード線10として機能するn型不純物領域21とを備えている。また、n型不純物領域21は、所定数のビット線9からなるビット線群13毎に分割されている。

(もっと読む)

フィン型チャンネル領域を有する不揮発性メモリ素子及びその製造方法

【課題】本体バイアス制御が可能であり、ビット当たりの面積を縮小させて高集積の可能な高性能不揮発性メモリ素子、及びその製造方法を提供する。

【解決手段】本体からそれぞれ突出され、一方向に離隔されてそれぞれ伸張する少なくとも一対のフィンの外側面及び上面の表面付近を少なくとも一対のチャンネル領域として利用でき、少なくとも一つ以上の制御ゲート電極は、チャンネル領域を横切って形成され、制御ゲート電極とチャンネル領域との間の少なくとも一部分には、少なくとも一対のストレージノードが介在されうる不揮発性メモリ素子である。

(もっと読む)

電気機械メモリ、それを用いた電気回路及び電気機械メモリの駆動方法

【課題】従来の半導体プロセスとの親和性が高く、機械的に電気的導通路を完全遮断するスイッチング機能を有し、かつ不揮発性の情報記録を可能とするメモリ素子を実現する。

【解決手段】基板上に形成された電気機械メモリであって、メモリセルを電極で挟む形で形成されており、ポスト部を介して中空に架橋された梁である可動電極を具備した電気機械メモリを実現する。この構成により、簡易な構造で不揮発性メモリを実現することが可能となり、従来実現困難であった低消費電力、低コストの高性能電気機械メモリおよびそれを用いた電気機器が実現可能となる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】

不揮発性メモリと多結晶シリコン薄膜抵抗素子の高精度化、高機能化とを安価に実現できる半導体装置の製造方法の提供を目的とする。

【解決手段】

不揮発性メモリのコントロールゲート電極と配線、多結晶シリコン薄膜抵抗素子を比較的薄い多結晶シリコン膜で形成し、ESD保護素子形成のための高濃度不純物注入をコントロールゲート配線にも行うことを特徴とする製造方法。

(もっと読む)

有機強誘電体メモリ

【課題】小型化及び高集積化を図ることができる有機強誘電体メモリを提供する。

【解決手段】有機強誘電体メモリは、複数の画素領域121を有する基板110と、基板110のそれぞれの画素領域121に設けられた画素電極122と、それぞれの画素電極122に設けられた電気光学素子124と、電気光学素子124を介して複数の画素電極122と対向する対向電極126と、走査線がゲート電極136に電気的に接続され、データ線が一方の電極132に電気的に接続され、画素電極122が他方の電極134に電気的に接続された第1の薄膜トランジスタ130と、第1の薄膜トランジスタ130を介してデータ線と電気的に接続された第1の電極142、第1の電極142に対向する第2の電極146、第1及び第2の電極142,146の間に設けられた有機強誘電体層144を含む有機強誘電体キャパシタ140と、を含む。

(もっと読む)

半導体集積回路装置

【課題】 実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供する。

【解決手段】 第1メモリセルユニット(MU1)の電流通路の一端、及び第2メモリセルユニット(MU2)の電流通路の一端に共通接続された第1ビット線(BL1)と、第3メモリセルユニット(MU3)の電流通路の一端に接続された第2ビット線(BL2)と、第1メモリセルユニット(MU1)の電流通路の他端に接続された第1ソース線(SL1)と、第2メモリセルユニット(MU2)の電流通路の他端、及び第3メモリセルユニット(MU3)の電流通路の他端に共通接続された第2ソース線(SL2)とを具備する。

(もっと読む)

半導体装置及び無線通信システム

【課題】無線通信によりデータの交信が可能な半導体装置において、半導体装置内の回路が過電圧により破壊されることを防止する。

【解決手段】半導体装置内のアナログ回路部、特に高周波回路、電源回路及びデータ復調回路で使用しているトランジスタと、デジタル回路部(ロジック回路部)で使用しているトランジスタとにおいて、アナログ回路部内のトランジスタのゲート長をデジタル回路部内のトランジスタのゲート長以上とする。こうして、過電圧が供給された際にゲート長の長いアナログ回路で電圧を緩和し、当該アナログ回路から出力された信号が入力されるデジタル回路部において、トランジスタ等の回路内の素子が破壊されるのを防止する。また、アナログ回路部、特に電源回路及びデータ復調回路は周波数の速い動作は必要がなく、一方、デジタル回路部等は周波数の速い動作が必要とされるので、それぞれの目的にあった無駄のない動作が実現できる。

(もっと読む)

半導体装置とその製造方法

【課題】 キャパシタ直下の導電性プラグが埋め込まれるホールの加工精度を高めることが可能な半導体装置とその製造方法を提供すること。

【解決手段】 第1絶縁膜11の第1、第2ホール11a、11b内に第1、第2導電性プラグ32a、32bを形成する工程と、酸化防止絶縁膜14に第1開口14aを形成する工程と、第1開口14a内に補助導電性プラグ36aを形成する工程と、補助導電性プラグ36a上にキャパシタQを形成する工程と、キャパシタQを覆う第2絶縁膜41に第3、第4ホール41a、41bを形成する工程と、第4ホール41bの下の酸化防止絶縁膜14に第2開口14bを形成する工程と、第3ホール41a内に第3導電性プラグ47aを形成する工程と、第3ホール41a内に第4導電性プラグ47bを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

溝に横方向第1ゲート及び縦方向第2ゲートを含むスプリットゲート記憶装置

スプリットゲート記憶装置には、第1ゲート誘電体に接触した第1ゲート電極と、第2ゲート誘電体に接触した第2ゲート電極とが含まれる。第1拡散領域は、半導体基板中に画成された溝(108)の一部の下に横たわり、第2拡散領域は、基板(102)の上部を占有する。第1ゲート誘電体(110)は、溝を内張りする。第1及び第2ゲート誘電体の内の1つには、一層の不連続記憶素子(DSE)(120)が含まれ、第1及び第2ゲート電極の内の1つは、少なくとも部分的に溝内に配置される。一事例では、第1ゲート電極は制御ゲートであり、第1誘電体は一層のDSEを含む。他の事例では、第1ゲート電極は選択ゲートであり、第2誘電体は一層のDSEを含む。第2ゲート誘電体は基板の上面全体に横たわる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 ヒューズ素子を選択的に切断することにより、機能や特性などの変更が可能な機能マクロを有する半導体装置において、ヒューズ素子群を搭載することで生じる配線制約によるレイアウト面積ロスを抑制することができる半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 ヒューズ素子を備えた半導体装置において、前記ヒューズ素子を半導体装置における最上配線層よりも下層側の配線層にて形成し、その配線層の製造工程が完了した時点で、ヒューズトリミングを行い、その後に残りの配線層の製造工程を完了する構成とする。この構成によれば、ヒューズ素子を形成する配線層よりも上層側では、ヒューズ領域上を配線が通過することが可能となる。

(もっと読む)

電界効果トランジスタとその形成方法並びに半導体記憶装置とその製造方法

【課題】トレンチ型DRAMにおいてさらなる高集積化を実現する電界効果トランジスタとそれを用いた半導体記憶装置及びそれらの形成製造方法を提供する。

【解決手段】基板に、第1導電型の一方のソース・ドレイン領域14と、チャネル形成領域となる第2導電型の半導体層16と、ゲート絶縁膜18と、ゲート電極19とを含んで積層されてなる積層体が形成されており、さらに、基板に、一方のソース・ドレイン領域及14及びゲート電極19から絶縁され、半導体層16の側面に接して第1導電型の他方のソース・ドレイン領域10cが形成された電界効果トランジスタとする。また、上記の一方のソース・ドレイン領域14に接続してメモリキャパシタの記憶ノード電極が接続された構成とする。

(もっと読む)

3−トランジスタメモリセルを有する不揮発性メモリ素子及びその製造方法

【課題】3−トランジスタ不揮発性メモリセルを提供する。

【解決手段】半導体基板内に形成され、互いに離隔されたソース領域及びドレイン領域を具備する。前記ソース領域と前記ドレイン領域との間の前記半導体基板上部にソース選択ライン及びドレイン選択ラインが提供される。前記ソース選択ライン及び前記ドレイン選択ラインはそれぞれの前記ソース領域及び前記ドレイン領域に隣接する。前記ソース選択ラインと前記ドレイン選択ラインとの間にセルゲートパターンが提供される。前記選択ラインと前記セルゲートパターンとの間のギャップ領域下部に浮遊不純物領域が提供される。前記セルゲートパターンと前記選択ラインとの間の間隔は前記選択ラインの幅より小さい。前記メモリセルの製造方法も提供される。

(もっと読む)

半導体記憶装置およびROMデータパターンの発生方法

【課題】 メモリセル拡散マスクパターンの形状容易化により、メモリセル拡散マスクパターン形成の安定化及び歩留向上を図る。

【解決手段】 隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターン5で構成し、拡散マスクパターン5がメモリセルアレイ1上に配列され、拡散マスクパターン5で形成されるメモリセルのソースコモン配線8をメタル配線にした。このように、メモリセル拡散マスクパターンを2ビット矩形拡散マスクパターンとし、ソースコモン配線を拡散層からメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化し、さらに実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持し、実メモリセルの拡散マスクパターンのパターン形成精度を向上させ、歩留向上を図る。

(もっと読む)

半導体集積回路装置

【課題】フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を提供する。

【解決手段】周期的に配置された信号電極線BLと、ワード線方向に、信号電極線BLと同一周期で一列に配置された信号電極線コンタクト13と、を備え、信号電極線BLの側面は、第1絶縁材14と、この第1絶縁材14上に積層された第2絶縁材15とに接しており、ワード線方向の断面において、信号電極線BLの、信号電極線コンタクト13に接する部分の径Dbtmは、信号電極線BLの最上面の径Dtopよりも狭い。

(もっと読む)

記憶素子及び記憶装置

【課題】 短いパルス電圧を印加した場合でも正しく記録を行うことができ、情報の記録及び読み出しを容易に安定して行うことができる記憶素子を提供する。

【解決手段】 第1の電極1と第2の電極4との間に記憶用薄膜3が挟まれて構成され、この記憶用薄膜3に少なくとも酸素と希土類元素とを有して成り、記憶用薄膜3内もしくは記憶用薄膜3と接している層2に、Cu,Ag,Znから選ばれるいずれかの元素が含まれ、素子サイズが70nm以下である記憶素子10を構成する。

(もっと読む)

半導体記憶装置

【課題】 コンパクトな構造で安定にデータを保持可能な半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、データの書き込み制御を行うPMOSトランジスタQ1と、データの読み出し制御を行うNMOSトランジスタQ2と、読み出しデータの電流増幅を行うNMOSトランジスタQ3とを備えている。トランジスタQ1のゲートとなる第1の半導体層1の上方に書き込みトランジスタ形成領域3を配置し、この書き込みトランジスタ形成領域3内にトランジスタQ1のソース、チャネルおよびドレインとトランジスタQ2のゲートとを形成するため、セル構造をコンパクトな形状にすることができる。

(もっと読む)

高密度不揮発性メモリアレイ及び製造方法

【課題】メモリアレイの密度を高めることのできる不揮発性メモリアレイ及びその製造方法を提供する。

【解決手段】 不揮発性メモリアレイは、サブF(サブ最小特徴サイズF)幅だけ離間して配置されたワード線と、該ワード線にほぼ垂直なビット線とを有する。少なくとも最小特徴サイズFの幅を有するマスク生成素子から、スペーサー技術を用いてサブFワード線を生成する段階を含む不揮発性メモリアレイのワード線パターン形成のための方法を含む。

(もっと読む)

2,001 - 2,020 / 2,405

[ Back to top ]