Fターム[5J106CC01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067)

Fターム[5J106CC01]の下位に属するFターム

アナログ発振回路 (130)

パルス・クロック発振回路 (169)

マイクロ波・分布定数発振回路 (4)

注入同期発振回路 (18)

原子発振器 (149)

掃引周波数発振回路 (4)

掃引電圧発振(発生)回路 (7)

基準発振回路 (165)

局部発振回路 (38)

予備発振回路 (1)

複数の発振回路・VCO (166)

Fターム[5J106CC01]に分類される特許

21 - 40 / 1,216

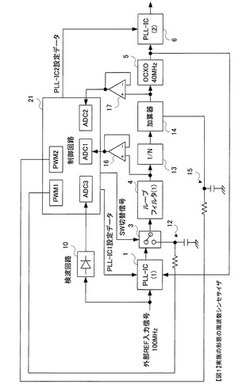

周波数シンセサイザ

【課題】 外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

(もっと読む)

平面型X線センサ

【課題】内部駆動タイミングと外部基準クロックとを整合させる。

【解決手段】X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサの内部駆動信号を生成する内部駆動信号生成回路50に、PLL構成の基準クロック生成回路51を備える。基準クロック生成回路51は、電圧制御発振器62と分周回路63と位相比較回路61とを備える。電圧制御発振器62は、たとえば水晶発振器を用いて、内部基準クロックを生成する。分周回路63は、内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する。位相比較回路61は、外部基準クロックと前記分周クロックとの位相を比較してその位相差を電圧制御発振器62に入力する。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

位相ロック・ループにおけるVCOの動的バイアス印加

【課題】無線通信機器における局部発振器を提供する。

【解決手段】局部発振器が位相ロック・ループを含む。位相ロック・ループは電圧制御発振器23と新規のVCO制御回路27を含む。VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、VCO制御回路は、PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次にPLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程はPLLがロックされたままで行われる。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

PLL回路およびそのキャリブレーション方法

【課題】1回のキャリブレーションによって電圧制御発振器のフリーラン発振周波数がPLLロックレンジ内に入るようにして、キャリブレーション時間の大幅な時間短縮が可能となり、低消費電流化に貢献できるようにする。

【解決手段】PLLループをオープンにし、電圧制御発振器1に制御電圧Vcとして基準電圧Vaを入力したとき、基準信号f3のパルスによって帰還信号f2のパルス幅をカウントし、得られたカウント値に基づき、電圧制御発振器1の発振周波数f1を調整するキャリブレーションを実行するキャリブレーション回路10を設ける。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

PLL回路

【課題】本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【解決手段】本発明は、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力するDCO1と、位相差を示すデジタル信号を出力する位相検出器10と、位相差を示すアナログ信号を出力し、デジタル信号の少なくとも最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有するEXOR型位相比較器21と、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える切替制御部Sと、を備えることを特徴とするPLL回路Pである。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

位相同期回路及びテレビジョン信号受信回路

【課題】チューニングラインに設けられるラインフィルタのフィルタ特性の低下を防止すること。

【解決手段】この位相同期回路は、チャージポンプ(35)から出力されるパルス信号を積分するローパスフィルタ(19)と、ローパスフィルタ(19)から電圧制御発振回路(17A)に対して制御電圧を供給する制御電圧供給ライン(LUHF)に設けられたラインフィルタ(20)と、を具備し、ラインフィルタ(20)のキャパシタ(C1)の一端をチャージポンプ(35)の出力端子からCP電流切替回路(36)の抵抗(r)を介してグランドに高周波的に接続した。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

無線送信機

【課題】局部発振器の位相雑音性能の改善により、送信信号に含まれる隣接チャネル漏洩信号を大幅に低減することができる無線送信機を提供する。

【解決手段】ディジタルデータ信号を出力するデータ信号生成回路と、ディジタルデータ信号をディジタル/アナログ変換し、中間周波数のIF信号を出力するディジタル/アナログ変換回路と、IF信号と局部発振器から出力されるローカル信号とをミキシングし、無線周波数のRF送信信号を出力する直交ミキサ回路とを備えた無線送信機において、データ信号生成回路は、ディジタル/アナログ変換回路から出力されるIF信号の周波数が送信チャネルに応じて切り替わるディジタルデータ信号を出力する構成であり、局部発振器は、RF送信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成である。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

高周波信号処理装置および無線通信システム

【課題】ディジタル型PLL回路を備えた高周波信号処理装置および無線通信システムにおいて、スプリアスの影響を低減する。

【解決手段】例えば、ディジタル位相比較部DPFD、ディジタルロウパスフィルタDLPF、ディジタル制御発振部DCO、マルチモジュールドライバ部(分周部)MMDを備えたディジタル型PLL回路において、DLPFのクロック信号CKDLPFのクロック周波数が複数の選択肢の中から選択可能に構成される。当該クロック周波数は、基準発振信号Frefの整数倍の周波数の中から、DCOの発振出力信号RFdcoに対して規格上のどの周波数帯を設定するかに応じて選択される。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

集積回路

【課題】電源ノイズが存在する環境下において、位相同期回路の出力信号の特性劣化を軽減する。

【解決手段】基準信号源は、基本周波数を有する基準信号を生成する。位相同期回路102は、制御電圧に応じた周波数の信号を生成する電圧制御発振器106と、前記周波数の信号をN分周して第1分周信号を生成する第1分周器107と、第1分周信号と基準信号との位相差を検出する位相検出器103と、チャージポンプ104と、ループフィルタ105と、を含む。第2分周器は、電圧制御発振器により生成された信号をM分周して第2分周信号を生成する。信号処理回路は、第2分周信号に同期して動作する。基本周波数のK倍と、第2分周信号の周波数との差分の絶対値が、電圧制御発振器の入力から位相同期回路の出力までの伝達関数によって表される帯域通過フィルタの低域遮断周波数以下または高域遮断周波数以上となるように、NおよびMの値が決定されている。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

21 - 40 / 1,216

[ Back to top ]