Fターム[5K029JJ08]の内容

直流方式デジタル伝送 (8,390) | 伝送路との接続部 (350) | 整合;反射波抑圧 (222)

Fターム[5K029JJ08]に分類される特許

1 - 20 / 222

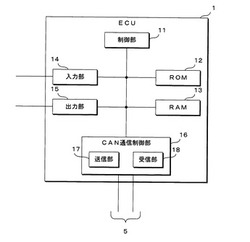

通信システム、通信装置及び通信方法

【課題】リンギングの影響を低減し、通信の高速化を実現可能な通信システム、通信装置及び通信方法を提供する。

【解決手段】ECU1は、送信データがドミナントの場合、第1時間Tpに亘って第1信号レベルの信号を通信線5に出力し、その後の第2時間Thに亘って第2信号レベル(0V)の信号を出力し、送信データがレセシブ且つ通信線5の信号レベルがレセシブの場合、第1時間Tp及び第2時間Thに亘って通信線5へ信号出力をせずハイインピーダンス状態とし、送信データがレセシブ且つ通信線5の信号レベルがドミナントの場合、第1時間Tpに亘って信号出力をせずにハイインピーダンス状態とし、その後第2時間Thに亘って第2信号レベルの信号を出力する。ECU1は、スイッチを切り替えることによって、通信線5に対する抵抗器の接続/遮断を行うことが可能な構成であり、1ビットの送信時間Tbにおける第1時間Tp経過後に抵抗器の接続を行う。

(もっと読む)

信号整形回路および光送信装置

【課題】柔軟な信号整形を行うこと。

【解決手段】演算回路112は、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する。分岐部113は、演算回路112によって出力された信号を分岐し、分岐した各信号の一方を第二入力部へ入力する。また、分岐部113は、分岐した各信号の他方を出力する。遅延回路114は、演算回路112から出力されて分岐部113へ入力される信号または分岐部113から出力されて第二入力部へ入力される信号を遅延させる。

(もっと読む)

電子部品及び反射波キャンセル方法

【課題】電子部品において、抑止すべき反射波を抑止すること。

【解決手段】電子部品1は、ドライバ2、記憶部3、反射波検出部4及び制御部5を有する。ドライバ2は、受信装置に対して、信号を出力する。記憶部3は、ドライバ2が出力した信号が対象とする図示しない受信装置で反射されてドライバ2に戻る反射波に関する反射情報を記憶する。反射波検出部4は、反射情報を基に反射波を測定する測定時間を決定し、測定時間に基づいて反射波の到達時間と反射波の振幅ピーク値を測定する。制御部5は、到達時間と振幅ピーク値から、受信装置における反射波の影響を抑止する反射波キャンセル情報を抽出し、ドライバ2に反射波キャンセル情報を設定する。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

中継装置およびコネクタ

【課題】バス型のネットワークにおいて、接続するノード数を増加させることができる中継装置およびその中継装置を備えたコネクタを提供する。

【解決手段】中継装置としてのASC1に、ビット歪み補正回路15と、リンギングパルス吸収回路16と、を備えて、ビット歪み補正回路15でビット単位にビット歪みを補正し、リンギングパルス吸収回路16で通信フレーム終端のリンギングパルスの吸収除去を行う。

(もっと読む)

通信システム

【課題】比較的安価な構成でリンギング現象を効果的に抑制可能な通信システムを得る。

【解決手段】幹線20の分岐点N1及びN3からそれぞれ放射状に6本の支線21、分岐点N2から図中上下に2本の支線22、合計14本の支線21及び22が接続される。なお、12本の支線21はそれぞれ第1の長さで設けられ、2本の支線22は上記第1の長さより長い第2の長さで設けられる。14本の支線21の端部に14個の非終端ECUであるECU2〜ECU15が接続される。ECU2〜7及び10〜15はそれぞれ抵抗値1800Ωの抵抗R2を有している。さらに、ECU8及び9はそれぞれ抵抗値600Ωの抵抗R3を有している。これら抵抗R2及び抵抗R3はリンギング現象抑制用の補助抵抗として機能する。

(もっと読む)

信号伝送回路

【課題】低コストかつ実装密度が高い回路基板を用いて、信号線間のクロストークノイズを低減するとともに、スタブによる反射ノイズを低減することのできる信号伝送回路を提供する。

【解決手段】本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品を接続する第2配線間に、第1電子部品を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

(もっと読む)

信号伝送システムおよび信号伝送方法

【課題】 伝送線路による信号伝送を行う伝送システムであって小型化が実現可能な信号伝送システムを実現する。

【解決手段】 誘電体層(1a)上の同一面内に配置された信号用号導体(2p1、2n1)と誘電体層(1a)を挟んで対向して配置された信号用導体(2p2、2n2)とを備えた伝送線路(201)において、誘電体層(1a)を挟んで対向する信号用導体同士が異なる極性同士の電圧となるよう差動信号源(3)から差動信号を伝送線路に出力し、上記4つの信号用導体により差動信号を伝送線路(201)を同一方向に信号伝送させることにより、伝送される差動信号により誘電体層(1a)の中央部に電気壁と等価とみなせる電界分布を形成させる。

(もっと読む)

差動伝送回路、光送受信モジュール、及び情報処理装置

【課題】差動伝送線路が屈曲領域を有する場合にも、2つの差動信号に生じる遅延時間差が抑制されるとともに、高密度な実装を可能とする、差動伝送線路、並びに、それを用いた光送受信モジュール及び情報処理装置の提供。

【解決手段】本発明に係る差動伝送線路は、1対の伝送線導体と、1対の伝送線導体と対向する領域を含んで外方に広がる接地導体層とを備える、差動伝送線路であって、1対の伝送線導体は、第1の幅で互いに平行して第1の方向に延伸するとともに第1の一層上に形成される、第1の直線領域と、1対の伝送線導体の一方は第1の層上に形成され、他の一方は第2の層に形成され、1対の伝送線導体が立体的に交差するとともに、第1の直線領域の前方に配置される第1の交差領域と、を含み、第1の交差領域における1対の伝送導体の幅それぞれは、ともに前記第1の幅より小さい、ことを特徴とする。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

通信装置および通信装置設定方法

【課題】クロストークの影響を抑止して伝送路の信号波形調節がおこなえること。

【解決手段】通信装置は、内部に信号伝送する複数の伝送路と、伝送路の信号波形調節により伝送特性が好適となる状態に変更自在なプリエンファシス部,ラインイコライザと、このプリエンファシス部,ラインイコライザによる伝送路の伝送特性の調節を制御するとともに、調節する伝送路に影響を与える他の伝送路を判定し、他の伝送路からのクロストークの発生を抑止する制御をおこなう好適化制御部と、を備える。

(もっと読む)

伝送回路、プリント回路基板

【課題】搭載する部品を回路毎に変更することなく、伝送経路の特性に合わせて回路の周波数特性を平滑化することのできる、低消費電力の伝送回路を提供する。

【解決手段】本発明に係る伝送回路は、信号伝送線に並列接続されたインダクタを有するパッシブイコライザを備え、インダクタは回路基板のスルーホール側面に形成された導体部分を用いて構成されている。

(もっと読む)

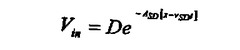

制御可能な減衰と伝播速度とを有する波形を伝送する方法

【課題】波形を伝送する方法を提供する。

【解決手段】制御可能な減衰と伝播速度とを有する波形を伝送する装置と方法とを説明する。例示的な方法は指数波形を生成することを含み、この指数波形は、(a)次の式

で表され、ただし、Dは大きさ、Vinは電圧、tは時間、ASDは減衰係数、vSDは伝播速度であり、(b)最大値で切り欠かれる。例示的な機器は、指数波形発生器と、指数波形発生器の出力に結合する入力記録器と、指数波形発生器の出力に結合するテスト対象の伝送路と、テスト対象の伝送路に結合する出力記録器と、テスト対象の伝送路に結合する別の伝送路と、別の伝送路と接地とに結合する終端インピーダンスとを備える。

(もっと読む)

半導体集積装置およびそれを備える表示装置

【課題】電磁波の不要輻射および伝送欠陥を低コストで低減することができる、半導体集積装置およびそれを備える表示装置を提供することを目的とする。

【解決手段】タイミングコントローラIC400が含む出力インターフェース回路420_1は、出力バッファ422と、出力バッファ422の後段に設けられた減衰部424とを有している。出力バッファ422は、正側画像信号DV1(+)および負側画像信号DV1(−)からなる差動信号を出力する。減衰部424は、1対のローパスフィルタ425Aおよび425Bを有している。ローパスフィルタ425Aおよび425Bにより高周波成分がそれぞれ減衰された正側画像信号DV1(+)および負側画像信号DV1(−)は、それぞれ伝送線路610Aおよび610Bに与えられる。

(もっと読む)

リピータ装置

【課題】簡易な構成でありながら、自動的に適切な高域ゲインに調整することのできるHDMIリピータ装置を提供する。

【解決手段】第1認証判断手段4は、ライン18のDDC信号を監視し、HDCP第1認証が行われるか否かを判断する。HDCP第1認証が行われると判断すると、高域ゲイン調整手段6は、イコライザ部2の高域ゲインを調整する。強制ホットプラグ手段8は、強制的にホットプラグ検出信号を出力し、調整された高域ゲインによって、HDMIソース装置SOからHDMIシンク装置SKにTMDS信号を送信させるようにする。

(もっと読む)

中継装置

【課題】第2通信信号が中継先から中継元の伝送路に帰還されることを防止して、波形を乱すことなく第2通信信号を中継可能な中継装置を提供する。

【解決手段】中継装置1は、第1抽出部111と第2重畳部132との間に挿入された第1スイッチ151と、第2抽出部112と第1重畳部131との間に挿入された第2スイッチ152とを備えている。第1スイッチ151は、第1伝送路21から第2伝送路22へ中継される重畳信号の経路のオンオフを行い、第2スイッチ152は、第2伝送路221から第1伝送路21へ中継される重畳信号の経路のオンオフを行う。第1スイッチ151は、第2伝送路22から第1伝送路21への重畳信号の中継時にオフするように、第1制御信号を受けてオンオフ制御される。第2スイッチ152は、第1伝送路21から第2伝送路22への重畳信号の中継時にオフするように、第2制御信号を受けてオンオフ制御される。

(もっと読む)

差動信号出力装置、差動信号出力装置のテスト方法、および、テスタ

【課題】差動信号とコモンモード信号をより適切に評価することが可能な差動信号出力装置を提供する。

【解決手段】差動信号を評価する差動信号テストモードにおいて、差動信号出力装置の第1の制御回路は、第1の制御信号に応じて、差動信号生成回路にデータ信号に応じた差動信号を生成させて第1および第2の送信端子に出力させ、且つ、差動信号出力装置の第2の制御回路は、第2の制御信号に応じて、コモンモード信号生成回路の動作を停止する。コモンモード信号を評価するコモンモード信号テストモードにおいて、第1の制御回路は、第1の制御信号に応じて、差動信号生成回路に固定の差動信号を生成させて第1および第2の送信端子に出力させ、且つ、第2の制御回路は、第2の制御信号に応じて、コモンモード信号生成回路にクロック信号に応じたコモンモード信号を生成させて第1および第2の送信端子に出力させる。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

信号伝送システムおよび半導体回路

【課題】受信回路の負荷容量が変化しても、スルーレートの低下の抑制とリンギングの抑制を両立させることが可能な信号伝送システムを提供する。

【解決手段】送信回路からの信号を配線を通じて受信回路へ伝送する信号伝送システムであって、前記送信回路を実装する第1の基板上において、前記配線に対して直列に接続された第1のRC並列回路と、前記受信回路を実装し、前記第1の基板に着脱可能である第2の基板上において、前記配線に対して直列に接続された第2のRC並列回路とを備えることを特徴とする。

(もっと読む)

半導体集積回路およびその動作方法

【課題】多ビットの差動受信回路および差動終端抵抗を内蔵して、半導体チップ面積と消費電流の増大を軽減する。

【解決手段】複数の差動受信回路2A、B〜Nと複数の差動終端抵抗回路3A、B〜Nと複数の制御電圧供給回路6A、B〜Nに、レプリカ抵抗回路4と制御電圧生成回路5が共用される。複数の回路6A、B〜Nの各回路は、第1非反転入力と第1反転入力と出力を有する差動増幅器DA1を含む。第1供給回路6Aの第1差動増幅器の第1非反転入力と、第2供給回路6Bの第2差動増幅器の第1非反転入力と、第N供給回路6Nの第N差動増幅器の第1非反転入力とに、生成回路5から生成される差動終端抵抗制御電圧Vcont1.5が共通に供給される。第1差動増幅器の出力電圧VoutAと第2差動増幅器の力電圧VoutBと第N差動増幅器の出力電圧VoutNとは、第1と第2と第Nの差動終端抵抗回路3A、3B、3Nにそれぞれ供給される。

(もっと読む)

1 - 20 / 222

[ Back to top ]