Fターム[2G132AL00]の内容

電子回路の試験 (32,879) | 目的、その他 (6,788)

Fターム[2G132AL00]の下位に属するFターム

被試験体の識別、存在の検知 (22)

接続の確実化 (517)

接続の確認、誤接続の検出 (109)

接続線の本数の減少(端子数の減少) (295)

多品種への対応(汎用性のあるもの) (130)

試験時間の短縮 (1,339)

試験精度の向上 (1,554)

不良箇所、原因の特定等 (520)

試験装置の調整 (288)

インピーダンスマッチ (76)

温度調整 (87)

レベル変換 (8)

複数の被試験体の試験 (254)

母線(バス等)に接続した状態での試験 (19)

異常時の処理、保護 (119)

低機能装置で高機能素子を試験 (203)

試験装置の構成要素の配置改善 (287)

試験装置の動作試験 (78)

試験方法としては一般的なもの (13)

Fターム[2G132AL00]に分類される特許

121 - 140 / 870

論理検証シナリオ生成装置、及び、論理検証シナリオ生成プログラム

【課題】CPUの論理検証に用いる検証シナリオ、及び期待値の生成負荷を抑える。

【解決手段】RTL記述されたCPUの論理検証のためのテストプログラムを生成する論理検証シナリオ生成装置であって、テストライブラリと、期待値フォーマット記憶部と、検証命令アドレス、前命令空間、後命令空間、データ空間、分岐命令空間、スタック空間とを有するメモリモジュールであって、テストライブラリから順次選択した検証命令と前後命令組合せとに基づいて、検証命令アドレスに検証命令を、前命令空間に前命令を、後命令空間に後命令を記憶し、前命令が分岐命令である場合に前命令の分岐先アドレスに検証命令アドレスを記憶したメモリモジュールをテストプログラムとして生成するテストプログラム生成部と、テストプログラムの各命令について期待値フォーマットを取得し、当該命令をデコードしたデコード情報に基づいて期待値を生成する期待値生成部と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】テスト時間の増加を防止しながら、低コストで、効率よく品種展開された半導体装置のテストを行う。

【解決手段】計算機3から、テストプログラム、テストパターン、および半導体装置のROMに書き込まれるROMファイルが、テスタ4に送信される。テスタは、品種固有テストであるRAM機能テスト、電源リーク測定、およびROMファイルを書き込むROM書き込みのそれぞれのテストの前に、ROMファイルに含まれるROMファイル番号が、’XXX’か、’YYY’かを判定し、テスト中の半導体装置が品種Aか、品種Bかを判定する。これら品種固有テストでは、品種の判定結果に基づいて、判定された品種に見合った規格値によるテスト判定が行われる。

(もっと読む)

テスト装置およびテスト信号発生装置

【課題】集積回路をテストするテスト装置において、費用、期間を削減する。

【解決手段】テスト装置1の制御部11は、集積回路6のテストを制御するための信号を出力する。テスト信号発生部66は、制御部11から出力された信号の入力に応じて、集積回路6に入力可能なテスト信号を発生する。分岐マルチプレクサ41には、複数の集積回路6が接続される。分岐マルチプレクサ41は、テスト信号を複数の分岐テスト信号に分岐し、接続されている複数の集積回路6に対して並列に出力する。

(もっと読む)

半導体集積回路装置

【課題】レギュレータ内蔵の半導体集積回路(チップ)に対して、スキャン試験を行う場合、チップの活性化率が非常に高くなるため、IRドロップにより、正しいテスト結果を得ることが出来ない。

【解決手段】チップの有するスキャンチェイン群を複数の回路ブロックに分割する。スキャン試験を行う前に、該回路ブロックへ電圧を供給し、各回路ブロックの入力電圧と予め定められる基準電圧を比較し、入力電圧が低い回路ブロックが存在する場合、いずれかの回路ブロックへのテストクロックの供給を遮断する。これにより、レギュレータの電力駆動力に応じた分だけの回路ブロックをスキャン試験することが可能となる。

(もっと読む)

半導体集積回路

【課題】一部の回路領域の電源を遮断した時にその回路領域からの出力を固定化するアイソレータセルの回路規模の低減、動作の高速化および誤設定が発生の低減および修正可能なLSIの実現。

【解決手段】複数の回路領域12A,12B,12Cと、1つの回路領域へ電源供給するか否かを切り替える電源スイッチTrBと、電源スイッチの制御を行う電源制御回路13と、1つの回路領域から他の領域への出力が入力される複数のフリップフロップを有するクランプスキャンチェーンSFF21と、クランプスキャンチェーンのフリップフロップを所定の出力状態に設定するクランプデータ制御回路30,18,21,23と、を備える半導体集積回路。

(もっと読む)

集積回路、シミュレーション装置、及びシミュレーション方法

【課題】LSIを実際の使用形態に沿って動作させるような入力パターンを用いて、LSI内部の遅延故障をLSI外部において効率良く検出することを目的とする。

【解決手段】開示の装置は、LSIのディレイテスト用のディレイテストパターンを生成する制御を行う。入力パターン制御回路は、被試験対象回路へ供給される入力パターンのサイクル数をカウントし、予め設定されたカウント数と一致した時点で、被試験対象回路への入力パターンの供給を停止し、入力パターン保存回路は、このような入力パターンを保存する。スキャン制御回路は、入力パターン制御回路からの制御信号を受け、被試験対象回路へスキャンシフト信号を供給し、被試験対象回路内のスキャンチェインをシフトさせる。そして、期待値生成回路は、スキャンチェインの出力を期待値データとして保存する。

(もっと読む)

異常箇所検出方法及び装置

【課題】複数の構成部品(ASIC)が搭載された基板の異常の有無を短時間に、簡略に検知するとともに、データバス等の異常箇所も検出できるようにする。

【解決手段】複数の構成部品を1つの単位とする部品ASIC10が同一基板上に搭載された基板の異常を検出する異常箇所検出装置であって、前段の前記部品に設けられ、後段の部品に所定のパターンTP0を出力する手段と、後段の前記部品に設けられ、前段から入力されるパターンTPOと同一のパターンTP1を生成するテストパターン生成モジュール7及び前記入力されたパターンTP0と前記生成されたパターンTP1とを比較するテストパターン比較モジュール8と、両者の比較結果に基づいて異常発生の有無を検出するCPU4と、を備えた。

(もっと読む)

スキャンチェーン形成方法、プログラム及び設計支援装置

【課題】タイミングエラーを解消しつつも、遅延素子の増加及び試験コストの増大を抑制することのできるスキャンチェーン形成方法を提供する。

【解決手段】複数のスキャンFFを、各スキャンFFのスキャン端子間の配線長が最短となるようにスキャンチェーンを形成する。その後、複数のスキャンFFのうちタイミングエラーの発生した対象スキャンFFを中心とした、タイミングエラーの発生しない座標集合X3を算出し、その座標集合X3内に配置されたスキャンFFの中から、リオーダー処理前のスキャンチェーンのつなぎ順をできる限り保持するように1つのスキャンFFを選択する(ステップS17〜S19,S23)。続いて、その選択したスキャンFFと対象スキャンFFとを接続するようにつなぎ順を変更する(ステップS20)。

(もっと読む)

試験装置用の電源装置およびそれを用いた試験装置

【課題】回路面積やコストの増加を抑制しつつ、被試験デバイスに安定的に電源供給可能な電源装置を提供する。

【解決手段】DUT1に電源信号S2(Vdd)を供給する試験装置用の電源装置100が提供される。A/Dコンバータ22は、電源信号S2に応じたアナログ観測値S2’をアナログ/デジタル変換し、デジタル観測値S3を生成する。デジタル信号処理回路24は、A/Dコンバータ22からのデジタル観測値S3が所定の基準値Refと一致するように調節される制御値S4をデジタル演算処理によって生成する。D/Aコンバータ26は、制御値S4をデジタル/アナログ変換し、DUT1に電源信号S2として供給する。デジタル信号処理回路24は、その信号処理の内容が変更可能に構成される。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】メモリ及びメモリ周辺ロジック間のテストを、スキャンテストにて実現することができる半導体周期回路を提供する。

【解決手段】半導体集積回路は、メモリセル22〜25及び冗長セル26,27と、メモリセルに欠陥があった場合に冗長セルを選択するセレクタ28とを有するメモリ10と、外部からの情報に基づきセレクタに冗長セルを選択させるための第1の制御信号を生成する救済制御回路13と、救済制御回路13の第1の制御信号をラッチする救済情報保持ラッチ14と、を有する。そして、救済情報保持ラッチ14は、第2の制御信号に応じて救済制御回路13が生成した第1の制御信号をラッチする。

(もっと読む)

時間デジタル変換回路、及びその校正方法

【課題】高分解能のTDC回路の消費電力を低減することを目的とする。

【解決手段】本発明に係るTDCは、入力信号を遅延する遅延素子11を複数直列に接続するディレイラインと、ディレイラインの最後段の遅延素子の出力の反転信号を出力する反転素子13と、基準クロック、又は反転素子の出力信号のいずれかをディレイラインの初段の遅延素子に提供するマルチプレクサ15と、を有するリング発振器10と、ディレイラインの遅延素子の接続ノード、又は初段の遅延素子の入力ノードに接続され、被測定信号の変化エッジが、遅延素子11の出力する基準クロックを遅延した信号の変化エッジに対して進んでいるか遅れているかを判定する複数の判定回路17と、判定回路17の判定結果をエンコードするエンコーダ回路31と、エンコーダ回路31の出力から、被測定信号の変化エッジの基準クロックに対する位相を算出する演算回路33と、を備える。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】精度の高い回路シミュレーションを実行する回路シミュレーション方法を提供する。

【解決手段】ゲートレベルでの電圧変動解析ステップを実行する(ステップS2)。ゲートレベルでの電圧変動解析ステップは、チップTP全体に対して実行する。そして、次に、電圧変動解析ステップに従う電源電圧および接地電圧(Vss)の電圧波形を取得するステップを実行する(ステップS4)。次に、トランジスタレベルでの信号解析ステップを実行する(ステップS6)。トランジスタレベルでの信号解析解析ステップは、チップTP全体よりも範囲の狭い例えば、すべてではない、1つ又はそれ以上の機能モジュールに対して実行する。そして、信号解析ステップに従う信号解析結果を取得するステップを実行する(ステップS8)。

(もっと読む)

試験装置、試験方法、そのコンピュータ・プログラムおよびそのプログラムを記録した記録媒体

【課題】ロット間のばらつきやウェハ面内のばらつきがある場合でも、高精度で良品/不良品の判定を行なうことが可能な試験装置を提供すること。

【解決手段】基準空間作成部22は、第1のロットの良品チップの試験データからウェハ内のチップに付されたチップ番号別に基準空間を作成する。基準値抽出部25は、基準空間作成部22によって作成された基準空間に対応する第1のロットの不良品チップの試験データから、基準空間のそれぞれに対して有効な試験項目およびその試験項目に対応する良否判定の基準値を抽出する。そして、良否判定部26は、基準空間のそれぞれに対するマハラノビスの距離の平均をチップ番号別に算出し、平均値が最小となる基準空間に対応する基準値を用いて第2のロットのチップの良否を判定する。したがって、ロット間のばらつきやウェハ面内のばらつきがある場合でも、高精度で良品/不良品の判定を行なうことが可能となる。

(もっと読む)

半導体集積回路、そのテスト方法、半導体集積回路の設計方法及びプログラム

【課題】異なるクロックで動作する回路を有する半導体集積回路において、回路規模を増大させることなく、実使用でのクロックでスキャンテストの実施が可能なスキャンテスト回路を備えた半導体集積回路を提供する。

【解決手段】異なるクロックのうち低い周波数でスキャンデータを全てのスキャンフリップフロップに設定し、遅延テストの実施の際には異なるクロックドメイン間でのデータの転送が発生しないようにクロックを遮断し、遅延テストを実施する。

(もっと読む)

テスト回路およびテスト回路の制御方法

【課題】テスト専用端子の増加を防ぎ、テストの長時間化を防止する。

【解決手段】テストアクセスポートに入力されるテスト信号に応じて、回路ブロックの試験を行うテスト回路であって、第1のTAP制御部及びその制御下にある第2のTAP制御部と、第1のTAP制御部のテスト動作の無効と、記憶情報の書き換えを不可に制御する第1の情報を記憶する第1のレジスタと、第1の情報に応じて記憶情報の書き換えを不可に制御され、第2のTAP制御部のテスト動作の有効・無効の制御する第2の情報を記憶する第2のレジスタと、外部から入力されるTDI信号に応じて前記第1、2のレジスタが書き換え不可状態を解除する制御回路と、を有するテスト回路。

(もっと読む)

自動テスト機器用高速故障捕捉装置および方法

【課題】 故障処理回路において、テスト対象メモリ(MUT)から故障ロケーション情報を識別するために使用される故障捕捉回路が開示される。

【解決手段】 故障捕捉回路は、複数のチャネルを備え、MUTに接続するように適合される故障検出回路を含む。故障検出回路は、テスト信号をMUTに与え、そこからの出力信号を処理して故障情報にするように動作する。テスト時間を最小化するために、故障メモリ回路および高速リンクが設けられる。高速リンクは、故障メモリ回路を故障検出回路に接続し、シリアルデータ転送能力をその間に提供する。

(もっと読む)

試験装置および信号処理回路

【課題】試験装置の回路規模を低減する。

【解決手段】被試験デバイスを試験する試験装置であって、それぞれが被試験デバイスと信号を受け渡す複数のチャネルと、複数のチャネルに対応する複数の信号を処理する信号処理回路とを備え、信号処理回路は、複数の信号を、予め定められたチャネルの順番で時分割に選択する入力セレクタと、入力セレクタが選択した信号に応じた信号を出力する処理部と、複数のチャネルに対応して設けられ、それぞれ信号を格納する複数の保持部と、処理部が出力するそれぞれの信号を、複数の保持部のうち、予め定められたチャネルの順番に応じた保持部に格納する出力セレクタとを有する試験装置を提供する。

(もっと読む)

スキャンテスト装置及びスキャンテスト方法

【課題】回路規模が増大することなく、テストデータを入力する入力端子の個数を削減できるスキャンテスト装置及びスキャンテスト方法を提供すること。

【解決手段】本発明にかかるスキャンテスト装置1は、テストデータ入力端子、OR素子17、スキャンフリップフロップ12を備える。テストデータ入力端子には、第1のスキャンチェーンに対する第1のテストデータと第2のスキャンチェーンに対する第2のテストデータとを少なくとも含むテストデータが入力される。OR素子17は、テストデータが入力され、クロック信号とは非同期であるマスク信号に基づいて、第2のテストデータをマスクして、第1のテストデータを出力する。スキャンフリップフロップ12は、前記第1のスキャンチェーンの先頭に配置され、OR素子17が出力した第1のテストデータに対応する非同期テストデータを保持する。

(もっと読む)

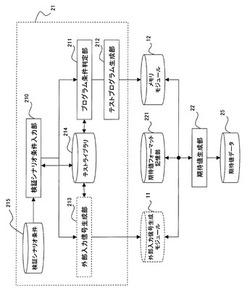

テスタシミュレーション装置、テスタシミュレーションプログラムおよびテスタシミュレーション方法

【課題】論理検証およびテストデバッグに要する総時間の短縮化を図ることを目的とする。

【解決手段】テスタによるDUTの試験を仮想的にシミュレーションするテスタシミュレーション装置1は、DUTの動作をシミュレータ上でモデル化した仮想デバイス11と、仮想デバイス11の論理検証を行うための検証シナリオの入力パターンを仮想デバイス11に印加し、仮想デバイス11から出力される応答パターンを入力して期待値パターンと比較して良否判定を行う仮想テスタ12と、入力パターンおよび期待値パターンを仮想テスタ12から取得し、入力パターンおよび応答パターンが正常なものであるときに、取得した入力パターンおよび期待値パターンをDUTの実試験を行うためのテストパターンとして生成するテストパターン生成部14と、を備えている。

(もっと読む)

半導体集積回路装置

【課題】ユーザ回路における消費電流をより低減する。

【解決手段】ユーザ回路13と、ユーザ回路13のスキャンテストに係るデータを保持するスキャンフリップフロップ回路FF11〜FF1nと、スキャンフリップフロップ回路FF11〜FF1nの出力値および一定の論理値のいずれか一方をユーザ回路13に出力するゲート回路(AND10、AND11〜AND1n)と、を備え、スキャンテストに係るシーケンスにおいて、一定の論理値をユーザ回路13に出力するようにゲート回路(AND10、AND11〜AND1n)を制御する。

(もっと読む)

121 - 140 / 870

[ Back to top ]