Fターム[5F033XX00]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696)

Fターム[5F033XX00]の下位に属するFターム

平坦化 (793)

段差被覆性改善、段切れ防止 (570)

微細化 (1,181)

エレクトロマイグレーション防止 (477)

ストレスマイグレーション防止 (204)

オーミック性向上 (46)

低抵抗化 (1,713)

低融点化 (3)

密着性改善 (1,147)

エッチングマスクのずれ対策 (331)

ヒロック防止 (130)

クラック防止、歪み防止 (509)

腐食防止 (505)

応力の利用、応力の低減 (758)

酸化防止 (315)

残さの除去 (252)

放熱 (140)

基板と配線又は配線間の干渉防止 (1,198)

信号の遅延防止、伝達の同時化 (255)

拡散、突き抜け防止 (992)

短絡防止 (613)

遮光 (95)

製造工程の簡略化 (781)

製造コストの低下 (762)

成膜時の膜厚の制御 (46)

配線修理 (121)

検査、試験 (367)

Fターム[5F033XX00]に分類される特許

21 - 40 / 1,392

半導体装置

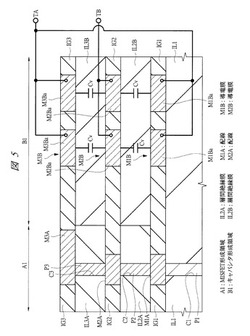

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

パターン構造体の製造方法

【課題】基材上にパターンを低温かつ低コストで形成することができると共に、リフトオフを容易にできるパターン構造体の製造方法を提供する。

【解決手段】実施形態に係るパターン構造体の製造方法では、基材10上に、インクジェット法によりリフトオフ材12を形成する。次に、基材10及びリフトオフ材12上に、原子層堆積法により機能膜14を形成する。次に、リフトオフ法によりリフトオフ材12を除去することによって、基材10上に、機能膜14からパターン14aを形成する。リフトオフ材12は、樹脂と溶媒とを含むインクを基材10上に塗布した後、溶媒を除去することによって形成される。溶媒は、樹脂に対する第1溶解性を有する第1溶媒と、第1溶解性よりも低い第2溶解性を有する第2溶媒とを含む。第1溶媒は第2溶媒に相溶する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビア層絶縁膜にビア用の孔を形成する工程において、シールリングのうちビア層絶縁膜に位置する部分に、導体を埋め込むための溝を形成しないで済むようにする。

【解決手段】ビア層絶縁膜40及び第2配線層絶縁膜50にはシール溝121が形成されている。また、エッチングストッパー層30には複数の孔31が形成されている。第2シール導体パターン120は、複数の孔31及びシール溝121に埋め込まれている。そして、エッチングストッパー層30は、シール溝121の底面に位置する部分が薄膜部32となっており、シール溝121が形成されていない部分と比較して薄くなっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】異なる深さに位置する導電層を露出させた接続孔を有する半導体装置において、浅い導電層の過剰なエッチングを防止し、半導体装置の歩留まりの向上を図る。

【解決手段】第1導電層および第1導電層よりも深く配置された第2導電層を内部に有する基板上に、第1導電層および第2導電層の上部を露出する開口を有する大径レジストパターンを形成する。この大径レジストパターンをマスクにしたエッチングに基づいて、第1導電層を底部に露出させた大径凹部を、基板に形成する。基板上に、第2導電層の上部を露出する開口を大径凹部の形成範囲内に有する小径レジストパターンを形成する。この小径レジストパターンをマスクにしたエッチングに基づいて、第2導電層を底部に露出させた小径凹部を、基板に形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極と配線との接続部位の抵抗のバラつきを低減させて、配線信頼性を向上させる。

【解決手段】貫通電極用の穴部を設け、配線層に対してオーバエッチングを施す。穴部に銅を埋め込むことにより、銅からなる貫通電極を形成させて、アルミニウムからなる配線と接続させた後、熱処理により貫通電極と配線とが接続される接触領域Gを合金化させることで、貫通電極と配線との抵抗バラつきを低減させて、配線信頼性を向上させる。本技術は、半導体装置と、その製造に適用することができる。

(もっと読む)

半導体装置の製造方法

【課題】電気めっき装置のハードウェアトラブルを低減しながら、銅めっき膜の均一性を保つ。

【解決手段】自動分析器14は、電極16,17間に印加されている電圧を検出し、その電圧値が設定電圧範囲内であるか否かを判断する。検出した電圧値が、設定電圧範囲の下限値よりも低い場合、自動分析器14は、検出した電圧値に基づいて、基本液の不足量を算出し、バルブ11を制御して不足分の基本液を補充した後、めっき液タンク6内のめっき液が規定量を保つようにバルブ13の動作制御を行い、めっき液を廃液する。また、検出した電圧値が設定電圧範囲の上限値よりも高い場合、検出した電圧値に基づいて基本液の超過量を算出し、バルブ12を制御して基本液の濃度が規定範囲内となるように純水をめっき液タンク6に補充してめっき液を薄めた後、バルブ13を制御して規定量を保つようめっき液を廃液する。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

プラズマエッチング方法及び半導体装置の製造方法

【課題】トレンチ・ビア形状のウエハ面内均一性を向上できるプラズマエッチング方法を提供する。

【解決手段】基板上の第1配線層の上に絶縁層と金属層とを形成するステップと、絶縁層内に形成される第2配線層のためのトレンチを画成する金属マスク層を金属層から形成するステップと、金属マスク層を覆う平坦化膜を形成するステップと、トレンチの底部に形成され第1及び第2配線層を接続するビアを画成するマスク層を平坦化膜から形成するステップと、マスク層で、絶縁層の厚さよりも小さい開口を形成する第1ステップと、金属マスク層で絶縁層をエッチングしてトレンチを形成し、開口を深くしてビアを形成する第2ステップとが行われる。第1及び第2ステップでは、供給されたエッチングガスの拡散の影響が支配的な位置と、供給されたエッチングガスの流れの影響が支配的な位置とに対応してエッチングガス供給条件が調整される。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

ドライエッチング方法

【課題】 基板上に形成されているシリコン膜と絶縁膜が積層している層状構造を有する積層膜に、基板面に垂直方向に形成されている孔又は溝の内側面に現れているシリコン層のドライエッチング深さの不均一化を抑制すること。

【解決手段】 基板上に形成されている、シリコン層と絶縁膜が積層している層状構造を有する積層膜に、基板面に垂直方向に形成されている孔又は溝の内側面に現れているシリコン層に対し、エッチングガスを用いてエッチングするドライエッチング方法において、エッチングガスとして、ClF3、BrF5、BrF3、IF7、IF5から選ばれる少なくとも1種類のガスとF2とを含有するガスを用いることを特徴とするドライエッチング方法。

(もっと読む)

半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

(もっと読む)

21 - 40 / 1,392

[ Back to top ]