Fターム[5F033XX00]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696)

Fターム[5F033XX00]の下位に属するFターム

平坦化 (793)

段差被覆性改善、段切れ防止 (570)

微細化 (1,181)

エレクトロマイグレーション防止 (477)

ストレスマイグレーション防止 (204)

オーミック性向上 (46)

低抵抗化 (1,713)

低融点化 (3)

密着性改善 (1,147)

エッチングマスクのずれ対策 (331)

ヒロック防止 (130)

クラック防止、歪み防止 (509)

腐食防止 (505)

応力の利用、応力の低減 (758)

酸化防止 (315)

残さの除去 (252)

放熱 (140)

基板と配線又は配線間の干渉防止 (1,198)

信号の遅延防止、伝達の同時化 (255)

拡散、突き抜け防止 (992)

短絡防止 (613)

遮光 (95)

製造工程の簡略化 (781)

製造コストの低下 (762)

成膜時の膜厚の制御 (46)

配線修理 (121)

検査、試験 (367)

Fターム[5F033XX00]に分類される特許

141 - 160 / 1,392

電極構造及びその製造方法

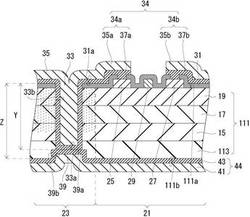

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体装置、半導体装置用基板および該基板の製造方法

【課題】電気的接続の信頼性を損なうことなく電気抵抗率を従来よりも低減できる埋め込み配線を有する半導体装置用基板および半導体装置を提供する。

【解決手段】本発明は、上記目的を達成するため、埋め込み配線を有する半導体装置用基板であって、前記埋め込み配線は、金属多結晶体からなり、平均結晶粒径が異なる少なくとも2層の領域を前記基板の厚さ方向に有し、前記埋め込み配線の開口面を含む層の平均結晶粒径が、前記埋め込み配線の他の層の平均結晶粒径よりも小さいことを特徴とする半導体装置用基板を提供する。また、本発明は、上記半導体装置用基板を用いたことを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体基体同士が張り合わされた構成を有する半導体装において、接合精度の向上を可能とする。

【解決手段】第1半導体基体31と、第2半導体基体45とを備え、第1半導体基体31の第1主面31A側と、第2半導体基体45の第1主面45A側が接合されている。そして、第1半導体基体31の第1主面31A側、第2半導体基体45の第1主面45A側、第1半導体基体31の第2主面31B側、及び、第2半導体基体45の第2主面45B側から選ばれる少なくとも1つ以上に形成されている反り補正層13,14を備える半導体装置79を構成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

銅配線の形成方法、配線基板の製造方法および配線基板

【課題】銅配線の導電性を向上させるとともに、経時変化による劣化を抑制することができる銅配線の形成方法、配線基板の製造方法および配線基板を提供することを目的とする。

【解決手段】粒子径が100nm以上の第1の銅粒子14を分散させた第1の分散液12を塗布し、基板10上に配線パターンを形成するパターン形成工程と、配線パターンを150℃未満の温度で乾燥を行う乾燥工程と、乾燥工程後の配線パターンと同じ位置に、第1の銅粒子14より粒子径の小さい第2の銅粒子18を分散させた第2の分散液16を塗布する塗布工程と、塗布工程後の配線パターンの第1の銅粒子14および第2の銅粒子16間の空隙を埋める緻密化工程と、緻密化工程後の配線パターンを加熱する加熱工程と、加熱工程後の配線パターンを還元処理する還元処理工程と、を有することを特徴とする銅配線の形成方法、配線基板の製造方法および配線基板である。

(もっと読む)

処理方法および記憶媒体

【課題】低誘電率膜のダメージ回復処理を行う際に、比誘電率やリーク電流値を低く維持しつつ内部の水分を除去することができる処理方法を提供すること。

【解決手段】被処理基板に形成された、表面部分にダメージ層を有する低誘電率膜に回復処理を施すにあたり、その分子が、低誘電率膜のダメージ層の内部に浸透できる程度に小さく、ダメージ層内の水分を除去することが可能な第1処理ガスと、ダメージ層の表面に疎水性で緻密な改質層を形成する第2処理ガスとを低誘電率膜のダメージ層に作用させる。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

シリカ系被膜、シリカ系被膜形成用組成物、シリカ系被膜の製造方法及び電子部品

【課題】機械強度が十分であり、低誘電性に優れ、シリコンウエハー及びP−TEOS等のSiO2膜の両方への接着性に優れたシリカ系被膜を提供する。

【解決手段】実質的にOH基の含有量が大幅に減少されてなる高い緻密性を備えた微細孔を有するシリカ系被膜。(a)一般式(1)で表せられる化合物を加水分解縮合して得られるシロキサン樹脂、(化1)R1nSiX4−n(1)(式中、R1は、H若しくはF又はB、N、Al、P、Si、Ge若しくはTiを含む基又は炭素数1〜20の有機基を示し、Xは、加水分解性基を示すし、nは0又は1の整数である)(b)下記一般式(2)で表せられるイオン性化合物並びに(化2)(R24N+)nYn−(2)(式中、R2は、水素原子又は炭素数1〜20の有機基を示し、Yは、陰イオンを示し、nは陰イオンの価数である)(c)前記(a)成分及び(b)成分を溶解可能な溶媒を含むシリカ系被膜形成用組成物。

(もっと読む)

抵抗回路を有する半導体装置

【課題】高抵抗・高精度の抵抗素子からなる抵抗回路を提供する。

【解決手段】500Å以下に薄膜化した薄膜材料からなる抵抗素子の上にシリコン窒化膜などの絶縁膜を形成する。この窒化膜により抵抗素子に対するコンタクトホールの突き抜けを防止する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

配線の形成方法および形成装置

【課題】有機導電性材料を含む塗布組成物をプラスチック基板上に形成した後、高い電気電導度の配線を形成することができる配線の形成方法および形成装置を提供すること。

【解決手段】プラスチック基板上に有機導電性材料を含む塗布組成物が塗布されて配線パターンが形成された部材を準備し、少なくとも前記配線パターンに電磁波を照射してアニールし、有機導電性材料からなる配線を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】SOGで平坦化した半導体装置であっても水分による閾値変動を抑制した半導体装置を提供する。

【解決手段】SOG平坦化後にSOGを除去したMOSトランジスタ領域を単層配線とし、SOGを残した非MOSトランジスタ領域を多層配線とすることで、SOGを介したMOSトランジスタへの水分の影響が無くなり、MOSトランジスタの閾値変動を抑制できる。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を確保する。

【解決手段】基板と、基板に埋め込まれ、複数の開口部を有する絶縁膜と、複数の開口部内に位置する基板に設けられた複数のダミー拡散層20と、抵抗素子形成領域40において、平面視でダミー拡散層20と重ならないように絶縁膜上に設けられ、かつ第1方向に延伸する複数の抵抗素子10と、抵抗素子形成領域40において、絶縁膜上およびダミー拡散層20上に設けられ、かつ第1方向に延伸する複数のダミー抵抗素子12と、を備え、ダミー抵抗素子12は、平面視で、第1方向と基板に水平な面内において垂直な第2方向に並ぶ少なくとも二つのダミー拡散層20と重なっている。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

室温金属直接ボンディング

【課題】外からの圧力を用いることなく、低温または室温でウエーハーを貼り合わせる。

【解決手段】貼り合わされたデバイス構造であって、デバイスまたは回路に接続された第1の組の金属ボンディングパッドおよび第1の基板10上の金属ボンディングパッドに隣接する第1の非金属領域を有する第1の基板、デバイスまたは回路に接続された第1の組の金属ボンディングパッドに隣接する第2の組の金属ボンディングパッド、および第2の基板13上の金属ボンディングパッドに隣接する第2の非金属領域を有する第2の基板、および第2の非金属領域に対して第1の非金属領域を接触ボンディングさせることにより形成される第1と第2の組の金属ボンディングパッドの間の接触ボンディングされた界面を含むボンディングされたデバイス構造。第1と第2の基板の少なくとも一方は弾性的に変形され得る。

(もっと読む)

半導体記憶装置

【課題】コンタクトプラグ同士のショートや、コンタクトプラグ間の耐圧の低下を抑制する。

【解決手段】半導体記憶装置は、基板と、前記基板内において、前記基板の主面に平行な第1方向に延びるように区画された複数の素子領域と、前記第1方向に垂直な第2方向に延びるように形成された複数の選択ゲートSGと、前記基板上において前記選択ゲート間に設けられており、個々の前記素子領域上に形成された複数のコンタクトプラグCWを含むコンタクト領域とを備え、前記コンタクト領域は、N個(Nは2以上の整数)の前記コンタクトプラグが、連続するN本の前記素子領域上に、前記第1及び第2方向に非平行な直線上に並ぶように形成された部分領域を複数有し、前記Nの値は、前記部分領域ごとに異なる値に設定され、前記コンタクトプラグの各々は、楕円形又は長方形の平面形状を有し、前記第1方向に対し、長辺が傾けられて配置されている。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

141 - 160 / 1,392

[ Back to top ]