Fターム[5J042CA00]の内容

論理回路 (4,317) | 論理回路の構成要素 (2,115)

Fターム[5J042CA00]の下位に属するFターム

リレー

スイッチ (15)

ヒューズ (11)

トランス (1)

ダイオード (10)

トランジスタ (8)

FET (213)

FETとトランジスタ等の組合せ (2)

差動接続されたもの (18)

遅延回路 (34)

レジスタ (112)

ラッチ回路 (68)

フリップフロップ (127)

カウンタ (45)

D/A、A/Dコンバータ (25)

比較器 (55)

加算回路・引算回路 (51)

メモリー (350)

基本論理回路 (744)

ジョセフソン素子 (9)

Fターム[5J042CA00]に分類される特許

201 - 217 / 217

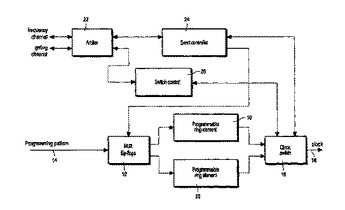

非同期回路設計に使用可能なプログラマブルロジックブロック

【課題】 非同期回路設計に使用可能なプログラマブルロジックブロックの提供。

【解決手段】 プログラミングの方式で、ロジックブロックに一般のデバイス処理の機能を具備させるのみならず、非同期プロトコルコミュニケーションを利用し、非同期デバイス設計の目的を達成する。こうして、非同期回路設計の便利性、正確さ、及び性能を増し、非同期回路の急速設計、検証の目的を達成する。

(もっと読む)

時分割多重処理可能なリコンフィギュラブル回路

【課題】 コンフィギュレーション切替に伴う時間損失とデータ入出力のレイテンシを低減した時分割多重処理可能なリコンフィギュラブル回路を提供する。

【解決手段】 本発明の時分割多重処理可能なリコンフィギュラブル回路は、所定数の整数倍の段数のパイプライン構造を有し、かつ供給される第1のコンフィギュレーション・データに応じて構成が可変な処理部を有する複数のプロセッサ要素と、複数のプロセッサ要素の入力および出力が総て接続され、入出力の間においてデータ転送を1クロックで行うネットワークと、処理部の各々に対し、前記所定数のタスク用に準備されたコンフィギュレーション・データを周期的に1クロックで切り換えて供給する切替手段から構成される。

(もっと読む)

帰還型断熱充電論理回路

【課題】 帰還型論理回路を断熱充電論理回路を用いて実現する。

【解決手段】 入力と出力を有し、その1つの出力を入力の1つとして帰還させる帰還型論理回路を断熱充電論理回路を用いて構成した帰還型断熱充電論理回路である。断熱充電論理回路を4段縦続接続(X,Z11,Z12,Z13)し、その内の初段の断熱充電論理回路Xに2つの入力を入力し、終段の断熱充電論理回路Z13の出力を初段の断熱充電論理回路の1つの入力として帰還させる。位相が90度づつずれた断熱充電電荷再利用型の4相クロックPCK1,PCK2,PCK3,PCK4を電源として、断熱充電論理回路X,Z11,Z12,Z13のそれぞれに印加して前段の断熱充電論理回路の出力を後段の断熱充電論理回路の入力に転送する。

(もっと読む)

半導体装置

【課題】 動的に回路構成を再構成可能な半導体装置にて、固定値データの記憶に要する記憶容量を低減できるようにする。

【解決手段】 コンフィグレーションデータを記憶するコンフィグレーションメモリ13Aと、コンフィグレーションデータに応じて回路構成を再構成可能な演算部22Aと、演算部に対して供給する固定値データを記憶する固定値用メモリ30とを備え、演算部に供給するコンフィグレーションデータと固定値データとを異なるメモリに記憶することで、コンフィグレーションメモリに固定値データを記憶するためのデータ領域を設定する必要をなくし、固定値用メモリから固定値データを読み出すための情報のみを記憶するだけで演算部に所定の固定値を供給することができるようにする。

(もっと読む)

電子デバイス

【課題】信号ルーティングのために第1または第2の垂直ラインを選択的に使用して、行シフト冗長において追加のドライバの必要性を小さくする。

【解決手段】第1または第2のスタガ形垂直ラインを通じて選択的に信号をルーティングするのに適する冗長アーキテクチャを含むプログラマブル・ロジック・デバイス(”PLD”)を提供する。1つの実施例は、ルーティング選択を決定するためのコンフィギュレーション・ロジックおよびプログラムを提供する。他の実施形態は、同じ行から動かされる垂直ラインの近接グループ化を提供する。さらに欠陥行の位置が分かった場合のスペア行の位置を提供する。

(もっと読む)

設定可能なデュアルMACおよびデュアルALUを有したデジタルシグナルプロセッサー

改良された性能を有するDSPアーキテクチャが記載される。例示アーキテクチャにおいて、DSPは2つのMACユニットと2つのALUを含み、ALUの一方は2つのMACユニットの一方のために加算器を交換する。このDSPはデュアルMAC/シンボルALU構成、シングルMAC/デュアルALU構成、またはデュアルMAC/デュアルALU構成において動作するように構成してもよい。この柔軟性は、DSPがさまざまなタイプの信号処理動作に対処することを可能にし、利用可能なハードウエアの利用を改善する。DSPアーキテクチャはさらに、クリティカルパスを分散し、より大きなスループットのためにより高いクロックスピードで動作を可能にするパイプラインレジスタを含む。  (もっと読む)

(もっと読む)

アップグレードおよび再設定可能なプログラマブル論理装置

プログラマブル論理装置およびこれら装置をプログラミングおよび/または再設定する方法が開示される。例えば、本発明の実施形態によれば、フラッシュメモリおよびSRAMを内蔵しまたフラッシュメモリおよび/またはSRAMをプログラミングするための多数のデータポートを含むプログラマブル論理装置が開示される。  (もっと読む)

(もっと読む)

プログラマブルで一時停止可能なクロック発生ユニット

互いに排他的に動作するように配置構成された2つのプログラマブル・リング発振器(10、20)と、プログラマブル可変遅延要素(図示せず)とを含むクロック発生回路。入力プログラミング・パターン(14)が発振回路に入力として供給され、プログラミング・パターン(14)は、クロック信号を発生させる必要のある周波数のシーケンスを表すデータを提供する。2つの発振器(10、20)の出力端がクロック・スイッチ(16)に接続され、発生されたクロック信号(18)がこのスイッチから出力される。周波数変更を求める要求が受け取られたときは、まず現在アイドル状態の発振器(20)が必要とされる次の周波数で活性化され、次いで現在動作中の発振器(10)の出力が、そのクロック信号がローのときに、ゲート制御されるようになる。次に、前にゲート制御されていた発振器(20)の出力が、その出力がローのときに、ゲート制御されないようにされ、次いで発振器(10)が非活性化される。  (もっと読む)

(もっと読む)

カスケード接続するDSPスライスを備えた集積回路

さまざまなサイズおよび複雑性を有するDSP回路を作成するためにカスケード接続され得るDSPスライスの列を備えた集積回路(IC)を記載する。各DSPスライスは、複数のオペランド入力ポートおよびスライス出力ポートを含み、それらのすべては、汎用のルーティングおよび論理リソースにプログラマブルに接続される。オペランドポートは、処理のためにオペランドを受取り、スライス出力ポートは、処理された結果を搬送する。各スライスは加えて、それぞれのスライス出力ポートに接続されてこの実施例では累積関数をサポートするフィードバックポートと、上流スライスの出力ポートに接続されてカスケード接続をサポートするカスケード入力ポートとを含む。  (もっと読む)

(もっと読む)

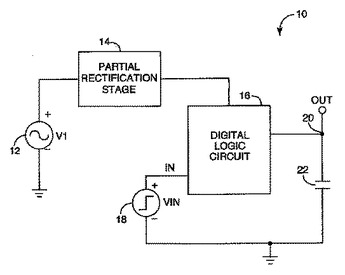

論理ゲートと部分整流段とを有する電子回路

論理回路は部分整流された交流(ac)波形により電力供給される。この波形はクリーンな一次dc電源信号を提供しないという意味で部分整流されている。代わりに実質的なac成分を含む波形で論理回路に電力供給することが可能である。部分整流ac波形をアモルファスまたは多結晶有機半導体、無機半導体またはそれら2つの組み合わせによる薄膜トランジスタを組み込んだ論理回路に適用し得る。  (もっと読む)

(もっと読む)

カオス演算モジュールのための装置、及び方法

動的に構成可能な論理ゲートは、第1の閾値基準信号を供給するように構成されたコントローラ(110)と、前記第1の閾値基準信号と少なくとも一つの入力信号とを合算することにより加算信号を生成するように構成された加算器(115)と、前記加算信号に非線形関数を適用するように構成されたカオス更新装置(105)と、第2の閾値基準信号と前記カオス更新装置(105)により処理された前記加算信号との差を求めることにより出力信号を決定するように構成された減算器(120)とを含む。論理ゲートは、前記複数の閾値基準信号の少なくとも一つを変更することに応答的な、複数の異なる論理ゲートの一つとして動作する。  (もっと読む)

(もっと読む)

コンフィギュレーション可能なロジック回路装置

本発明は、少なくとも1つのロジック信号切換のためのマルチプレクサを有するコンフィギュレーション可能なロジック回路装置に関する。マルチプレクサは1つ以上のデータ入力および1つ以上の制御信号入力を含む。少なくとも1つのマルチプレクサ(8,12,13)が、回路装置の1つ以上の外部の制御信号発生要素によって、制御入力に印加されるコンフィギュレーション信号により回路動作中にランタイム可変にて構成可能であり、かつデータ入力に印加されるロジック信号を回路動作中にランタイム可変にて転送する。  (もっと読む)

(もっと読む)

プログラマブルシステムオンチップ

プログラマブルシステムオンチップ集積回路デバイスは、プログラマブルロジックブロックと、不揮発性メモリブロックと、アナログサブシステムと、アナログ入出力回路ブロックと、デジタル入出力回路ブロックとを備えている。プログラマブル相互接続構造は、プログラマブル素子と相互接続導体を備えている。プログラマブルロジックブロックの入力及び出力、不揮発性メモリブロック、アナログ回路ブロック、アナログ入出力回路ブロック、及び前記デジタル入出力回路ブロックがプログラム可能に相互接続され得るように、プログラマブル素子の内の1つが、プログラマブルロジックブロック、不揮発性メモリブロック、アナログサブシステム、アナログ入出力回路ブロック、デジタル入出力回路ブロック、及び相互接続導体に接続される。  (もっと読む)

(もっと読む)

データ処理装置

本発明においては、アプリケーションを実行するための回路の少なくとも一部であるオブジェクト回路を動的に再構成可能な論理回路の一部にマッピングするためのオブジェクト回路情報(23)と、オブジェクト回路に接するインタフェース回路を論理回路にマッピングするためのインタフェース回路情報(24)と、インタフェース回路において実現する境界条件(26)とを含むアーキテクチャコード(20)を使用する。

本発明のデータ処理装置は、アーキテクチャコード(20)を取得するロードユニットと、アーキテクチャコードのオブジェクト回路情報(23)及びインタフェース回路情報(24)により、論理回路領域にオブジェクト回路とインタフェース回路をマッピングするマッピングユニットと、アーキテクチャコードの境界条件(26)にしたがってインタフェース回路を制御する動作制御ユニットを有する。

(もっと読む)

スキュー制御を有するクロックジェネレータ

クロック発生をもたらすためのシステムおよび方法が開示される。一実施例によれば、構成可能でインシステムプログラマブルな、柔軟なスキュー制御アーキテクチャを含むクロックジェネレータチップが与えられる。クロックジェネレータチップはさらにプログラム可能な入力回路、プログラム可能な出力回路を与えることができ、JTAGバウンダリスキャンを可能にし得る。  (もっと読む)

(もっと読む)

データ転送方法、データ転送回路、出力回路、入力回路、半導体装置、電子装置

データ転送回路は、nビット(nは2以上の整数)の第1の2値電圧データを2n値の多値電流データに変換して、単一のデータ転送線に出力する電圧電流変換回路を備えている。電流比較回路は、前記データ転送線上の前記多値電流データを(2n−1)ビットの2値電流データに変換し、電流電圧変換回路は、前記(2n−1)ビットの前記2値電流データを(2n−1)ビットの第2の2値電圧データに変換する。計数回路は、前記(2n−1)ビットの前記第2の2値電圧データから前記nビットの前記第1の2値電圧データを復元する。 (もっと読む)

SoCのための再設定可能なファブリック

ラッパーの動作機能を変化させることができ、したがって設計されたSoCの動作機能を変化させることができる機能再設定モジュール(FRM)を有しているラッパーを使用することによって、並外れて効果的なSoC設計が達成される。コア+ラッパーの組み合わせの一実施の形態は、ラッパー内の別個の入力セルおよび出力セル、ならびに別個のFRMを有している。他の実施の形態においては、入力セルおよび出力セルをFRM内に組み込んでもよい。FRMは、例えばフィールド・プログラマブル・ロジック・アレイ(FPLA)によって実装することができる。さらなる進歩が、SoCの種々の要素を相互接続している信号経路ネットワークに何本かの予備のリードを設けることによって達成される。  (もっと読む)

(もっと読む)

201 - 217 / 217

[ Back to top ]