Fターム[5J042CA00]の内容

論理回路 (4,317) | 論理回路の構成要素 (2,115)

Fターム[5J042CA00]の下位に属するFターム

リレー

スイッチ (15)

ヒューズ (11)

トランス (1)

ダイオード (10)

トランジスタ (8)

FET (213)

FETとトランジスタ等の組合せ (2)

差動接続されたもの (18)

遅延回路 (34)

レジスタ (112)

ラッチ回路 (68)

フリップフロップ (127)

カウンタ (45)

D/A、A/Dコンバータ (25)

比較器 (55)

加算回路・引算回路 (51)

メモリー (350)

基本論理回路 (744)

ジョセフソン素子 (9)

Fターム[5J042CA00]に分類される特許

161 - 180 / 217

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

半導体集積回路

【課題】ダイナミック・リコンフィギュラブル・プロセッサにおいて、小さいハードウェア規模で構成情報を効果的に格納し、処理性能を向上させる機構を提供する。また、柔軟性と高い動作周波数を両立する実装の容易な状態遷移機構を提供する。

【解決手段】構成情報を階層的に記憶し、演算部60での処理を停止させることなく、以後の処理に必要な構成情報を第1の記憶領域(構成情報バッファ1000)から第2の記憶領域(構成情報レジスタ1800,2300)へ予め転送するように構成する。また、複数の状態遷移モードにより、異なる状態遷移条件に対する条件判定処理を実行するように構成する。

(もっと読む)

制御装置

【課題】 プログラマブルデバイスを用いつつ、電源投入後、早期に制御を開始することを可能とした制御装置を提供する。

【解決手段】 制御回路100は、プログラマブルデバイスであるFPGA1と、FPGA1の一部の処理内容を共通して実行することが可能なベース処理IC3を有している。起動時にコンフィグレーションROM10に内蔵されたコンフィグレーション情報をFPGA1へと書き込んで、コンフィグレーションを完了するまでの間は、ベース処理IC3を用いて制御を行う。さらに、コンフィグレーション後もコンペアIC8がベース処理IC3とFPGA1の制御出力を比較することで、コンフィグレーション情報の状態をチェックする。

(もっと読む)

混合された相互接続リソースを備えたFPGAアーキテクチャ

FPGAは、相互接続リソースが2つのグループに分けられたプログラム可能相互接続構造を含む。相互接続リソースの第1のサブセットは高スピードに対して最適化される。相互接続リソースの第2のサブセットは低電力消費に対して最適化される。実施例によっては、第1および第2のサブセットのトランジスタは異なるしきい値電圧を有する。スピードに対して最適化されている第1のサブセットのトランジスタは、低電力消費に対して最適化される第2のサブセットのトランジスタより低いしきい値電圧を有する。しきい値電圧の差は、異なるドーピングレベル、異なる電圧レベルにバイアスされた井戸を使用することによって、または他の既知の手段を使用することによって実現可能である。実施例によっては、相互接続リソースの第1のサブセットは、第2のサブセットより高い電圧レベルに結合されたバッファを含む。実施例によっては、第1のサブセットは、第2のサブセットのものより大きいトランジスタを使用して製造されたバッファを含む。  (もっと読む)

(もっと読む)

レベル生成装置

【課題】 100V超の高耐圧素子を用い、かつ容量性負荷を駆動させる場合でも、ハイレベルとミドルレベルの間の電位差を高耐圧素子の耐圧の範囲内で、自由に設定することを目的とする。

【解決手段】 各ドレインが出力端子4に接続された、ハイレベルトランジスタ6とミドルレベルトランジスタ7とロウレベルトランジスタ8の3個のトランジスタを有し、それぞれオン時にハイレベル、ミドルレベル、ロウレベルを出力する。さらにミドルレベルトランジスタ7と出力端子4の間に、カソードが出力端子4に接続された逆流防止ダイオード29を備える。

(もっと読む)

半導体検査装置

【課題】FPGAなどのハード構成をプログラマブルに構築可能なコンフィギュアラブルデバイスを用いて構成された半導体検査装置において、複数の被測定デバイスに対して最適なハード構成を構築して装置の汎用性を向上させる。

【解決手段】コンフィギュアラブルデバイスであるFPGA12と、FPGA12をコンフィギュレーションするためのインターフェイスと、FPGA12のハード構成を規定するプログラムが書き込まれ、装置本体Aの外部に配置され、インターフェイスを介して接続される記憶素子21とを備える。記憶素子21からFPGA12にコンフィギュレーションするプログラムをフレキシブルに変更することで、装置本体Aを被測定デバイスBの検査に適したハード構成にて動作させる。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

マルチプライヤを含んだプログラマブルロジックデバイスならびにそのリソース使用を低減するための構成

【課題】リソースの使用を低減するよう構成されるマルチプライヤ回路を備えたプログラマブルロジックデバイスの提供。

【解決手段】専用のマルチプライヤ回路を有するプログラマブルロジックデバイスにおいて、通常はデバイスの検査に使用されるスキャンチェーンレジスタのいくつかがマルチプライヤの入力に近接して配置される。スキャンチェーンレジスタは入力レジスタとAND演算され、1および0のテンプレートでロードできる。これにより、例えば最も重要でないビットに0がロードされ残りのビットに1がロードされた場合にサブセット乗算が可能になる。マルチプライヤは他の構成要素と共にブロック構成され、有限インパルス応答(FIR)フィルタとして構成可能になる。この構成においてフィルタ係数をロードするためスキャンチェーンレジスタを使用し得、デバイス上の限られたロジックおよびルーティングリソースの使用を回避する。

(もっと読む)

放射線に耐性のある、スタティックRAMのフィールドプログラマブルゲートアレイにおける誤りの検出と訂正の方法及び装置

本システムは、論理モジュールと、論理モジュールと共に結合された配線資源を持った、放射線に耐性のあるプログラマブル論理素子を備える。構成データを提供する構成データラインは、論理モジュールと配線資源とを制御する。構成データラインに結合される誤り訂正回路は、単一事象の異常(SEU)によって起こり得る構成データ内の誤りを分析して訂正する。本システムは、また、プログラマブル論理素子をプログラムするための構成データを持ったプログラマブル論理素子内の誤りを訂正する方法を備える。本方法は、構成データのバックグラウンド読み取り段階を備える。次に、構成データは、誤りに対して分析される。最後に構成データは、訂正されて、もし誤りが見付かれば、構成データは書き換えられる。  (もっと読む)

(もっと読む)

出力可変回路

【課題】 製品の仕様に合わせてプルアップ、プルダウン、又はハイインピーダンスに自由に設定できる出力可変回路を提供する。

【解決手段】 所定のプログラムをダウンロードすることによって所定の出力を設定できるデバイスと、一端が該デバイスの出力に接続され他端が配線に接続される抵抗を有する出力可変回路であって、前記デバイスは、該デバイスにダウンロードされるプログラムによって出力がハイ(H)、ロー(L)、又はハイインピーダンスに設定される構成を備え、前記出力がハイ(H)に設定された場合には前記抵抗をプルアップ抵抗として動作させ、前記出力が(L)に設定された場合には前記抵抗をプルダウン抵抗として動作させ、前記出力がハイインピーダンスに設定された場合には前記抵抗の効果を無効とし、プルアップ及びプルダウンとして動作させない。

(もっと読む)

プログラマブルロジックセルのアレイを有する電子回路

本電子回路は、マルチビットオペランドモードおよび多重化モードで動作するように構成することのできる複数のプログラマブルロジックユニットを備えた、プログラマブルロジックセルを有する。プログラマブルロジックユニットは、入力回路と出力回路との間に並列に結合される。マルチビットオペランド処理モードでは、入力回路は、複数のロジック入力端のうちの異なる複数のロジック入力からのロジック入力信号を複数のプログラマブルロジックユニットに供給するように構成される。複数のプログラマブルロジックユニットは、少なくともマルチビットオペランドモードではキャリーチェーンに沿った複数の連続的な位置に結合されて、キャリーチェーンからの複数の桁上げ信号を処理する。出力回路は、マルチビットオペランドモードで、複数のプログラマブルロジックユニットからの複数の出力を並列に渡す。複数のプログラマブルロジックユニットは、複数の同じ構成ビットを共有する複数のルックアップテーブルを有する。複数のプログラマブルロジックユニットはまた、多重化動作モードで動作するように構成されたときにおいては、複数の受領済み入力信号のうちの1つを渡すためのマルチプレクサを有することもできる。  (もっと読む)

(もっと読む)

電圧制御オシレータ及びこれを用いる電子システム

【課題】最大出力周波数が受動素子により制限されない電圧制御オシレータ及びそれを用いた電子システムの提供。

【解決手段】電圧制御オシレータは、第1のXOR結果を第1の出力信号に変換する第1の変換器、第2のXOR結果を第2の出力信号に変換する第2の変換器、第1の入力信号と第2の入力信号に基づいてXOR論理操作を行って第1のXOR結果を出力する第1のXOR論理ユニット、及び第1の出力信号と参考電圧に基づいてXOR論理操作を行って第2のXOR結果を出力する第2のXOR論理ユニットを含む。また、電圧制御オシレータは、更に、第1の出力信号と第2の出力信号に基づいてXOR論理操作を行って第3のXOR結果を出力する第3のXOR論理ユニットを含むことができる。

(もっと読む)

三値論理関数回路及び多値論理関数回路

【課題】 33^2=19683種類存在する全ての二変数三値論理関数回路を実現するために必要となる基本回路の種類を著しく削減するとともに、スイッチング時間の非対称性も著しく小さくすることができる三値論理関数回路を提供する。

【解決手段】 二変数三値論理演算を行う三値論理関数回路は、第1の入力aを構成する3つの論理値−1,0,1に応じて、一変数三値論理関数回路C1,D1,C2,D2,C3,D3によって3つのトランスファーゲートT1,T2,T3を導通又は遮断し、第2の入力bに接続される3つの一変数三値論理関数回路B1,B2,B3の出力を選択する。

(もっと読む)

プログラマブル論理デバイス

目的論理関数に応じ、論理関数メモリ間の入力線数、レイル数を変化させ、メモリ容量を必要最小限に抑えて最適化設計できるプログラマブル論理デバイスである。論理関数メモリ(4)を直列に順序配列し、LUTを記憶させる。外部入力線から、各論理関数メモリ(4)への入力変数を入力する。二つの論理関数メモリ(4)間において、接続メモリ(6)が記憶する接続情報に従って、接続回路(5)が前段の論理関数メモリ(4)の出力線又は外部入力線と後段の論理関数メモリ(4)の入力線との接続を行う。目的論理関数に合わせて、接続情報を書き換えれば、接続回路を再構成し、入力線数、レイル数を変化させることができる。レイル数と入力線数の比を論理関数に合わせて最適化し、メモリ容量を必要最小限に抑えることが可能となる。  (もっと読む)

(もっと読む)

プログラマブル論理回路

【課題】 専用の復号回路を用いることなく、暗号化されたコンフィギュレーションデータにより設計情報の秘匿性を確保可能なプログラマブル論理回路を提供する。

【解決手段】 暗号化されたコンフィギュレーションビットストリームは、コンフィギュレーションチェーン6を通過しながらアレイ状のPE4に形成された各コンフィギュレーション回路2のレジスタ(図示せず)にロードされる。このとき、入力されたコンフィギュレーションビットストリームはコンフィギュレーションチェーン6を通過する過程で値が変化するので、アレイ状に配列されたPE4の中で目的のPEに達する時点でどのような値になるかについて設計者以外は知り得ない。したがって、所望の2箇所におけるコンフィギュレーション回路2の間に帰還回路40aを設けてデータを帰還すれば、データが攪拌されるので、第三者がコンフィギュレーションデータを推定することは困難になる。

(もっと読む)

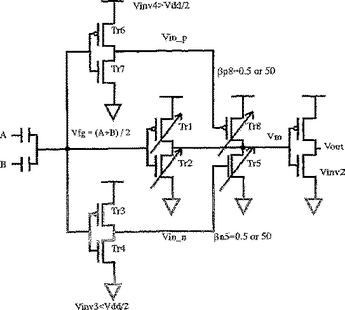

スピン依存伝達特性を有するトランジスタを用いた再構成可能な論理回路

不揮発に再構成可能な論理回路を構成する。スピンMOSFETを用いたCMOS構成による再構成可能な論理回路である。スピンMOSFETであるTr1、Tr2、Tr5、Tr8の磁化状態によりそれぞれのトランジスタの伝達特性を変化させることでAND/OR/XOR/NAND/NOR/XNOR/“1”/“0”の全2入力対称関数が再構成可能である。不揮発かつ少素子数で論理機能を構成できるため、チップ面積の縮小化が可能であり、高速・低消費電力動作が期待できる。  (もっと読む)

(もっと読む)

集積回路のデバッグ方法、デバッグプログラム

【課題】 メモリ容量を増大させることなく、かつ、迅速に、動的再構成可能LSIにおける現在のコンフィグレーションを特定する。

【解決手段】 動的再構成可能LSIのプログラムの実行を設定にしたがって停止させた状態で、主メモリに記憶されたコンフィグレーションデータおよびそのソースデータ、並びに、コンフィグレーションメモリの実行バンクに格納されたコンフィグレーションデータを取得するデバッガ24は、プロセッサコアによる他律ダイナミックリコンフィグレーションの発生時に、実行バンク(バンク0)に格納されるべきコンフィグレーションの供給元のバンク名を静的変数として主メモリ60に記憶し、プログラムの実行停止時に、マトリクス32からバンク由来値を取得して、静的変数とバンク由来値とを比較し、これらが不一致の場合に、自律ダイナミックリコンフィグレーションが発生したと判断する。

(もっと読む)

量子回路及び複数の量子ビット素子間の量子もつれ状態制御方法

【課題】固体量子ビット素子を量子コンピュータに用いる場合に、任意の2つの量子ビット素子間の結合を異なる周波数をもつマイクロ波パルス列で行うことにより、従来量子ビット素子間それぞれに必要であった専用の結合用回路を不要とし、固体量子ビット素子の実装及び量子ビット間の量子演算を容易にする。

【解決手段】複数の超伝導固体量子ビット素子Q1,Q2,…,Qnと、複数の超伝導固体量子ビット素子間に相互作用を生じさせるための超伝導レゾネータRと、複数の超伝導固体量子ビット素子の状態及び超伝導レゾネータの状態を制御するためのマイクロ波パルスを発生するマイクロ波ラインLとを備える。

(もっと読む)

ロジック装置およびロジックシステムならびにデータ読み出し制御方法

【課題】汎用の不揮発性メモリを流用可能とする。

【解決手段】ロジック装置1は、コンフィグレーションデータおよびプログラムデータを、汎用メモリインターフェースを介して、フラッシュROM2から読み出すロジック装置であって、リセット解除されると、データ領域21のアクセスアドレスを生成し、領域21から読み出されたプログラムデータによって動作するCPUコア部11と、フラッシュROM2のリセット解除よりも遅延してCPUコア部11をリセット解除するロジックリセット生成部12と、フラッシュROMリセット解除時からCPUコア部リセット解除時までの期間中に、コンフィグレーション領域22のアクセスアドレスを生成するコンフィグレーションアドレス生成部14と、上記期間中に、領域22から読み出されたコンフィグレーションデータをラッチするコンフィグレーションレジスタ19とを備える。

(もっと読む)

プログラマブル・ロジック・デバイス、情報処理装置、プログラマブル・ロジック・デバイスの制御方法

【課題】 プログラマブル・ロジック・デバイスに用いられる構成情報の異常の早期発見による予防保守を実現する。

【解決手段】 プログラマブル・ロジック・デバイス10に備えられたコンフィギュレーション回路20に、不揮発性メモリ60からコンフィギュレーションデータS4を読み出してユーザ論理の構築を行うコンフィギュレーション用メモリ制御回路24と、コンフィギュレーション操作完了後に定期的に不揮発性メモリ60からコンフィギュレーションデータS4を読み出してエラーチェックを行うメモリ監視用メモリ制御回路21を備えた。コンフィギュレーション操作完了後の不揮発性メモリ60の放置期間における当該不揮発性メモリ60内のコンフィギュレーションデータS4の異常を、次回のコンフィギュレーション操作の実行に先立って早期に発見でき、予防保守が可能になる。

(もっと読む)

161 - 180 / 217

[ Back to top ]