Fターム[5J500AC00]の内容

増幅器一般 (93,357) | 目的、効果 (9,357)

Fターム[5J500AC00]の下位に属するFターム

補償 (601)

出力直流電圧の変動対策、調整 (444)

素子のバラツキの影響低減 (230)

寄生素子の影響低減 (51)

アーリー効果の低減 (13)

歪低減(直線性改善を含む) (1,554)

交流出力の正負のバランス改善 (17)

ダイナミックレンジの改善 (330)

利得向上 (116)

電力効率向上、低消費電力化、節電 (1,415)

低電源電圧化 (139)

雑音低減 (966)

発振防止 (146)

保護(例;負荷の保護) (418)

その他の信頼性の向上 (124)

周波数特性の変更 (618)

入力インピーダンス特性の変更 (56)

出力インピーダンス特性の変更 (77)

整合(インピーダンス整合) (173)

不整合 (5)

誘導性負荷の駆動 (8)

容量性負荷の駆動 (49)

バイアス回路の変形、改良 (167)

ミラー比の変更 (5)

高速起動 (50)

放熱、冷却 (30)

増幅器自体の低価格化 (122)

増幅率の精度の向上 (104)

フェイルセーフ (4)

IC化容易 (84)

回路の簡素化、小型軽量化 (745)

増幅器自体の試験 (32)

増幅器自体の調整 (136)

他回路との兼用化 (24)

Fターム[5J500AC00]に分類される特許

201 - 220 / 304

四端子二重絶縁ゲート電界トランジスタを用いたCMOS増幅器、それを用いた多入力CMOS増幅器、高利得多入力CMOS増幅器、高利得高安定多入力CMOS増幅器および多入力CMOS差動増幅器

【課題】 増幅器の入力インピーダンスに制限を加えず、入力オフセット電圧Vofsによる増幅段数の制限をなくし、信号入力経路に悪影響を及ぼすことがないようにした四端子二重絶縁ゲート電界トランジスタを用いたCMOS増幅器、それを用いた多入力CMOS増幅器、高利得多入力CMOS増幅器、高利得高安定多入力CMOS増幅器および多入力CMOS差動増幅器を提供することにある。

【解決手段】 P形およびN形の四端子二重絶縁ゲート電界効果トランジスタを用い、それぞれのドレインを共通接続して出力端子とし、それぞれの第一のゲートを接続して第一の入力端子とし、それぞれの第二のゲートを接続して第二の入力端子とするCMOS増幅器を構成する。このCMOS増幅器を複数個用い、その各出力端子を接続して一つの出力端子とし、各CMOS増幅器の入力端子は同複数個の2倍の独立した入力端子として用いて多入力CMOS増幅器を構成する。

(もっと読む)

ミュート回路

【課題】入出力インターフェースにおいてミューティング用MOSトランジスタの耐圧により制限される電源電圧範囲を拡大できるミュート回路を提供することを目的とする。

【解決手段】正負の信号が出力される出力端子10のミューティング用NchMOSトランジスタ1と、このトランジスタ1のゲートに印加される電圧を切換え、トランジスタ1のオン/オフを制御するミュート切換回路3を備え、トランジスタ1のバックゲートを、出力端子10と所定のマイナス電位VSSとの間に直列に接続される抵抗R1と抵抗R2の抵抗分割でバイアスする。この回路構成によれば、トランジスタ1がオフされることによるミュートオフ時に、トランジスタ1のバックゲート電圧が、出力端子10に出力される信号の変動に伴い変動され電源電位VCCの範囲に抑えられることにより、トランジスタ1の耐圧を電源電位VCCの範囲に抑えることができる。

(もっと読む)

平衡出力増幅装置

【課題】音質を損なうことなく出力電圧のレベルを抑えることができ、3端子ヘッドホン接続時でもセパレーション性能を確保することができる平衡出力増幅装置を提供する。

【解決手段】入力信号SLを非反転増幅して出力する演算増幅器1と、入力信号SLを反転増幅して出力する演算増幅器2と、入力信号SRを非反転増幅して出力する演算増幅器3と、入力信号SRを反転増幅して出力する演算増幅器4とを備え、抵抗R1及びR5を介して演算増幅器2と逆相出力端子10とが接続され、抵抗R7を介して演算増幅器1と正相出力端子9とが接続され、抵抗R2及びR6を介して演算増幅器4と逆相出力端子12とが接続され、抵抗R8を介して演算増幅器3と正相出力端子11とが接続される平衡出力増幅装置。

(もっと読む)

アナログ入力信号処理回路

【課題】入力フィルタ特性と入力ゲインを個別に調整可能なアナログ入力信号処理回路を提供する。

【解決手段】可変アナログ信号源100a・100bが発生する信号電圧は、ゲイン調整回路10a・10bとスイッチドキャパシタフィルタ回路20a・20bとアナログ比較回路30a・30bを介してマイクロプロセッサ110に入力される。プログラムメモリ111と協働するマイクロプロセッサ110は、可変周期・可変デューティの制御信号パルス列CNTa・CNTbを発生し、該制御信号パルス列CNTa・CNTbの周期によりフィルタ特性が調整され、パルスデューティによってゲインが調整される。アナログ比較回路30a・30bの比較基準電圧31a・31bが固定値であっても、ゲイン調整回路10a・10bのゲインを調整することにより見かけ上の比較基準電圧の変更調整が行える。

(もっと読む)

アナログ・アイソレーション回路

【課題】 一般部品を使用して簡易な回路でアナログ信号を絶縁できるアナログ・アイソレーション回路を提供する。

【解決手段】接地系統が異なる電源系統の回路を、コンデンサカップリングを用いて接続した。1次電源系のアナログ信号を2つのコンパレータと三角波を用いてPWM変調する。PWM変調波はカップリングコンデンサを経由して2次電源系の回路へ伝達される。その後コンパレータと低域通過フィルタを用いて復調し、1次電源系のアナログ信号を再生する。

(もっと読む)

スイッチ回路

【課題】 PINダイオードをスイッチ素子として用いた従来のスイッチ回路においては、バイアス供給回路とのアイソレーションが不充分であった。

【解決手段】 スイッチ回路1は、電力増幅回路70の負荷整合回路80を切り換えるスイッチ回路である。このスイッチ回路1は、負荷整合回路80に一端が接続された容量素子12と、一端が容量素子12の他端に接続されるとともに、他端が接地されたPINダイオード14と、容量素子12とPINダイオード14との間の経路に一端が接続された抵抗素子16と、抵抗素子16の他端に接続されるとともに、他端が接地された容量素子18と、抵抗素子16と容量素子18との間の経路に一端が接続された抵抗素子22と、抵抗素子22と並列に接続されたFET24と、出力端が抵抗素子22の他端に接続され、バイアス供給回路を構成するインバータ26と、を備えている。

(もっと読む)

ショート検出回路

【課題】

本発明は、アンプにおけるショートの高精度な検出と誤検出の防止とを両立できるようにする。

【解決手段】

本発明は、電流検出部12により電源電流I1が上限電流値を超えたことを検出して検出信号SDを「High」レベルで出力すると共に、電圧検出部13により出力電圧Voutが上限電圧値を超えたことを検出した場合に検出信号SDを強制的に「Low」レベルに切り換えることにより、スピーカ100に大電流が流れたときに電流検出部12による検出結果を電圧検出部13により無効化してショートの誤検出を防止できると共に、実際にショートされた際には電圧検出部13が電流検出部12による検出結果を有効化して検出信号SDを「High」レベルで出力することができ、これによりアンプ装置10に正確な保護動作をさせることができる。

(もっと読む)

演算増幅器

【課題】

入力抵抗素子の抵抗値が可変の演算増幅器において、入力端子に接続されたC結容量と前記入力抵抗素子とでハイパスフィルターが構成された場合に、前記ハイパスフィルターのカットオフ周波数を一定にできるようにする。

【解決手段】

基準電源106からの基準電圧を差動入力増幅器101の一方の入力端子に入力する。抵抗値が可変で一方の端子が差動入力増幅器101の他方の入力端子に接続された入力抵抗素子、および前記入力抵抗素子の他方の端子と直列に接続された容量素子によってハイパスフィルターを構成する。そして、前記入力抵抗素子の前記他方の端子に接続され、前記入力抵抗素子の抵抗値に応じて、オンオフが切り替わるアナログスイッチを介して、電流源107から前記入力抵抗素子に一定の電流を出力する。

(もっと読む)

ミュート回路

【課題】 音声出力装置のミュート動作を制御するミュート回路において、通常動作の途中でのミュートオンからの復帰に時間がかかる。

【解決手段】 通常動作時のミュートオンは、スイッチSWをオンしてコンデンサCmを放電し、トランジスタQ8のベース電圧Vin1をトランジスタQ9のベース電圧Vref2より低くすることにより行われる。Q8のベースにダイオードD1を接続し、Vin1がクランプ基準電源の供給する電圧Vref1より下がらないようにクランプする。これにより、SWをオフした後の再充電によりVin1がVref2を越えるまでの時間が短縮され、ミュートオンからの復帰の迅速化が図られる。

(もっと読む)

光受信装置および自動利得制御方法

【課題】伝送システムの周波数特性の歪みを取り除き、低コストで操作性が良いAGC(Automatic Gain Control)制御ができる光受信装置および自動利得制御方法を提供すること。

【解決手段】光通信システム10の光受信装置20は、光信号を電気信号に変換する受光素子31と、信号を増幅する増幅器(32、34、37)と、チャンネル周波数の電力値を測定するレベルスキャン回路41と、利得制御電圧Vc1〜Vc4を決定するAGC制御回路43と、利得制御電圧で周波数特性の歪みを補正するイコライザ35やアッテネータ(33、36)とを含んでいる。利得制御電圧は、レベルスキャン回路41で測定された電力値に基づき決定される。AGC制御回路43は、チャンネル周波数掃引によりピーク電力値を検出して、伝送路の周波数特性を判定する。自動利得制御方法は、レベルスキャン回路41、ピーク電力値検出回路42およびAGC制御回路43により行われる。

(もっと読む)

パルスモード増幅器の2ピーク電力レベル制御方法および装置

パルスモードで動作する増幅器の少なくとも2つのピーク電力レベルを制御する装置であって、少なくとも以下の要素、すなわち、

・少なくとも1個の増幅器(1)および増幅器(1)に矩形波信号を供給するのに適した1つの処理装置(6)を含む第1の増幅段、

・少なくとも1個の増幅器(7)および施された変調の形状と概ね同一の形状を有する信号を供給するのに適した1つの処理装置(9)を含む第2の増幅段、

を少なくとも含む変調前段と、

・増幅サブシステムの出力における信号の少なくとも一部をサンプリングして、ビデオ増幅器(22)へ送信するカプラおよび検知器(11)、

・増幅器(20)向けに変調信号を生成するのに適したピーク検知器(24)およびレベル識別器(25)、

・増幅器用の電力供給手段(21、22、23)、

を少なくとも含む電力ロック段とを含むことを特徴とする装置。

(もっと読む)

集積回路

【課題】従来の発振器用集積回路では、低振幅の出力波形を要求された場合に、出力増幅回路トランジスタ対のゲート・ソース間電圧が十分に確保できず、大きな負荷を駆動できないという問題があった。

【解決手段】 出力増幅回路112のPチャネルトランジスタ110およびNチャネルトランジスタ111のゲートを、コンデンサ106および107により発振回路104の出力に交流的に結合するとともに、抵抗108および109を介してPチャネルトランジスタ110のゲートはGND電位に、Nチャネルトランジスタ111のゲートは電源電位にバイアスされていることにより、これらのトランジスタのゲート・ソース間電圧が充分に確保され、大きな負荷を駆動できるようにしたことを特徴とする集積回路。

(もっと読む)

耐磁場性増幅器および同左を使用する無線トランシーバ

増幅器ステージ、シングルエンデッド出力差動増幅器ステージ、ならびに第1の遅延ラインおよび第2の遅延ラインを有する耐磁場性増幅器。増幅器ステージは、一対の差動入力端子、および一対の差動出力端子を有する。シングルエンデッド出力差動増幅器ステージは、一対の差動入力端子および出力端子を含む。第1の遅延ラインおよび第2の遅延ラインは各々、出力端子を有する。別の実施形態において、本発明は、接合点で直列に接続され、かつ非誘導的に巻かれて磁気変化度から誘発された電流をキャンセルする2つのコイルを含む、磁気変化度キャンセレーション遅延ラインに関する。  (もっと読む)

(もっと読む)

光受信器

【課題】 交流結合用容量素子の後段における受信信号を検波する構成を有する光受信器において、入力断の判定時間を短縮するとともに該判定時間を容易に変更でき、且つ受信信号からクロック周波数を抽出できない場合でも入力断を判定できる光受信器を提供する。

【解決手段】 光受信器1は、交流結合用の容量素子9a,9bの後段に接続され受信信号Sp2,Sn2の入力断を検出する受信信号監視回路4を備える。受信信号監視回路4は、受信信号Sp2,Sn2に含まれる各ビットの論理値を参照しつつ所定時間をカウントし、該論理値が所定時間連続して同値であった場合に無信号アラーム信号LOSCIDを生成する無信号アラーム生成部5と、所定時間をカウントするためのクロック信号CLを無信号アラーム生成部5へ提供するクロック発生部7とを有する。

(もっと読む)

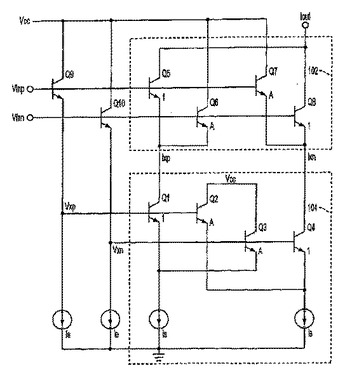

広帯域2乗セル

入力電圧に応答して、対応する電流を発生させる第1の回路と、第1の回路によって発生された電流および入力電圧に応答して、入力電圧の2乗に対応する出力電流を発生させる、好ましくは絶対変調器回路の形態の第2の回路とを備える2乗セルを提供する。一実施形態において、第1の回路は絶対値電圧−電流変換器を含み、別の実施形態においては、第1の回路は線形電圧−電流変換器を含む。温度ならびに広い入力電圧範囲および周波数から独立したセルの正確な2乗性能を向上させるための手法を呈示する。  (もっと読む)

(もっと読む)

フィードフォワード増幅器

【課題】主増幅器や誤差増幅器の群遅延時間の短縮を実現することができるフィードフォワード増幅器を得る。

【解決手段】歪み抽出部を構成する主増幅器4または歪みキャンセル部を構成する誤差増幅器2の少なくとも一方に、負の群遅延時間を有する回路1または素子を前置または後置する。また、負の群遅延時間を有する回路1として、(A)コンデンサ、インダクタおよび抵抗を用いた直列共振回路8を、信号線路に対して並列接続すると共に、所望の周波数近傍で共振させる負の群遅延時間を有する回路、または(B)コンデンサ、インダクタおよび抵抗を用いた並列共振回路を、信号線路に対して縦続接続すると共に、所望の周波数近傍で共振させる負の群遅延時間を有する回路の少なくとも1つを用いる。

(もっと読む)

遅延時間検出方法

【課題】プリディストーション歪補償を行うためのフィードバック信号の遅延時間検出を、経年変化等による大きな遅延時間変化が生じたときでも、オンライン状態のままで効率よく行えるようにする。

【解決手段】粗遅延検出部102による1サンプル単位での粗遅延検出と、微遅延生成器104、遅延器105、106、相関器107、108、加算器109及び遅延検出制御部103による微遅延検出をともにオンラインで行えるようにし、常時は微遅延検出とその検出値による微遅延補正のみを繰り返し実行し、微遅延検出ができないときだけ粗遅延検出を行って粗遅延補正の更新を行う。こうして、大きな遅延時間変化のため粗遅延検出が必要となったとき、粗遅延検出精度は微遅延検出のそれよりも低いので少ない処理時間で検出、補正の更新がオンラインで可能になる。

(もっと読む)

Dクラスオーディオ増幅器の非同期性BTL設計

【課題】

Dクラスオーディオ増幅器の非同期性BTL設計を提供する。

【解決手段】

本発明のDクラスオーディオ増幅器の非同期性BTL設計は、二つの独立した信号ルートを採取し、それぞれ、PWM変調器、プレドライバ、及び、パワーMOS回路、からなる。二つの独立した信号ルートは、それぞれ、PWM変調器により、入力信号を受信し、その後、出力信号は、パワーMOS回路を経て、共同で、スピーカーを駆動する。二つのPWM変調器に入力される同期化信号はなく、且つ、二つのパワーMOS回路は、フィルター前、及び/又は、フィルター後の信号を、それぞれ、二つのPWM変調器に、フィードバックし、互いに影響しない。本発明は、公知技術の同期化設計を省略すると共に、BTLが必要な二つのプッシュプル式信号を、それぞれ、処理し、二つの信号を互いに影響させず、しかし、最後に、共同で、スピーカーを駆動する。

(もっと読む)

電力増幅器および通信装置

【課題】 増幅歪みの補償の調整範囲が広い電力増幅器およびこれを用いた通信装置を提供する。

【解決手段】 可変インピーダンス回路30は、バイポーラトランジスタ104のベースと接地ノードとの間に接続されており、キャパシタ111と、MOSFET112とを含む。キャパシタ111は、直流成分に対して開放であるように作用する。MOSFET112は、交流成分に対するインピーダンスを変化させる。ベース電圧生成部40の抵抗109,110は、バイポーラトランジスタ104のベースにかかるバイアスを設定する。すなわち、ベース電圧生成部40は、電圧端子105から供給される動作電圧VBを抵抗109と抵抗110との比で分割することで、バイポーラトランジスタ104のベース電圧を生成する。

(もっと読む)

電力増幅器を管理する方法及び装置

【課題】トラフィックパターン及び電力出力能力を動的に整合させることによって増幅器の電力を最適化する電力管理手法を提供する。

【解決手段】本発明の電力増幅器を管理する方法においては、電力増幅器における複数の増幅器群のうち最も長い時間オフに切り換えられている増幅器群が評価され(826)、最低位増幅器群が提供される。最低位増幅器群に関連付けられた上位しきい値が評価され(828)、現在の電力増幅器の電力出力について、別の評価が行われる(820)。次に、現在の電力出力が少なくとも所定の手法で上位しきい値に相当するか否かが判定され(830)、現電力出力が少なくとも所定の手法で上位しきい値に相当する場合、最低位増幅器群はオンに切り換えられる(832)。

(もっと読む)

201 - 220 / 304

[ Back to top ]