Fターム[5F004DA00]の内容

半導体のドライエッチング (64,834) | 処理に用いるガス (14,486)

Fターム[5F004DA00]の下位に属するFターム

CF4 (1,450)

C2F6 (313)

C3F8 (211)

Cl2 (911)

CCl4 (102)

CCl2F2 (8)

CClF3 (36)

C2Cl2F4 (1)

C2Cl3F3 (2)

CBrF3 (9)

BCl3 (356)

PCl3 (2)

SiCl4 (132)

CHCl3 (22)

CH2F2 (321)

CHF3 (793)

NF3 (544)

SF6 (890)

XeF2 (78)

HF (219)

Air (40)

He (632)

Ar (1,539)

H2 (517)

N2 (930)

O2 (2,010)

O3 (172)

NO2 (43)

HCl (151)

混合量の変化 (134)

Fターム[5F004DA00]に分類される特許

81 - 100 / 1,918

プラズマ処理装置及びそのガス供給方法

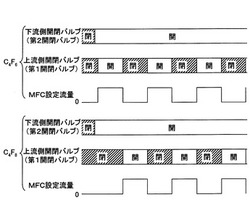

【課題】処理ガスの供給を交互に切り換える際に,これらの処理ガスが混ざり合うことなく,過渡現象を従来以上に抑制する。

【解決手段】ウエハのプラズマ処理中に少なくとも2種類以上の処理ガス(例えばC4F6ガスとC4F8ガス)を交互に切り換えて処理室内に供給する際に,切り換える処理ガスを供給する各ガス供給路については,そのガス供給路に設けられたマスフローコントローラ(MFC)の下流側の開閉バルブを開いたまま,マスフローコントローラに所定流量とゼロ流量を繰り返して設定することによって,各処理ガスの供給を交互にオンオフする。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

シリコンウエハの加工方法及び貫通電極付3次元シリコンインターポーザ並びにチップサイズパッケージ

【課題】シリコンウエハに貫通孔を形成することが不可欠なチップサイズパッケージや3次元積層型のパッケージについて、シリコンウエハに直接識別記号を形成する技術を提供することを目的とした

【解決手段】少なくとも、シリコンウエハ上に感光性レジストを塗布する塗布工程、感光性レジストを所定のパターンを有する濃度分布マスクを介して露光する露光工程、感光性レジストにシリコンウエハが露出する開口部と露出しない開口部とを形成する現像工程、ドライエッチングにより感光性レジスト開口部に対応する部位のシリコンウエハを除去してシリコンウエハに導通用の貫通孔と非貫通孔から構成される識別記号とを同時に形成する工程、残余の感光性レジストを除去する工程、とを有することを特徴とするシリコンウエハの加工方法である。

(もっと読む)

ドライエッチングガスおよびドライエッチング方法

【課題】高アスペクト比のコンタクトホールなどのパターンを形成することが可能となるドライエッチングガスを提供する。

【解決手段】二重結合に直接結合したCF3CFフラグメントを持つ化合物(ただし、CF3CF=CFCF=CF2を除く)を含むドライエッチングガス。特に、CF3CF=CF2及びCH2F2を含むドライエッチングガスが好ましい。

(もっと読む)

堆積物除去方法

【課題】エッチング処理後の放置時間の長短に係わらず、効率的に堆積物を除去することができ、かつ、パターン中の構造物の二酸化シリコンに対するダメージを抑制することのできる堆積物の除去方法を提供する。

【解決手段】基板上にエッチングによって形成されたパターンの表面に堆積した堆積物を除去する堆積物除去方法であって、前記基板を加熱しながら酸素プラズマに晒す酸素プラズマ処理工程と、前記酸素プラズマ処理工程の後、前記基板を、処理チャンバー内でフッ化水素ガスとアルコールガスの混合ガスの雰囲気に晒し、かつ、前記アルコールガスの分圧を第1の分圧とする第1の期間と、処理チャンバー内を排気し前記アルコールガスの分圧を第1の分圧より低い第2の分圧とする第2の期間とを、複数サイクル繰り返すサイクル処理工程と、を具備したことを特徴とする。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

アッシング方法およびアッシング装置

【課題】ポッピングの発生を抑制するとともに、ポッピングが発生してしまった場合には飛散した変質層の破片をも除去することができるアッシング方法およびアッシング装置を提供する。

【解決手段】イオン注入により表面に形成された変質層4とその下の未変質層3とを有するレジストを除去するアッシング方法であって、基板の前記レジストが形成された面を覆うように塗布膜5を形成し、前記レジストと前記塗布膜5とを反応性ガスを用いたプラズマ処理により除去する。

(もっと読む)

アモルファスカーボン膜の成膜方法、それを用いた半導体装置の製造方法、およびコンピュータ読取可能な記憶媒体

【課題】耐プラズマ性が高く、低温成膜が可能なアモルファスカーボン膜の成膜方法、およびそのようなアモルファスカーボン膜の成膜方法を適用した、半導体装置の製造方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器内に炭素と水素と酸素とを含む処理ガスを供給し、処理容器内の基板を加熱して処理ガスを分解して、基板上にアモルファスカーボン膜を堆積する。この方法を半導体製造装置のエッチングマスクの形成に適用して半導体装置を得る。

(もっと読む)

シリコン基板のエッチング方法、及びシリコン基板のエッチング装置

【課題】シリコン基板に形成される凹部の加工精度を高めることのできるシリコン基板のエッチング方法及び該方法を用いるシリコン基板のエッチング装置を提供する。

【解決手段】シリコン基板に対してその厚さ方向に延びる凹部を形成する際に、シリコン基板を含む基板Sを収容する真空槽11内に六フッ化硫黄(SF6)ガスのプラズマを生成して、該シリコン基板の厚さ方向に延びる凹部を形成する。加えて、真空槽11内に三フッ化ホウ素(BF3)ガスのプラズマを生成して、上記凹部の内壁面にホウ素とシリコンとを含む保護膜を形成する。

(もっと読む)

プラズマ処理方法

【課題】マイクロ波プラズマエッチングによるシリコン深溝トレンチの高速エッチングを実現することによる生産性の高いエッチング方法を提供する。

【解決手段】シリコン基板111やSOI(Silicon On Insulator)基板111に高アスペクト比(アスペクト比=トレンチ深さ/トレンチ幅)の深いシリコントレンチまたは穴を形成するプラズマエッチング方法において、マイクロ波によって生成されたプラズマを用い、プラズマを形成するマイクロ波は、高圧力、高マイクロ波出力においても安定したプラズマを形成するため、導波管104の一部にマイクロ波回転発生器105を設け、マイクロ波回転発生器105を通過したものであり、また、プラズマ形成に用いるガスとして少なくともフッ素を含むガスとO2の混合ガスを用い、かつ、試料台110に高周波電源112によりバイアス電圧を印加することにより深いシリコントレンチまたは穴を形成する。

(もっと読む)

エッチング装置及びエッチング方法

【課題】高圧下において面内均一性の向上を図るとともに、エッチングレートの低下を抑制することができるエッチング装置及びエッチング方法を提供する。

【解決手段】基板Sを収容する真空槽11と、基板Sが載置される下部電極25と、下部電極25に対してプラズマ生成空間PLを介して対向する上部電極12と、下部電極25に接続された高周波電源26と、真空槽11にエッチングガスを供給するガス導入口12aと、真空槽11内の圧力を調整する排気系制御部C2とを備えるエッチング装置であって、高周波電源26は、下部電極25にVHF周波数帯の高周波電力を供給し、排気系制御部C2は、真空槽11内を50Pa以上150Pa以下に調整し、下部電極25と上部電極12との間の電極間距離Lが50mm以上100mm以下である。

(もっと読む)

エッチング装置及び方法

【課題】シリコン等をエッチングするための反応ガスの利用効率を高め、エッチングレートを高くする。

【解決手段】被処理物9を搬入側排気チャンバー20、処理チャンバー10、搬出側排気チャンバー30の順に搬送する。処理チャンバー10内に反応ガスを導入する。排気手段5によって、排気チャンバー20,30の内圧が外部の圧力及び処理チャンバー10の内圧より低圧になるよう、排気チャンバー20,30内のガスを吸引して排気する。好ましくは、連通口13,14におけるガス流の流速を0.3m/sec〜0.7m/secとする。

(もっと読む)

プラズマ処理装置およびマイクロ波導入装置

【課題】簡単な構成でプラズマの分布を均一化する。

【解決手段】プラズマ処理装置1は、処理容器2内にマイクロ波を導入するマイクロ波導入装置5を備えている。マイクロ波導入装置5は、天井部11の複数の開口部に嵌合する複数のマイクロ波透過板73を含んでいる。複数のマイクロ波透過板73は、天井部11の複数の開口部に嵌合した状態で、載置台21の載置面21aに平行な1つの仮想の平面上に配置されている。複数のマイクロ波透過板73は、マイクロ波透過板73A〜73Gを含んでいる。マイクロ波透過板73G,73Aの中心点PG,PA間距離とマイクロ波透過板73G,73Bの中心点PG,PB間距離は、互いに等しいかほぼ等しくなるように設定される。

(もっと読む)

シリコン含有物のエッチング方法

【課題】被処理物が有機物にて汚染されている場合でも、シリコン含有物を効率良くエッチングする。

【解決手段】原料ガスを大気圧近傍のプラズマ空間23に導入してエッチングガスを生成する(生成工程)。エッチングガスを、温度を10℃〜50℃とした被処理物90に接触させる(エッチング反応工程)。原料ガスは、フッ素含有成分と、水(H2O)と、窒素(N2)と、酸素(O2)と、キャリアガスを含む。原料ガス中の窒素と酸素とキャリアガスの合計体積流量(A)とフッ素含有成分の体積流量(B)との比は、(A):(B)=97:3〜60:40である。原料ガス中の窒素と酸素の合計体積流量は、窒素と酸素とキャリアガスの合計体積流量の2分の1以下である。窒素と酸素の体積流量比は、N2:O2=1:4〜4:1である。

(もっと読む)

プラズマ処理装置

【課題】処理ガスをプラズマ生成空間及び吹出路に通して吹出し、被処理物を表面処理する際、吹出路からの電界の漏洩を防止する。

【解決手段】プラズマ生成部10の一対の電極11,12を対向方向に対向させ、これらの間にプラズマ生成空間19を形成する。ノズル部20を電気的に接地された金属製の角材21,22にて構成し、これをプラズマ生成部10の処理位置Pを向く面に配置する。連結部材31,32にてノズル部20をプラズマ生成部10に連結して支持する。吹出路29の吹出方向の長さをノズル部20の吹出路29を画成する面から上記対向方向の外側面までの寸法より大きくか略等しくする。

(もっと読む)

ガス吐出機能付電極およびプラズマ処理装置

【課題】 最大ガス流量に関する自由度に富み、電極カバー部材の薄型化も可能であり、かつ、ガス導入時の処理室内におけるガス挙動の経時的な変化も発生し難いガス吐出機能付電極を提供すること。

【解決手段】 複数のガス穴54を有するベース材52と、ベース材52の複数のガス穴54のそれぞれに対して1対1で対応するガス穴53を複数有し、ベース材52に固定されて被処理体をプラズマ処理する処理空間に面して配置される電極カバー部材51と、を含み、電極カバー部材51のガス穴径を、ベース材52のガス穴径よりも大きくする。

(もっと読む)

基板洗浄装置及び真空処理システム

【課題】基板の周縁部の不要部位を、基板の有効領域への悪影響を抑えた状態で良好に洗浄することができる技術を提供すること。

【解決手段】エッチング工程にて曝されて表面側ベベル部に針状突起群Tが生成され、また裏面側のベベル部に複合化合物Pが付着したウエハWを真空室内の回転ステージに載置する。真空室内には、ウエハWの上方側及び下方側にガスクラスターノズルが設けられ、これらノズルから洗浄処理に対応した洗浄ガスのクラスターCをウエハWの表面側及び裏面側のベベル部に照射し、ガスクラスターCの衝突による物理的作用とガスと除去対象部位との化学的作用とにより、針状突起群T及び複合化合物Pを除去する。さらに、パージガスをガスクラスターCの照射箇所に吐出することで、洗浄により生じた飛散物のウエハWへの再付着を防止する。

(もっと読む)

半導体装置及びその製法において用いられるアモルファスカーボン膜の製造法

【課題】ハードマスクとして好適に用いられるアモルファスカーボン膜の製造法を提供する。また、半導体装置における保護膜や封止膜に適したアモルファスカーボン膜の製造法を提供する。

【解決手段】プラズマ雰囲気形成領域を内部に有するチャンバーを備えるCVD装置を用意し、チャンバー内圧を6.66Pa以下、バイアス印加手段を介して成膜用の基体を設置するステージに印加するバイアスを100〜1500W、基体の成膜時の基体温度を200℃以下、成膜用の原料ガスの流量を100〜300cc/min.(0℃、大気圧)、プラズマ雰囲気を形成するための希ガスの流量を50〜400cc/min.(0℃、大気圧)とし、基体をプラズマ雰囲気に対面させ、基体上にアモルファスカーボン膜を形成する。

(もっと読む)

プラズマ処理チャンバ

【課題】プラズマエッチングリアクタの静電チャックの寿命を向上させるチャンバ洗浄機構を提供する。

【解決手段】一実施形態において、プラズマを生成するよう構成されたプラズマ処理チャンバ100は、基板を受けるよう構成された内側下部電極131と、内側下部電極の外側に配置された外側下部電極133とを備えた下部電極アセンブリを備えている。プラズマ処理チャンバは、上部電極111を備え内側下部電極131と外側下部電極133との真上に配置された上部電極アセンブリ112を、さらに備える。

(もっと読む)

低温結合方法および結合構成物

【課題】洗浄またはエッチングにより面を洗浄、活性化することを含む低温または室温で結合する方法を提供する。

【解決手段】方法は、シリコン、シリコン酸化物およびSiOのような材料の室温化学結合をなすように可逆的反応を防ぐために界面高分子化の副産物を除去することを含む。結合すべき面は、滝度合の平滑性および平坦性に研磨される(2)。VSEは、結合される面を僅かにエッチングするためにリアクチブイオンエッチングまたは湿式エッチングが用いられる(3)。表面粗さおよび平坦性は、落ちず、かつVSEプロセスにより増加される。エッチング面は、水酸化アンモニウム、フッ化アンモニウムのような溶液でリンスされ、前記面上の望ましい結合化学種の形成を助長する(4)。

(もっと読む)

81 - 100 / 1,918

[ Back to top ]