Fターム[5J500AC00]の内容

増幅器一般 (93,357) | 目的、効果 (9,357)

Fターム[5J500AC00]の下位に属するFターム

補償 (601)

出力直流電圧の変動対策、調整 (444)

素子のバラツキの影響低減 (230)

寄生素子の影響低減 (51)

アーリー効果の低減 (13)

歪低減(直線性改善を含む) (1,554)

交流出力の正負のバランス改善 (17)

ダイナミックレンジの改善 (330)

利得向上 (116)

電力効率向上、低消費電力化、節電 (1,415)

低電源電圧化 (139)

雑音低減 (966)

発振防止 (146)

保護(例;負荷の保護) (418)

その他の信頼性の向上 (124)

周波数特性の変更 (618)

入力インピーダンス特性の変更 (56)

出力インピーダンス特性の変更 (77)

整合(インピーダンス整合) (173)

不整合 (5)

誘導性負荷の駆動 (8)

容量性負荷の駆動 (49)

バイアス回路の変形、改良 (167)

ミラー比の変更 (5)

高速起動 (50)

放熱、冷却 (30)

増幅器自体の低価格化 (122)

増幅率の精度の向上 (104)

フェイルセーフ (4)

IC化容易 (84)

回路の簡素化、小型軽量化 (745)

増幅器自体の試験 (32)

増幅器自体の調整 (136)

他回路との兼用化 (24)

Fターム[5J500AC00]に分類される特許

41 - 60 / 304

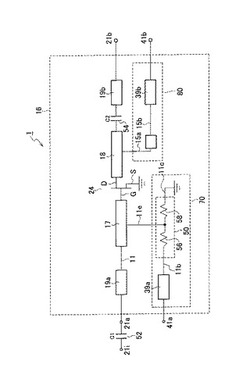

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

スイッチドキャパシタ利得段

【課題】出力電流を増やすことなくセトリング時間を短縮することが可能なスイッチドキャパシタ利得段、及び、これを用いたパイプライン型A/D変換器を提供する。

【解決手段】スイッチドキャパシタ利得段は、第1フェーズではサンプル/ホールド回路(キャパシタCf及びCs、並びに、スイッチSWa〜SWc)を用いて入力電圧Vinのサンプリングを行い、第2フェーズでは増幅器(AMP1及びAMP2)を用いてサンプリング済み入力電圧の増幅出力を行うスイッチドキャパシタ利得段において、入力電圧Vinのサンプリング動作時にのみ、前記増幅器のミラー補償を行うミラー補償部(Cm、SWg)を有する構成とする。

(もっと読む)

増幅器

【課題】 複数の増幅手段を接地電位と直流電源との間に接続していても、電源の省電力化を図る

【解決手段】 高周波信号を順に増幅するように増幅器6、8、集積増幅回路12の入出力が接続され、集積増幅回路12の出力信号をエミッタ共通接続のダブルエミッタトランジスタ20がベース電極に受けて増幅し、コレクタ電極から出力し、エミッタ電極20e1、20e2が接地電位点に接続されている。エミッタ電極20e1と接地電位点との間に、増幅器6及び集積増幅回路12の電源端子A、B、C、Dが、直列に接続され、エミッタ電極20e2と接地電位点との間に、増幅器8の2つの電源端子E、Fが接続されている。

(もっと読む)

利得可変増幅器および光受信器

【課題】大信号入力後に小信号が入力される際の自動利得制御応答時間を短縮する。

【解決手段】利得可変増幅器は、フォトダイオード(PD)から入力される電流信号INを帰還抵抗RFの値に比例する利得によって増幅すると同時に電圧信号に変換するインピーダンス変換増幅器コア回路(TIACORE)と、TIACOREの出力を入力として出力信号OUTを出力する出力バッファ(BUF)と、TIACOREの出力電圧に基づいてTIACOREの利得が所望の値になるようにフィードバック制御し、外部から与えられるリセット信号ResetをトリガとしてTIACOREの状態を初期化してTIACOREの利得が最大になるように制御する外部リセット端子付き利得制御回路(CTRL)とを有する。

(もっと読む)

シングルサプライD級アンプ

利得可変回路

【課題】利得制御信号の分配配線を簡素化し、回路の高周波化・広帯域化を実現し、負方向の利得可変幅を増大させる。

【解決手段】利得可変回路は、入力信号Inを増幅する可変利得増幅器(VGA)1と、VGA1の出力信号Out1を増幅する固定利得増幅器(Amp)2と、Amp2の出力信号Out2の振幅を検出して、検出した振幅と予め設定された振幅設定値とが等しくなるようにVGA1の利得を制御する自動利得調整回路(AGC)3とを備える。VGA1は、ギルバートセル型の可変利得増幅器である。

(もっと読む)

クラス特性可変増幅器

電力増幅装置

【課題】高出力と専有面積の縮小とを両立させた電力増幅装置を提供する。

【解決手段】基板上に形成された電力増幅装置300であって、全体で環状の一次インダクタ1,2と、グランドパターン4〜8と、トランジスタ対(Q1p,Q1n)および(Q2p,Q2n)と、二次インダクタ3とを備える。グランドパターン4〜8は、基板に垂直な方向から見て、環状の一次インダクタ1,2の内側の領域の一部から外側の領域に及ぶように設けられ、外側の領域の複数箇所で接地される。各一次インダクタ1,2の両端には、対応のトランジスタ対を構成する第1および第2のトランジスタの第1の主電極がそれぞれ接続される。第1および第2のトランジスタの各第2の主電極は、一次インダクタの内側の領域でグランドパターンに接続されるとともに、上記の接地された複数箇所のいずれとも電気的に導通する。

(もっと読む)

増幅器

【課題】広帯域特性の改善と隣接セルからの干渉問題の抑制を両立できる増幅器を得る。

【解決手段】3セル以上のユニットセルトランジスタ(11)が等間隔に配置されたマルチセルトランジスタ(10)と、スリット(23)で区切られたオープンスタブ(22)により、基本波の整数倍の周波数で短絡状態を形成するように各ユニットセルトランジスタに対応して設けられた高調波処理回路(21)を複数有し、各高調波処理回路がトーナメント構成となるように線路構成された出力整合回路(20)とを備えた増幅器であって、各高調波処理回路(21)は、マルチセルトランジスタを構成する各ユニットセルトランジスタのゲートまたはドレイン端子の少なくとも一方から、電気長で1/2波長未満の距離に配置され、オープンスタブ(22)が、主線路と平行して片側に1本で配置されている。

(もっと読む)

電流源、電流源回路、およびこの電流源回路の使用

【課題】MOS技術を使ったパワー素子を用いなくても、正確な負荷電流を供給しうる電流源を提供する。

【解決手段】電流源10が、制御端子および制御パスを有するバイポーラトランジスタ1と、バイポーラトランジスタ1の制御パス上にあって、電気負荷D1と接続される第1の端子と、抵抗器4経由で基準電源端子と接続される第2の端子と、バイポーラトランジスタ1の制御端子に接続され、この制御端子に送られる制御電流を測定する測定装置2と、バイポーラトランジスタ1の制御電流が制御パス上に位置する第1の端子において補償されるように、測定装置2およびバイポーラトランジスタ1に接続された補償電流源3とを備える。

(もっと読む)

バイアス回路

【課題】 不要波の出力を抑制することのできる小型なバイアス回路を得ることを目的とする。

【解決手段】 半導体素子3に電力を供給するバイアス回路において、インダクタ5及びキャパシタ6が直列に接続された直列回路と、直列回路に並列に接続されて並列回路を構成するインダクタ7と、接地されたキャパシタ8とインダクタ7との間に接続され、外部から電力が供給されるバイアス端子9を備えて、直列回路および並列回路の共振により、半導体素子3の不要波を除去し所望の周波数のみを伝達する。

(もっと読む)

振幅制限増幅回路

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40と、からなる回路を、2段以上に亘って縦続接続したて構成する。

(もっと読む)

電荷を電圧に変換するシステムおよびこのシステムを制御する方法

【課題】最終変換利得を低減させることなく、変換デバイスを制御する方法を提供する。

【解決手段】本発明は、増幅器と、増幅器の入力と出力の間に負帰還で取り付けられた少なくとも1つのキャパシタとを含み、それによって前記増幅器を、前記増幅器から電荷を受け取る少なくとも1つの入力段と前記増幅器へ電圧を送る少なくとも1つの出力段との間に接続でき、前記電圧が、入力で受け取った電荷を表す、電荷を電圧に変換するデバイスを制御する方法であって、前記方法が、入力で受け取った電荷の電圧変換を含む少なくとも1つの段階(62)を含む、方法に関する。本発明によれば、変換段階は少なくとも、増幅器が入力段に接続され、また増幅器が出力段から切断される、1つの第1の副段階(64)と、増幅器が入力段から切断され、また増幅器が出力段に接続される、その後の第2の副段階(66)とを含む。

(もっと読む)

D級増幅回路

【課題】簡易な構成で、D級増幅回路の出力電流を反転可能にする。

【解決手段】本発明に係るD級増幅回路100は、入力信号AINに応じて第1状態と第2状態とが切り替えられる。第1状態では、コイルLと負荷30とが電気的に切り離された状態で、第1ノードND1から第2ノードND2へ向かう電流がコイルLに流れた後、コイルLと負荷30とが電気的に接続されて、第1ノードND1から第2ノードND2へ向かう電流が負荷30を流れるとともに容量素子Cに充電される。第2状態では、コイルLと負荷30とが電気的に切り離された状態で、第2ノードND2から第1ノードND1へ向かう電流がコイルLに流れた後、コイルLと負荷30とが電気的に接続されて、第2ノードND2から第1ノードND1へ向かう電流が負荷30を流れるとともに容量素子Cに充電される。

(もっと読む)

D級増幅回路

【課題】 D級増幅回路においてゲイン切替を好適に行う。また、それに伴って発生する弊害(周波数特性の変動等)を防止する。

【解決手段】 D級増幅回路は、入力信号(Vin+,Vin−)とフィードバック信号(FBa,FBb)を合成した信号を積分して積分信号(Xa,Xb)を出力する演算手段(10)と、積分信号と三角波信号(TRI)との比較結果に基づいてパルス幅変調信号(Pa,Pb)を生成する信号生成手段(40)と、演算手段と信号生成手段との間を接続する第1・第2帰還経路(19a,19b)上の第1・第2ノード(N1,N2)にその両端が接続された帰還抵抗値切替回路(51)と、を備える。この回路は、自身の抵抗値を変更することによって、全差動オペアンプ(11)からみた帰還抵抗値を変更する。D級増幅回路は、このほか、帰還抵抗間容量切替回路(52)、あるいは積分定数切替回路(53a,53b)を備える。

(もっと読む)

車載用アンプの低バッテリ電圧時制御方法及び装置

【課題】バッテリ電圧が低下してアンプの電流が増大し、ヒューズ切れ等を生じることがなく、且つアンプ全体の出力の大きな低下を生じない「車載用アンプの低バッテリ電圧時制御方法及び装置」とする。

【解決手段】複数チャンネルのオーディオ信号を入力して各チャンネルの出力レベルを算出し、その出力レベルにより、最も出力レベルの高いチャンネルを選択し、アンプの昇圧用出力電圧を、最も出力レベルの高いチャンネルの出力が得られるように設定する。この出力電圧で作動するバッテリ電流を算出し、その電流がヒューズの容量を超えるかを判別する。超えないときはアンプからスピーカへの出力を行い、超えるときは前記選択した最も出力レベルの高いチャンネルの出力レベルを所定量低下させ、低下させた出力レベルでのバッテリ電流がヒューズの容量を超えないとき、アンプからスピーカへの出力を行う。

(もっと読む)

バイアス電流モニタおよびアンプのための制御機構

アンプのバイアス電流をモニタリングおよび制御するための技術が説明される。典型的な設計において、装置は、アンプとバイアス回路を含むとしてもよい。アンプは、インダクタに連結された少なくとも一つのトランジスタを含むとしてもよい。バイアス回路は、アンプに対するターゲットバイアス電流を得るために、アンプの少なくとも一つのトランジスタに対する少なくとも一つのバイアス電圧を生成してもよい。バイアス回路は、アンプのインダクタを横切る電圧、または、アンプの少なくとも一つのトランジスタの一つを用いて形成されたカレントミラーによる電流、または、アンプの少なくとも一つのトランジスタのうちの一つのゲート−ソース間電圧、または、アンプを模倣するレプリカ回路の電圧、または、無効化されたスイッチモード電源を用いてアンプに適用される電流、に基づいて少なくとも一つのバイアス電圧を生成してもよい。 (もっと読む)

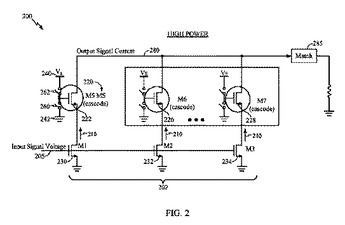

RF駆動増幅器送信機における利得制御の直線性

入力信号電圧を複数の入力信号電流に変換するための複数の電圧−電流トランスデューサとカスコード段とを備える例示的装置が開示される。カスコード段は、増幅器利得制御を実現するように電圧−電流トランスデューサに結合される。カスコード段は、薄ゲート酸化膜トランジスタと厚ゲート酸化膜トランジスタとを備える。  (もっと読む)

(もっと読む)

歪補償装置

【課題】TDD方式や送信信号の平均電力が時間的に変化する通信方式であっても、高い歪補償性能を有し、かつ歪補償の追従に要する収束時間を短縮できる歪補償装置を提供する。

【解決手段】歪補償前の送信信号及び高出力増幅器2がオンとなる送信時間に増幅された当該送信信号を取得するデータサンプル部4と、データサンプル部4によって取得された信号に基づいて、高出力増幅器2の逆歪み特性データを算出するLUT計算部5と、LUT計算部5によって算出された逆歪み特性データを用いて、送信信号に対して高出力増幅器2で発生する歪みを補償するプリディストータ1と、高出力増幅器2がオンして送信時間が開始された当初の区間に対応する信号が連続して取得されないように、データサンプル部4による信号取得の時間位置を制御するサンプル位置制御部6とを備える。

(もっと読む)

カスケード電圧増幅器およびカスケード電子管を起動する方法

【課題】

パルス又は連続波形で増幅出力を発生する改良型のカスケード電圧増幅器を提供する。

【解決手段】

本発明による増幅器は、スイッチング増幅およびクラスA又はC増幅構造として構成された電子管を用いる少なくとも一つの非最終ステージを含む。最終ステージはクラスA又はC増幅構造として構成された電子管を含む。前記少なくとも一つの非最終ステージと前記最終ステージは直列に接続してあり、増幅された出力は少なくとも1000ボルトの電圧を有する。更に共通の真空エンクロージャ内部で複数のカスケード電子管ステージを起動させる方法を開示する。有利にも、充分な量のエネルギーが第1ステージに供給されると何らかの中間ステージを通って最終ステージまで直列に伝搬し全部の真空間断の起動が容易に行なえる。

(もっと読む)

41 - 60 / 304

[ Back to top ]