Fターム[5J500AC00]の内容

増幅器一般 (93,357) | 目的、効果 (9,357)

Fターム[5J500AC00]の下位に属するFターム

補償 (601)

出力直流電圧の変動対策、調整 (444)

素子のバラツキの影響低減 (230)

寄生素子の影響低減 (51)

アーリー効果の低減 (13)

歪低減(直線性改善を含む) (1,554)

交流出力の正負のバランス改善 (17)

ダイナミックレンジの改善 (330)

利得向上 (116)

電力効率向上、低消費電力化、節電 (1,415)

低電源電圧化 (139)

雑音低減 (966)

発振防止 (146)

保護(例;負荷の保護) (418)

その他の信頼性の向上 (124)

周波数特性の変更 (618)

入力インピーダンス特性の変更 (56)

出力インピーダンス特性の変更 (77)

整合(インピーダンス整合) (173)

不整合 (5)

誘導性負荷の駆動 (8)

容量性負荷の駆動 (49)

バイアス回路の変形、改良 (167)

ミラー比の変更 (5)

高速起動 (50)

放熱、冷却 (30)

増幅器自体の低価格化 (122)

増幅率の精度の向上 (104)

フェイルセーフ (4)

IC化容易 (84)

回路の簡素化、小型軽量化 (745)

増幅器自体の試験 (32)

増幅器自体の調整 (136)

他回路との兼用化 (24)

Fターム[5J500AC00]に分類される特許

21 - 40 / 304

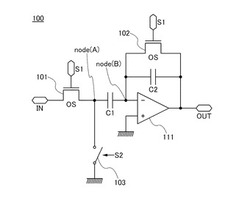

半導体回路

【課題】安定した入出力特性を得られる半導体回路を提供する。特に、スイッチング素子のリーク電流に起因する不具合が抑制された半導体回路を提供する。

【解決手段】スイッチトキャパシタ回路に用いられるスイッチング素子に、酸化物半導体などのワイドギャップ半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタを適用する。このようなトランジスタは、オフ状態におけるリーク電流が小さい特徴を有し、当該トランジスタをスイッチング素子に適用することによりリーク電流に起因する不具合が抑制され、安定した入出力特性が得られる半導体回路を構成することが出来る。

(もっと読む)

増幅回路

【課題】追加プロセスなしに、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる高耐圧の入力段とすることが可能な増幅回路を提供する。

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

(もっと読む)

受信回路

【課題】本発明の実施形態は、光信号の変動に起因する誤動作を抑制することが可能な受信回路を提供する。

【解決手段】実施形態に係る受信回路は、光信号を受信し第1の光電流に変換する第1の受光素子と、前記第1の光電流を信号電圧に変換する信号電圧生成部と、前記光信号を受信し第2の光電流に変換する第2の受光素子と、前記第2の光電流を基準電圧に変換する基準電圧生成部と、前記基準電圧の信号成分を遅延低減する遅延要素と、前記信号電圧と、前記基準電圧に基づく閾値電圧と、を比較する比較器と、を備える。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

オペアンプ

【課題】低い電源電圧に対応する生産プロセスで生産された製品に対して高い電源電圧を供給した場合にも、ホットキャリアに起因するオペアンプ特性の劣化を回避することができるオペアンプを提供する。

【解決手段】バイアス電源回路が、2つのカレントミラー回路の間に挿入された一対の抵抗部を有して定電流バイアス電位の他に付加バイアス電位を生成し、差動増幅器が、差動入力トランジスタ対と能動負荷トランジスタ対との間に挿入され且つ当該付加バイアス電位によってバイアスされる電圧降下用トランジスタ対を含むオペアンプ。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】変調信号のオンデューティー比が上限付近の状態が継続しても、D級増幅器を正

常に動作させて駆動信号を出力が可能とする。

【解決手段】駆動波形信号から生成した変調信号を電力増幅した後、平滑化することによ

って駆動信号を生成する。変調信号を電力増幅するデジタル電力増幅器では、電源とグラ

ンドとの間で2つのNチャンネル(以下ch)MOSFETをプッシュ・プル接続し、更

に、電源側のNchMOSFETに対して並列にPchMOSFETを接続する。こうす

れば、電源側のNchMOSFETをONにするためのブートストラップコンデンサーに

蓄えられた電荷が不足してNchMOSFETをONにすることができない場合でも、P

chMOSFETをONにすることで電力増幅を行うことができ、駆動信号を出力するこ

とが可能となる。

(もっと読む)

増幅装置

【課題】電流コラプスを適切に改善するとともに、光照射による消費電力を抑制する。

【解決手段】包絡線抽出部1は、増幅部2で増幅される信号の包絡線を抽出する。増幅部2は、可変電源部3から供給される電力によって、入力される信号を増幅する。可変電源部3は、包絡線抽出部1から出力される包絡線に応じて、増幅部2に供給する電力を可変する。照射部4は、増幅部2に光を照射する。制御部5は、包絡線抽出部1から出力される包絡線の傾きに応じて、照射部4の出力する光を制御する。

(もっと読む)

ベース電流補償回路

【課題】印加電圧が変動しても、入力端子から流れ込む電流を一定とすることのできるベース電流補償回路を提供する。

【解決手段】実施形態のベース電流補償回路1は、補償対象トランジスタQ10のベースが接続される入力端子INにベースが接続されたアーリー効果相殺用トランジスタQ2が、補償対象トランジスタQ10に発生するアーリー効果と同じアーリー効果を補償電流生成用トランジスタQ1に発生させる。補償電流生成用トランジスタQ1に流れる電流は、カレントミラー回路11で折り返されて、補償対象トランジスタ10のゲートへ注入される。

(もっと読む)

信号出力装置

【課題】映像再生処理時間の情報を表示装置から取得できなくても、表示装置における映像再生処理時間を測定し、オーディオ信号の遅延時間を制御する信号出力装置を提供すること。

【解決手段】本発明の実施形態に係るAVアンプ10は、テレビ20に遅延測定用のオーディオ信号Sa2を出力して、テレビ20において遅延された再生オーディオ信号Sa2dを取得することにより、テレビ20における遅延時間を測定する。そして、AVアンプ10は、映像信号Sgをテレビ20に出力するとともに、オーディオ信号Sa1を、測定した遅延時間に応じて遅延させてスピーカ装置40に出力することにより、テレビ20の表示画面に表示される映像の内容と、スピーカ装置40から放音される内容とのリップシンク制御を実現する。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

音声信号処理回路

【課題】音声信号処理回路の汎用性を向上する。

【解決手段】ゲインコントローラ12は、音声信号の振幅をコントロールする。PWM変換器18は、振幅がコントロールされた信号をPWM変換する。そして、ゲインコントローラ12は、リミッタ制御信号に応じて、音声信号の振幅を制限し、PWM変換回路18は、振幅コントロールされた音声信号の最大振幅の信号については、リミッタ制御信号にかかわらず、PWM変換の変調度を制限による振幅制限を掛ける。

(もっと読む)

低雑音増幅器

【課題】製造上の素子の特性ばらつきや電源電圧の変更やばらつきに対しても安定化させる。

【解決手段】入力端子2と、入力端子に入力された入力信号を増幅するトランジスタ1と、トランジスタの出力信号を出力する出力端子3と、トランジスタの出力信号の帰還量として振幅を調整して出力する帰還量調整回路10と、トランジスタに供給されるバイアス電流を生成するバイアス回路9と、帰還量調整回路の出力電圧と参照電圧とを比較して入力信号が前記トランジスタの利得抑圧を発生させることを判定したときトランジスタのバイアス電流を増加させるようにバイアス回路を動作させる差動電圧比較器11と、参照電圧を生成して差動電圧比較器の一方の入力端に印加させる第1の第1の入力バイアス回路12と、帰還量調整回路の出力電圧にバイアス電圧を付加して差動電圧比較器の他方の入力端に印加させる第2の第2の入力バイアス回路13と、を備える低雑音増幅器。

(もっと読む)

歪補償装置、歪補償方法、及び無線装置

【課題】本実施例における歪補償装置は、歪補償処理後の送信信号に対するRF補正処理の精度を向上させることを目的とする。

【解決手段】本実施例における歪補償装置は、送信信号の電力値に関連付けられた複数の歪補償係数を記憶する歪補償係数記憶部と、複数の歪補償係数の中から、入力された送信信号の電力値に対応する歪補償係数を取り出し、取り出された歪補償係数に基づいて、送信信号に対して前記歪補償処理を行う歪補償処理部と、歪補償係数記憶部に記憶された歪補償係数に基づいて位相補正値を計算する位相計算部と、送信信号の位相を、位相計算部によって計算された位相補正値に基づいて補正することにより、参照信号を生成する位相補正部と、参照信号と前記送信電力増幅器からフィードバックされたフィードバック信号とに基づいて、歪補償処理が行われた送信信号に対して補正処理を行う補正処理部とを含むことを特徴とする。

(もっと読む)

電圧発生装置、電流発生装置

【課題】出力電流の制限の精度を劣化させないでより高い電圧を発生させる。

【解決手段】本発明の電圧発生装置は、第1、第2、第3の入力増幅部と、第1、第2、第3の入力増幅部にそれぞれ設けられた飽和防止回路と、電流帰還手段と、電圧帰還手段と、出力増幅部と、ダイオードスイッチと、出力制御部を具備する。電流帰還手段は、電位が接地に近い方の負荷の端子に負荷と直列に接続された電流検出用抵抗の電圧を検出し、その検出した電圧を第1、第3の入力増幅部の入力側に帰還する。出力増幅部は、逆方向に電流が流れるように負荷に電圧を印加する第1の出力増幅器と、所定方向に電流が流れるように負荷に電圧を印加する第2の出力増幅器とを有する。出力制御部は、正出力端子と負出力端子の出力に応じて、第1の出力増幅器または第2の出力増幅器を選択し、制御する。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

電源分離型電子機器

【課題】片手の操作で筐体から電源回路部を容易に取り外すことができて作業性を向上する。

【解決手段】筐体と、略直方体形状を有して筐体に着脱可能に収納される電源回路部180と、筐体に収納され、電源回路部180から給電される増幅部190とを備える。電源回路部180は、周側部のうち長手方向に平行な一対の側部の各々に、互いに対向するように、係止用突起を含む係止部200,210を有する。筐体は、係止用突起に係止可能な係止溝を有する。

(もっと読む)

送信装置及び歪補償方法

【課題】相互変調歪成分の歪補償において、フィードバック信号のアナログデジタル変換処理におけるサンプリング周波数の高速化を緩和する。

【解決手段】送信装置1は、周波数が離間する複数信号を含むベースバンド信号を変調する変調器12と、変調信号を増幅する増幅器14と、増幅器14の出力信号の一部を復調する復調器20と、所定の相互変調歪成分の周波数よりも低いサンプリング周波数で復調信号をサンプリングしてデジタル信号に変換するアナログデジタル変換器23と、アナログデジタル変換によって生じる所定の相互変調歪成分の折り返し成分を検出する検出部25と、検出された折り返し成分に応じて補償係数を生成する補償係数生成部32と、入力信号に補償係数を乗じる歪補償部10と、を備える。

(もっと読む)

スイッチ制御回路、増幅器、および送信装置

【課題】 増幅素子のバイアス入力部の近傍に大容量のコンデンサが接続された場合であっても、バイアス電圧制御の応答遅れを抑制することが可能なスイッチ制御回路、増幅器、および送信装置を提供する。

【解決手段】 バイアスが印加されることによって増幅作用を発生する増幅素子の前記バイアスのオン/オフを制御するスイッチ制御回路であって、二つのスイッチ素子が相補的に動作するコンプリメンタリ回路を複数並列に接続した回路を含む。

(もっと読む)

電子回路

【課題】適切な利得制御を行うことが可能な電子回路を提供すること。

【解決手段】入力信号Iinを増幅する増幅器10と、増幅器10から出力された出力信号Vtiaを、時定数に基づいて平均化して制御信号Vagcを生成するとともに、時定数τs1と、時定数τs1より大きい時定数τl1との間で時定数を切り替え可能な制御回路20と、制御信号Vagcに基づいて第1時定数制御信号を生成し、制御回路20の時定数を時定数τs1から時定数τl1に切り替える第1時定数制御回路30と、増幅器10から出力された出力信号Vtiaを、時定数τs1より大きく、かつ時定数τl1より小さい時定数τl2に基づいて平均化して第2時定数制御信号を生成し、制御回路20の時定数を時定数τl1から時定数τs1へと切り替える第2時定数制御回路60と、制御信号Vagcに基づいて、入力信号Iinをバイパスするバイパス回路40と、を具備する電子回路。

(もっと読む)

21 - 40 / 304

[ Back to top ]