Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

181 - 200 / 211

ポイント拡散クロックの分配ネットワーク及びクロックの分配方法

【課題】ポイント拡散クロックの分配ネットワーク及びクロックの分配方法を提供する。

【解決手段】マスタクロックに応答して動作する複数のロードを備えるクロックシステムを複数の領域に分割し、分割された領域にマスタクロックを分配するために、複数の分割領域のそれぞれに配置されて、複数の分配ポイントまたはロードにマスタクロックを供給する複数のクロックポイントと、複数のクロックポイントの間に少なくとも一つずつ配置され、複数のクロックポイントにマスタクロックを伝達する複数の分配ポイントと、を備えるポイント拡散クロックの分配ネットワークである。これにより、高速で動作しつつも、消費電力が減少する。

(もっと読む)

デュアルループPLLおよび逓倍クロック発生装置

【課題】 初期起動においてロックアップ時間を短縮できるデュアルループPLL(Phase Looked Loop)を提供すること、および消費電力低減に寄与する逓倍クロック発生装置を提供すること。

【解決手段】 デュアルループPLLは、位相を比較する位相比較器1を有する位相比較ループと、周波数を比較する周波数比較器7を有する周波数比較ループとを有するデュアルループPLLを備え、周波数比較器7は、位相比較器1に用いる、外部基準クロックラインCLex11から入力される基準クロック信号と異なる、キャリブレーションクロックラインCLcal18から入力される入力信号を用いて周波数比較を行う。また、上記デュアルループPLLを用いて、逓倍クロック発生装置を構成する。

(もっと読む)

タイミング発生回路

【課題】 微小遅延部で発生させる遅延量を精密に制御することができるタイミング発生回路を得る。

【解決手段】 直列接続した粗遅延部及び微小遅延部と、粗遅延部に電源電圧を供給する第1のDLLと、微小遅延部に電源電圧を供給する第2のDLLとを設ける。そして、第1のDLL内のモニタ回路として用いる遅延部を粗遅延部と同じ回路形式とする。また、第2のDLL内のモニタ回路として用いる遅延部を微小遅延部と同じ回路形式とする。

(もっと読む)

比較器

【課題】小面積で計算速度が速い比較器を提供する。

【解決手段】比較器は、各々の入力端にクロック信号が共通して入力される第1及び第2遅延回路と各々の第1入力端に第1遅延回路の出力信号及び第2遅延端の出力信号が各々入力される第1及び第2論理ゲートを含む第1ラッチ回路、及び第1論理ゲートの出力端から出力される信号及び前記第2論理ゲートの出力端から出力される信号をラッチする第2ラッチ回路を備える。第1遅延回路の遅延時間は外部から入力される第1デジタル信号により制御される可変の遅延時間であり、前記第2遅延回路の遅延時間は外部から入力される第2デジタル信号により制御される可変の遅延時間である。

(もっと読む)

位相比較回路及びクロックリカバリ回路

データ信号とクロック信号の位相差を示す位相差信号を出力する位相比較回路であり、異なる複数の識別レベルを用いてデータ信号の位相を検出し、位相を示す複数の信号を出力する検出部と、検出部から出力される複数の識別レベルに対応する複数の出力信号の各々とクロック信号との位相差を示す複数の位相差信号を出力する位相比較部と、位相比較部から出力される複数の位相差信号の全部又は一部を用いて、複数の位相差信号のうちの1つの信号を出力するか又は出力しないかを制御する制御部とを有するように構成する。  (もっと読む)

(もっと読む)

ゼロクロス検出装置および画像形成装置

【課題】ゼロクロス付近で変化率の大きい台形歪波形のような入力波形においても、正常にゼロクロス信号を検出する。

【解決手段】交流電源11に接続され交流電圧の正側の半波を検出し、当該半波に対応する矩形波を出力する第1のフォトカプラ12と、交流電源に接続され交流電圧の負側の半波を検出し、当該半波に対応する矩形波を出力する第2のフォトカプラ13と、第1のフォトカプラ12から出力される矩形波の後エッジを検出する第1の後エッジ検出回路14と、第2のフォトカプラ13から出力される矩形波の後エッジを検出する第2の後エッジ検出回路15と、第1および第2の後エッジ検出回路の2出力を受けてその論理和出力を生成する論理和回路16とを備え、論理和回路16の出力をゼロクロス信号として用いる。

(もっと読む)

半導体装置

【課題】

オシレータから出力されるクロックに発振異常が発生した場合、その異常に対応してマイクロコンピュータの動作を適切に停止させる。

【解決手段】

発振器と、発振異常検出部とを具備する半導体装置を構成する。発振異常検出部は、その発振器から出力されるクロックを計測して得られたカウント値に基づいてその発振器の周波数を特定する。そして、その周波数が所定の周波数範囲外のときに、発振異常信号を生成する。

(もっと読む)

電圧比較器および電圧比較方法

【課題】不感領域を小さくできるとともに高い応答性と高精度な電圧比較を実現する。

【解決手段】 第1の入力信号処理回路と第1の出力端子との間に第1の遮断回路を設けるとともに、第2の入力信号処理回路と第2の出力端子との間に第2の遮断回路を設け、これら第1および第2の遮断回路で、比較動作時に信号レベル判定回路から第1および第2の入力信号処理回路を遮断する。

(もっと読む)

絶縁型電圧検出回路

【課題】回路構成が単純で、廉価な部品のみにより構成される、簡易的な絶縁型電圧検出回路を提供する。

【解決手段】レジスタ1に設定されたデータに比例したパルス幅の第1のPWM信号を出力するパルス幅変調回路2と、その出力を絶縁して第2のPWM信号として出力する第1の絶縁手段3と、第2のPWM信号をアナログ電圧信号aに変換する変換回路4と、アナログ電圧信号aと検出対象であるアナログ電圧信号bを比較し、2つの極性をもつ比較信号を出力する比較器5と、その比較信号を絶縁して2つの極性を有する第2の比較信号cとして出力する第2の絶縁手段6とを備え、第2の絶縁手段6から出力される第2の比較信号cの結果を所定の周期で検出し、アナログ電圧信号aと検出対象であるアナログ電圧信号bが等しくなるように、レジスタ1に設定するデータをCPU7により増減させるようにした絶縁型電圧検出回路。

(もっと読む)

トリガ信号生成回路および記録装置

【課題】トリガ信号を出力する条件を多様に設定し得るトリガ生成回路を提供する。

【解決手段】記録対象データDiの電気的パラメータが所定条件を満たしたときにトリガ検出信号Sdを出力する複数のトリガ検出器23a〜23hと、各トリガ検出器23a〜23hからそれぞれ出力された各トリガ検出信号Sdに対して論理処理を実行してトリガ信号Stを出力する論理処理回路24とを備えたトリガ信号生成回路11であって、入力した記録対象データDiを指定されたトリガ検出器23に出力するセレクタ回路22を備えている。

(もっと読む)

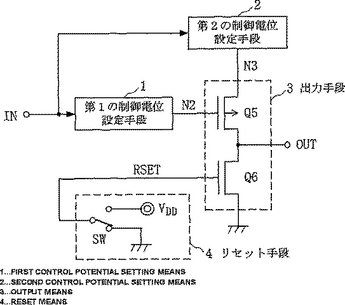

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

信号伝送システム及びそれに用いる信号波形変換回路並びに信号波形復元回路

【課題】 送信信号を伝送する場合、できるだけ信号周波数を低くして他の回路への影響を防止し、またノイズ除去して信号の伝送をなす。

【解決手段】 信号送信側において、信号波形変換回路として機能する分周回路20を用いて、送信すべき信号を分周して互いに位相が異なる一対の信号Q1,Q2に変換して伝送路を介して送信する。受信側では、信号波形復元回路21を用いて、当該一対の信号のレベルの組み合わせに応じたレベルを生成して元の信号を復元する。伝送路では、信号の周波数が分周処理により半分に低下するので、他の回路などへの影響が少なくなり、また受信側回路が複数存在する場合にも、送信側から一対の信号を全ての受信側回路へ伝送すればよいので、送信側の出力ピンも大幅に低減する。さらに、分周回路20内において、ノイズ除去の機能である保護回路22を付加すれば、ノイズ低減も可能となる。

(もっと読む)

ディジタルPWM手段

【課題】 簡単な構成で、短いPWM信号周期でも高い分解能のPWM信号であって、加えて、スイッチング周波数のスペクトル強度を低減するPWM信号を出力するディジタルPWM手段を実現すること。

【解決手段】

2値以上を持つ信号を出力する手段であって、そのうちの1つの値が継続する時間と該値の繰り返す周期の比率が、入力信号に応じて変化するディジタルPWM手段であって、該値の繰り返す周期を固定しないで変化させることによって、簡単な構成で、短いPWM信号周期でも高い分解能のPWM信号であって、加えて、スイッチング周波数のスペクトル強度を低減するPWM信号を出力するディジタルPWM手段を実現できる。

(もっと読む)

集積回路

【課題】 内部回路が逓倍クロック信号に基づいて動作することによる電源変動の影響が、クロック信号出力回路に及ぶことを極力回避できる集積回路を提供する。

【解決手段】 電源配線14がデジタル回路群17を経由してクロック信号出力回路11に電源供給を行う経路中にローパスフィルタ22を配置し、電源配線14を伝搬しようとするノイズ成分をアナロググランド側に逃がして除去する。そして、クロック信号出力回路11による逓倍クロック信号fmの発振精度を向上させ、その逓倍クロック信号fmに同期して動作するデジタル回路群17における通信ブロック16の通信精度等を向上させる。

(もっと読む)

半導体集積回路及びその制御方法

【課題】

本発明の目的は、感度調整回路を備えたコンパレータおよびこのコンパレータ有

したデータ通信装置を提供することである。

【解決手段】

本発明においては、CMOSトランジスタで構成され、マイクロコンピュータに

よりオフセット(感度)制御可能なコンパレータ(差動増幅アンプ)が実現される

。この感度調整回路を備えたコンパレータを備えることにより、コストおよび回路

面積を増やすことなく感度の高いデータ通信装置が実現できる。そして、このデー

タ通信装置を使用することにより、より遠距離に位置する電波源からの電波受信をすることができる。また、アンプ感度調整回路を任意の感度に調整することによっ

て、特定の通信距離範囲に渡って配置される電波源との間で常に安定した通信が確

保されると共に、無用なノイズに対する感度を落として良質な通信を維持できる。

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】基準信号と内部クロック信号とが同期しているか否かを瞬時に判断することによって検査効率を向上させることができる遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路を提供する。

【解決手段】遅延同期ループ回路に、各タップ信号をクロック信号とする複数のフリップフロップを直列に接続することによってシフトレジスタを形成し、複数のフリップフロップにクロック信号として基準信号からの遅延時間の長いタップ信号から順に入力した場合に、このシフトレジスタから出力される第1の検査信号と、複数のフリップフロップの全てにクロック信号として基準信号を入力した場合に、このシフトレジスタから出力される第2の検査信号とを検出し、これらの第1の検査信号と第2の検査信号との差に基づいて良否を判定することとした。

(もっと読む)

シグマデルタベースのフェーズロックループ

位相周波数検出器(PFD)と、チャージポンプと、電圧制御発振器とを含むシグマデルタベースのフェーズロックループ・デバイスが提供される。PDFは、基準信号とフィードバック信号とを受信し、基準信号とフィードバック信号との比較に基づく信号を出力する。チャージポンプは、PFDからの出力信号に基づくチャージを出力する。チャージポンプは、固定量の電流を流す第1の電流源と、可変量の電流を流す第2の電流源とを含む。電源制御発振器は、チャージポンプからの受け取ったチャージに基づくクロック信号を出力する。  (もっと読む)

(もっと読む)

集積回路

【課題】 回路評価において、集積回路に入力するクロックのON/OFF制御を不要とし、その集積回路における他の回路部に影響を与えることなく、複数のクロック断検出回路の動作確認を同時に行うことを可能とする。

【解決手段】 入力されるクロックを停止することなく、クロック断を検出する集積回路10であって、クロック断を検出するクロック断検出部20と、クロック断検出部20に入力されるクロックを、クロック断検出部20に入力される前に入力し、マスク設定がON状態である場合はマスクして、マスク設定がOFF状態である場合はそのままで、クロック断検出部20へ出力するクロックマスク制御部21とを備えた集積回路。

(もっと読む)

データ伝送装置、およびデータ伝送方法

【課題】パラレルデータを、シリアルデータに正確に変換して所定のデータ伝送路に出力するデータ伝送装置、および、パラレルデータを、シリアルデータに正確に変換して所定のデータ伝送路に出力するデータ伝送方法を提供する。

【解決手段】伝送されてくるパラレルデータが同期している第1の基準クロックとは別の第2の基準クロックを生成するクロック生成部1311と、上記パラレルデータを、上記第2の基準クロックに基づく第2のパラレルデータに変換するASIC1313と、このASIC1313から出力された第2のパラレルデータを、上記第2の基準クロックに基づくシリアルデータに変換するシリアライザ1315とを、全て同一基板上に備えた。

(もっと読む)

等間隔パルス列生成装置および生成方法

【課題】 低消費電力を図り、かつ周波数の変動を生じない精度の良い出力波を得ることのできる位相合成装置および位相合成方法を提供する。

【解決手段】

クロックに同期した位相データと所定電圧値とのクロス点前後の位相データの差分をサンプルホールドした後アナログ値に変換するD/A変換器2と、D/A変換器により変換されたアナログ値を電流に変換する電流源3および該電流を時間的に積分するコンデンサ4からなる積分器5と、積分器の電荷を放電するリセット回路6とを備える直線補間回路を有する位相合成装置およびそれを用いた位相合成方法により、コンデンサのゲイン変化やD/A変換におけるDCオフセット誤差に影響されることなく、ジッタの小さい精度の良い出力波を合成することができる。

(もっと読む)

181 - 200 / 211

[ Back to top ]