Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

161 - 180 / 211

ノイズ低減回路

【課題】 外部に高価なフレームメモリーを設けることなく雑音抑制を行うことができるノイズ低減回路を提供する。

【解決手段】 ノイズ低減回路は、複数の電荷蓄積手段2a〜2nと複数のスイッチ手段1a〜1nとを備えている。ノイズ成分を含む信号に応じた電荷量を複数の電荷蓄積手段2a〜2nに蓄積した後に、複数のスイッチ手段1a〜1nを導通させることによって複数の電荷蓄積手段2a〜2nを互いに並列に接続し、それによって、複数の電荷蓄積手段2a〜2nに蓄積されている電荷量を平均した電荷量と対応する信号を出力する。

(もっと読む)

クロック発生装置及び半導体集積回路装置

【課題】 高速動作メモリを用いる場合であっても拡散スペクトル・クロック信号を用いて、EMIを効果的に低減することができるクロック発生装置及び半導体集積回路装置を提供する。

【解決手段】 拡散スペクトル・クロック発生器210は、DDR SDRAM112Aの連続アクセスを判定し、DDR SDRAM112Aのデータ読み出し時の連続アクセスでは拡散OFFにする状態判定器220を備える。

(もっと読む)

半導体集積回路装置

【課題】 簡単な構成で高逓倍能力を持ち、高速応答を実現したクロック生成回路を備えた半導体集積回路装置を提供する。

【解決手段】 遅延回路の各段遅延信号をゲート手段で選択し初段側に帰還してリングオシレータを構成する。デコーダにより1つのゲート手段の選択信号を形成して上記ゲート手段を制御する。基準周波数信号の1周期間での上記リングオシレータの発振出力のカウンタ出力とX倍指定値との比較結果により第1レジスタで上記デコーダの入力信号を形成する。第1動作モードで上記制御回路の代表比較結果に対応してバイナリスキャンにより上記入力信号を形成する。第2動作モードでは、上記比較結果により上記入力信号に対して+1又は−1とする。

(もっと読む)

クロック検出回路

【課題】 低電圧で動作し、かつ低電圧のクロックを検出することが可能なクロック検出回路を提供すること。

【解決手段】 出力端子とGNDの間に並列に接続した第1の容量と抵抗でクロック信号入力端子に入力されるクロックを検出するクロック検出回路において、任意の電位を接続する入力端子と出力端子の間に整流素子を2個直列に接続し、整流素子の接続点とクロック信号入力端子の間に第2の容量を設けた。

(もっと読む)

クロック補正回路及びクロック補正方法並びにマイクロコントローラ

【課題】

ソフトウェア上の処理が簡略化され、コストの低減を図ることが可能なクロック補正回路を提供すること。

【解決手段】

本発明に係るクロック補正回路は、メインクロックAと、メインクロックAよりも周波数が低いサブクロックBとが入力され、メインクロックAの周波数の誤差を補正して出力するクロック補正回路であって、サブクロックBの1周期に含まれるメインクロックAのパルス数をカウントするパルス数カウンタ201と、パルス数カウンタ201がカウントしたパルス数と予め定められた基準パルス数とを用いて補正情報を算出する演算部203と、補正情報に基づいてクロック補正信号を出力する休止信号カウンタ204と、クロック補正信号に基づいてメインクロックAの出力を補正するゲート205とを有する。

(もっと読む)

AD変換器

【課題】サンプリング終了直前にパルス性の雑音が入ったとしても、その出力が全て1や全て0のデータを出力してしまうのを回避することが可能なAD変換器を提供すること。

【解決手段】本発明にかかる逐次比較型のAD変換器は、電圧比較器1と、逐次比較レジスタ2と、DA変換器3を備えている。電圧比較器1は、容量対を介して直列に接続された2以上の差動増幅器11、12を備えている。入力されたアナログ信号をサンプリングする場合には、サンプリング容量C1と差動増幅器11の間に設けられたスイッチ21、S22をオフ状態にすることにより、パルス性の雑音が伝わるのを防止している。

(もっと読む)

振幅検出回路、振幅検出方法及び光通信装置

【課題】 ピーク検出に必要なキャパシタを用いることなく時定数を大幅に小さくできる振幅検出回路を実現する。

【解決手段】 aに示す入力信号(入力in)を折り返してbに示す折り返し信号を得る。この折り返し信号波形は、入力inのハイからロウ、ロウからハイへの遷移点で入力の立ち上がり・立下り時間のためへこみqが生じており、検出した振幅値に誤差が生じる。一方、入力inを微分してcに示す微分波形を得、さらにこれを折り返してdに示す折り返し信号を得る。次に、bとdとを加算することにより、へこみqがdにより補正され、ピーク値Pに示すような入力inのピーク値に対応する平坦な出力を得ることができる。即ち、キャパシタを用いないで入力inの振幅を検出することができる。

(もっと読む)

半導体集積回路

【課題】 クロックスキューを低減し、動作マージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】 遅延回路8による遅延時間DL1とクロックツリー11による遅延時間DL11との和が、遅延回路9による遅延時間DL2とクロックツリー12による遅延時間DL12との和と等しくなるように、遅延回路8,9の遅延時間DL1,DL2が調整される。このように、予め任意に遅延時間をプログラムすることができるプログラマブル遅延回路8,9を設けたことによって、機能ブロック3,4に供給される内部電源電圧V1,V2の差が大きい場合でも、機能ブロック3,4間のクロックスキューを低減することができる。したがって、低消費電力の半導体集積回路において、クロックスキューを低減することができ、動作マージンを十分に確保することが可能になる。

(もっと読む)

電圧比較器

【課題】制御電圧の電圧変化に誤動作なく速やかに応答して正帰還(ラッチ)動作を開始ができ、且つ入力電圧の差動増幅動作への復帰が速く高速動作を行なえるようにする。

【解決手段】電圧比較器は、外部から入力される差動入力電圧Vinp、Vinnを差動電流に変換して出力する差動入力回路101と、出力電圧Voutn、Voutpを正帰還増幅するラッチ回路103と、差動入力回路101とラッチ回路103との間に接続され、第1の制御電圧Vcを各ゲートに受けるMOSトランジスタ10、11を含む第2のスイッチ回路105と、該第2のスイッチ回路105とラッチ回路103との間に接続され、第1の制御電圧Vc1と逆極性の第2の制御電圧Vc2をゲートに受けるPMOSトランジスタ12を含む第3のスイッチ回路106とを有している。

(もっと読む)

チョッパ増幅回路

【課題】回路構成が簡単であって、しかも高い信頼性を有し、低電圧で動作可能なチョッパ増幅回路を提供する。

【解決手段】チョッパ変調器1は入力信号を所定の制御信号に従ってチョッパ変調してチョッパ変調信号を出力する。スイッチドオペアンプ3の増幅回路はチョッパ変調器1から出力されるチョッパ変調信号を増幅して増幅されたチョッパ変調信号を出力する。スイッチドオペアンプ3のチョッパ復調器4は増幅回路から出力される増幅されたチョッパ変調信号を、制御信号に従ってチョッパ復調して復調された出力信号を出力端子からチョッパ増幅された出力信号として出力する。チョッパ変調器5はチョッパ復調器4から出力される復調された信号を、制御信号に従ってチョッパ変調してチョッパ変調信号を増幅手段の入力端子に出力する。

(もっと読む)

マイクロコンピュータ

【課題】温度が変化する環境下において、CR発振回路の発振出力に基づいて行われる所定の処理時間が一定となるように補正する構成を、より簡単に実現するマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータのEEPROMに、温度により変動するCR発振回路の発振出力特性に基づき、通信回路により管理される1フレームのデータ送信時間を一定とするための通信レートCMRを決定するデータを記憶しておく。CPUは、温度検出回路によって検出される温度(ステップS2)に応じてEEPROMに記憶されているデータを読み出し(ステップS3)、決定した通信レートCMR(ステップS4)を通信回路に設定する(ステップS5)。

(もっと読む)

クロックジェネレータ

【課題】 チャージポンプ回路の出力電圧変動を抑制する。

【解決手段】 PLL回路1は、位相比較器2、チャージポンプ回路・LPF部3、VCO4、及び分周器5から構成され、チャージポンプ回路・LPF部3には、チャージポンプ回路6の充電電流及び放電電流を同一にするための補正チャージポンプ電流をチャージポンプ回路6に供給するチャージポンプ電流補正回路9が設けられている。

(もっと読む)

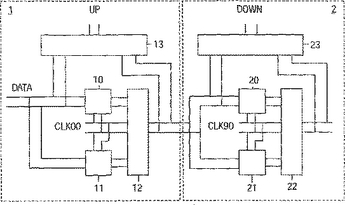

多重送信用ラッチ付き線形位相検出器

線形位相検出器は、クロック抽出器およびデータ再生器内で使用するために、第1および第2クロック信号(CLKOO,CLK90)を受信して第1および第2制御信号(UP,DOWN)を生成する回路(1,2)を備え、これらの回路は、入力および出力との間の長い経路の長さと多くの動作により大きな遅延を有する(洞察)。これらは、それぞれの回路(1,2)に2つの並列のラッチ(10,11,20,21)と、これらのラッチの出力信号を多重送信するマルチプレクサ(12,22)を与えることにより、より速くさせることが可能である(基本概念)。データ信号は第1回路(1)に供給され、第1回路出力信号は第2回路(2)に供給される。それぞれがまた2つのラッチとマルチプレクサを備える第3および第4回路(3,4)を導入することにより、高速線形位相検出器は、多数のトランジスタから独立した、データ信号におけるゲインを有するように構成されており、これは長所である。それぞれの回路(1,2,3,4)の論理回路(13,23)は、加算器/減算器(5)に結合される。  (もっと読む)

(もっと読む)

ゼロクロス検出回路

【課題】

商用電源の交流電圧に対する重畳ノイズ及び波形歪みに対して、ゼロクロスを定周期にかつ安定に検出することができるゼロクロス検出回路を実現する。

【解決手段】

交流電圧がゼロ電位をクロスするタイミングに同期したパルス信号を生成するゼロクロス検出回路において、前記交流電圧の正の半サイクル又は負の半サイクルの少なくともいずれかに同期した矩形波信号を生成する矩形波変換手段と、前記矩形波信号によりトリガされるモノステイブルマルチバイブレータ手段とを備える。

(もっと読む)

ディジタル信号受信回路

【課題】 復調信号に直流電位オフセットが生じても、ベースバンド信号を正しく再生できるディジタル信号受信回路を提供する。

【解決手段】 遅延ピーク検出部13によって、ピーク検出部11よりも遅れたタイミングで入力信号INのピークレベルを検出し、遅延ピークレベルDPLとピークレベルPLとのピーク差PLDをピーク差分検出部15で検出する。リセット部17では、ピークレベルPLとボトムレベルBLのレベル差が入力信号INの振幅に対応する所定値を越え、かつピーク差PLDが許容ピーク差PLMを越えたときに、ボトム検出部12に対するリセット信号BRSを出力する。これにより、ボトム検出部12から出力されるボトムレベルBLは、最新の入力信号INに基づいたボトムレベルに置き換えられる。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】

半導体集積回路は、位相周波数比較回路とループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する電圧を電流に変換し、変換後の電流をこれら複数のCDR回路に分配する。

(もっと読む)

チャージポンプ回路

【課題】 チャージポンプ回路に用いるスイッチング素子を低耐圧素子で構成可能とする。

【解決手段】 モードAにおいて、第1及び第2のクロックCKa,CKbを接地電圧(GND)に設定すると共に、第1のスイッチング素子SW1をオンし、第2及び第3のスイッチング素子SW2,SW3をオフする。モードBにおいて、第2のクロックCKbをGNDに維持し、第1のクロックCKaを高レベル(VDD)に変化させると共に、第2のスイッチング素子SW2をオンし、第1及び第3のスイッチング素子SW1,SW3をオフする。モードCにおいて、第1のクロックCKaをVDDに維持し、第2のクロックCKbをGNDから高レベル(VDD)に変化させると共に、第3のスイッチング素子SW3をオンし、第1及び第2のスイッチング素子SW1,SW2をオフする。

(もっと読む)

コンパレータ、信号処理装置および方法

【課題】 簡単な構成でしきい値を容易に収束させることができるコンパレータを提供し、またそのコンパレータを用いる信号処理装置および方法を提供する。

【解決手段】 センサ入力が時刻t10でしきい値のハイレベル側からローレベル側に変化すると、しきい値はハイレベル側に遷移する。センサ入力がしきい値をローレベル側に越えた瞬間に、しきい値を反転しにくい方であるハイレベル側へずらすので、時刻t10の直後にノイズが重畳されても、誤反転しにくくすることができる。センサ入力がローレベル側からハイレベル側に変化の方向を逆転する前に、しきい値が漸次設定値に近付くように、しきい値を段階的に変化させる。しきい値の有効ビット数を少なくするような場合、しきい値が設定値に達しなくても、変化量が0になってしまう。そこで、強制的にしきい値を設定値に収束させる。

(もっと読む)

パルス列生成回路

【課題】基準パルス列のパルス毎のエッジを所望位置に変更したパルス列を生成する。

【解決手段】パターン生成回路10は、エッジを変更するための基準電圧を生成する基準電圧データと、基準パルス列を生成するパターン・データを記憶し、同期して端子B及びAから夫々出力する。DAC14は、基準電圧データをデジタル・アナログ変換し、基準電圧を生成する。LPF12は、パターン・データから生成された基準パルス列のエッジをなまらせ傾斜させる。比較器16は、基準電圧とLPF12の出力を比較し、基準パルス列に比較してエッジ位置が変更されたパルス列を生成する。

(もっと読む)

感度調整機能付きシュミットトリガ回路及びそれを備える半導体装置

【課題】 シュミットトリガ回路のノイズ除去特性を安定的に維持する。

【解決手段】 入力信号のスレッシュホールドレベルを定めるVp/Vn設定部11とRSラッチ部12とからなるシュミットトリガ回路10と、シュミットトリガ回路10から出力される所定の幅以上のパルス信号を通過させるローパス・フィルタ機能を含むドライバ部13と、ローパス・フィルタ機能を含むインバータINV4に対して通過させるパルス幅を変更するように電源電圧を変更して供給する動作電流設定・センサ部14を備える。動作電流設定・センサ部14は、電源電圧を設定するための直列接続されるPchトランジスタMP2、NchトランジスタMP2を含むセンサ回路16を備え、インバータINV4は、PchトランジスタMP2、NchトランジスタMP2とそれぞれ同一形状のPchトランジスタMP1、NchトランジスタMP1で構成される。

(もっと読む)

161 - 180 / 211

[ Back to top ]