Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

81 - 100 / 211

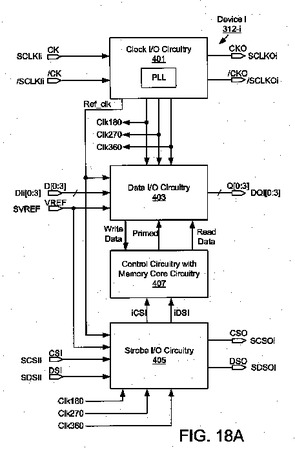

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

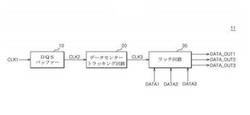

データセンタートラッキング回路及びこれを含む半導体集積回路

【課題】本発明は、外部環境の影響にも安定的に動作し、より向上した電力及び面積効率を具現するデータセンタートラッキング回路及びこれを含む半導体集積回路を提供する。

【解決手段】本発明は、直列連結した複数のクロックバッファーからなり、クロックをバッファーリングして出力信号を出力するクロックツリー;クロックに基づき、出力信号の位相の変化を感知して感知信号を出力する感知部;及び、感知信号に応じて、クロックツリーに供給される電流を調節し、出力信号の位相を調節するディレイ補償部を含む。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

半導体集積回路

【課題】発振回路により作成される動作クロックによる不要な電磁輻射ノイズを低減する。

【解決手段】乱数発生回路10から出力された乱数データは、周波数可変データレジスタ12に格納される。周波数可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。発振回路13はクロックを発生する回路であり、クロックは不図示の動作クロック作成回路を通して動作クロックとして、内部回路14に供給される。発振回路13のクロックの周波数は、周波数可変データレジスタ12に格納された乱数データに応じて可変制御されるようになっている。また、周波数可変データレジスタ12に格納された乱数データに応じて可変制御される周波数の幅を制御するための制御データが格納される周波数可変幅制御レジスタ15が設けられている。

(もっと読む)

半導体集積回路

【課題】出力信号のステップパルスに伴う、不要な電磁輻射ノイズを低減する。

【解決手段】乱数制御レジスタ11は、乱数発生回路からの乱数データの出力のスタート(開始)、スタンバイ(待機)、ストップ(停止)、出力のタイミング等を制御するためのレジスタである。乱数発生回路10から出力された乱数データは、立上り/立下り時間可変データレジスタ12に格納される。立上り/立下り時間可変データレジスタ12に格納されるデータは、乱数発生回路10から順次発生される乱数データによって更新される。出力回路13は、マイクロコンピュータの内部回路14からの信号φを外部機器に出力するための回路であり、出力回路13の出力信号の立上り/立下り時間は、立上り/立下り時間可変データレジスタ12に格納された乱数データに応じて、可変制御されるようになっている。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

半導体装置および電子機器

【課題】閾値ばらつきが大きなトランジスタを用いても正確に比較動作ができる半導体装置およびこれを備えた電子機器を提供する。

【解決手段】トランジスタ104,105を用いて入力信号VIN1,VIN2を比較する。昇圧回路100は、トランジスタ104の第1入出力端子に接続された第1入力端子CIN1と、トランジスタ105の第1入出力端子に接続された第2入力端子CIN2と、トランジスタ104のゲート端子に接続された第1出力端子COUT1と、トランジスタ105のゲート端子に接続された第2出力端子COUT2に接続とを有して、トランジスタ105のゲート端子の電圧を昇圧または降圧する。

(もっと読む)

半導体記憶装置

【課題】入力データとデータストローブクロックのタイミングにより自動的にデータ入力ストローブ信号の発生タイミングをチューニングする半導体記憶装置を提供する。

【解決手段】入力データとデータストローブクロックの入力タイミングによりデータ入力ストローブ信号の発生タイミングをチューニングする内部チューニング手段と、前記データ入力ストローブ信号に応答して、複数のデータをグローバルラインに伝送するデータ入力センスアンプとを含む。

(もっと読む)

信号発生装置

【課題】選択した所望のビットにのみジッタ又はノイズを付加した波形データを発生させる。

【解決手段】信号発生装置の表示装置の画面上に、ジッタ/ノイズ設定領域18とビット選択領域20が表示される。ビット選択領域20で選択されたビットに限定して、ジッタ/ノイズ設定領域18で設定されたジッタ又はノイズが設定される。ビットの選択方法としては、ユーザが直接選択するビット・パターンを入力するもの、ビットに対応した箱型オブジェクトを表示し、箱型オブジェクトを個別に選択することでビットを選択するもの、「01又は10」などいくつかの所定ビット・パターンをメニューから選択するもの、選択する上位の連続ビット数又は下位の連続ビット数を指定するものなどがある。

(もっと読む)

高電圧、高速、高パルス繰返し数のパルス発生器

【課題】RF電力増幅器と関連する高パルス繰返し数の制限を解決する高電圧、高速、および高繰返し数パルス発生器(30)を提供する。

【解決手段】パルス発生器(30)は共振技術を利用して、短絡および開回路の双方の負荷状態中に、パルス発生器(30)の機能障害なしに、パルス発生器(30)の継続的な高電圧、高速、および高繰返しパルス数動作を可能にする電流制限特徴をもたらす。本発明の好適な実施例において、パルス発生器(30)は、DC電圧を高周波AC電圧に変換するように構成されているインバータ(40)と、前記AC電圧に応答して、AC電流源として動作するように構成されているコンバータ(50)と、前記AC電流源によって発生するAC入力電流に応答して、高電圧、高速、高繰返し数電圧パルスを発生させるように構成されているパルス整形部分(60)とを備える。

(もっと読む)

半導体素子制御装置

【課題】電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

(もっと読む)

回転方向判別装置

【課題】 第1のパルス信号が第2の値に反転する時刻と、第2のパルス信号が第2の値に反転する時刻との間の時間が短い場合であっても、正確にロータリースイッチの回転方向を判別すること。

【解決手段】 パルス信号A及びパルス信号Bの一方がローレベルに反転してから、他方のパルス信号がローレベルに反転するまでの時間が所定時間未満である場合、パルス信号A及びパルス信号Bのうち、どちらのパルス信号が先にハイレベルからローレベルに反転したかによって回転方向を判別せずに、どちらのパルス信号が先にハイレベルからローレベルに反転したかによって回転方向を判別する。従って、回転方向を正確に判別することができる。

(もっと読む)

フィルタ回路および方法

【課題】サンプリングクロックに同期して順次入力されるデジタルデータに連続したサンプリング周期にわたって混入したノイズをも除去するノイズ除去回路および方法を提供。

【解決手段】ノイズ除去回路1は、3つの遅延された入力データ(21、22、23)のうちのそれぞれ2つの平均(24、25、26)を算出し、これらの平均値のいずれが前回選択された出力データ(31)の値に対して最小の差(27、28、29)を有するかを判定し、最小の差を有する減算器データ(32)に対応する加算器(5、6、7)が出力する平均値(24、25、26)をフィルタ済出力信号値31として出力することにより、入力信号20に連続したサンプリング周期にわたり混入したノイズを除去する。

(もっと読む)

入力インタフェース回路、集積回路装置および電子機器

【課題】信号入力端子に静電気ノイズが印加された場合に、そのノイズの内部回路への伝達を未然に、かつ確実に防止することができる入力インタフェース回路を提供すること。

【解決手段】ノイズを検出するノイズ検出回路(200)と、ノイズが検出されたときに第1のスイッチ回路(SW1)をオフしてノイズ伝達を遮断する機能をもつノイズキャンセラ(300)と、を設ける。第1のスイッチ回路(SW1)がオフしているときは、第2のスイッチ回路(SW2)がオンして、直前の電圧をラッチする。ノイズ検出回路200に含まれるノイズ検出用トランジスタは、Nウエルの電位を適応的に最適化することができるフローティングNウエルトランジスタによって構成される。

(もっと読む)

データスライス回路及びデータ復元回路

【課題】復調信号の最初のパルスから確実にデータを復元することが可能なデータスライ

ス回路を提供する。

【解決手段】データスライス回路3は、レベルシフト回路5と基準電圧生成回路6とコン

パレータ7とにより構成されている。レベルシフト回路5は、入力信号SIの電圧レベル

を一定電圧レベルだけシフトしたレベルシフト電圧SLを生成し、基準電圧生成回路6は

、入力信号のピーク電圧及びボトム電圧を分圧した基準電圧SBを生成する。コンパレー

タ7は、レベルシフト電圧SLと基準電圧SBとを比較した結果を出力する。

(もっと読む)

クロックデータリカバリー回路及び通信装置

【課題】LSI化に適し且つ従来のPLLを用いたのと同等の特性を設定できるシリアルデータインターフェースのCDR回路を提供する。

【解決手段】本発明のCDR回路は、所定周波数のクロックの周期T1をN分割したT2時間ずつずらしたN相のクロックを出力する手段、シリアル転送されたデータをT2時間毎にサンプリングする手段、サンプリングしたデータを周期T1毎に第1のNビットパラレルデータに変換する手段、サンプリングしたデータのデータ変化点を示す第2のNビットパラレルデータに変換する手段、及び、第2のNビットパラレルデータを位相情報入力としてシリアルデータのデータ変化点の略中間位置を示す第3のNビットパラレルデータを出力する手段を有し、第3のNビットパラレルデータが示したビット位置と同じ、第1のNビットパラレルデータのビット位置データを復元データとすることを特徴とする。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

クロックスキューコントローラ及びそれを備える集積回路

【課題】クロックスキューを補償することができるコントローラを備える集積回路を提供する。

【解決手段】第1クロックマッシュに入力される第1クロックと第2クロックマッシュに入力される第2クロックとの間のスキューを調節するためのクロックスキューコントローラを備える。クロックスキューコントローラは、第1出力クロックと第2出力クロックとの間の遅延時間に対応するパルス信号を発生するパルス発生器と、パルス信号のパルス幅に対応するデジタル信号を出力するパルス幅検出器と、デジタル信号に対応する時間だけ、第1及び第2クロックのうちのいずれか一つを遅延させるクロック遅延調節器と、を備えて、クロックマッシュの間のクロックスキューを検出し、該検出されたスキューに対応する遅延時間だけクロックマッシュに供給されるクロック等の遅延時間を調節することができる。

(もっと読む)

電圧制御発振回路

【課題】動作が誤発振状態または準安定状態となったことを検出し、誤発振状態または準安定状態から抜け出して正常な発振状態にとすることができるVCOをを提供する。

【解決手段】本発明の電圧制御発振回路は、互いに逆相の差動のクロック信号が入力される差動遅延素子を縦続接続し、バイアス電圧によって差動遅延素子に流れる電流の量を制御することで、該差動のクロック信号の遅延量を制御する差動リングオシレータ型の電圧制御発振回路であり、いずれかの差動遅延素子の差動出力の出力電圧と、異常動作を検出する電圧に設定されたリファレンス電圧とを比較することにより異常発振を検出して検出信号を出力する位相検出部と、差動遅延素子毎に設けられ、検出信号が入力されると、差動出力対間の電位差を増幅するクロスカップル回路とを有している。

(もっと読む)

パルス検出回路、包絡線検出回路、および、電子装置、ならびに、パルス検出方法

【課題】IRのような素子性能の限界に及ぶ超高周波域で良好に動作し消費電力が少なく安価で信頼性が高く且つ通常のCMOS半導体プロセスで製造可能な新たなルス検出回路、包絡線検出回路および電子装置ならびにパルス検出方法を提供することを目的とする。

【解決手段】ゲートおよびドレインを短絡したMOSトランジスタ103(108)が介挿された負帰還路を有する増幅回路20a(20b)と、増幅回路の入力端に一端側が接続され他端側が被検出信号が供給される信号入力端として設定されたコンデンサ105(110)とを含み、信号入力端に供給される被検出信号(Vs)の波形をその変動における一方の極性側のピークレベルが略一定に揃い且つ他方の極性側に向けて当該変動に相応する振幅変化を呈する波形に変換する信号波形変換部と、信号波形変換部10a(10b)の出力信号から被検出信号が担うパルスを検出するパルス検出部とを備える。

(もっと読む)

81 - 100 / 211

[ Back to top ]