Fターム[2G132AL00]の内容

電子回路の試験 (32,879) | 目的、その他 (6,788)

Fターム[2G132AL00]の下位に属するFターム

被試験体の識別、存在の検知 (22)

接続の確実化 (517)

接続の確認、誤接続の検出 (109)

接続線の本数の減少(端子数の減少) (295)

多品種への対応(汎用性のあるもの) (130)

試験時間の短縮 (1,339)

試験精度の向上 (1,554)

不良箇所、原因の特定等 (520)

試験装置の調整 (288)

インピーダンスマッチ (76)

温度調整 (87)

レベル変換 (8)

複数の被試験体の試験 (254)

母線(バス等)に接続した状態での試験 (19)

異常時の処理、保護 (119)

低機能装置で高機能素子を試験 (203)

試験装置の構成要素の配置改善 (287)

試験装置の動作試験 (78)

試験方法としては一般的なもの (13)

Fターム[2G132AL00]に分類される特許

21 - 40 / 870

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体試験装置、半導体試験方法及びプログラム

【課題】ウェハに含まれる半導体集積回路の電気的特性の測定には、測定対象となる全ての半導体集積回路が専用の測定回路を備えている必要があるが、全ての半導体集積回路に対して専用の測定回路を配設すると、半導体集積回路の面積が増加してしまう問題がある。そのため、半導体集積回路の面積を増加させることなく、半導体集積回路の電気的特性の測定を可能とする半導体試験装置が望まれる。

【解決手段】半導体試験装置は、第1の半導体集積回路と、電気的特性を測定するための測定回路及び測定端子と、前記測定回路に近接する第2の半導体集積回路と、を含むウェハの特性の測定を行う測定部と、第2の半導体集積回路に対して実施するウェハテストから得られる第1の電気的特性と、測定端子から測定した第2の半導体集積回路についての第2の電気的特性と、の相関に基づいて第1の半導体集積回路について第2の電気的特性を推定する制御部と、を備えている。

(もっと読む)

試験装置および試験方法

【課題】被試験デバイスから出力されるクロック信号を取得して試験する。

【解決手段】被試験デバイスが出力するデータ信号を被試験デバイスが出力するクロック信号に応じたサンプリングクロックに応じたタイミングまたは当該試験装置の試験周期に応じたタイミング信号のタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、データ取得部がサンプリングクロックに応じたタイミングまたはタイミング信号に応じたタイミングの何れによりデータ信号を取得するかを指定する指定部と、を備える試験装置を提供する。

(もっと読む)

位相特性推定装置並びにそれを備えた位相補正装置及び信号発生装置並びに位相特性推定方法

【課題】試験対象の周波数範囲全体にわたって位相特性を推定して位相特性の平坦化に資することができる位相特性推定装置並びにそれを備えた位相補正装置及び信号発生装置並びに位相特性推定方法を提供する。

【解決手段】信号発生装置1は、互いに異なる周波数の2つのCWを合成した合成CWを出力する信号出力部10と、合成CWを直交変調して直交変調信号を出力する直交変調器16と、直交変調信号の電力レベルを調整するレベル調整器20と、位相特性を推定する位相特性推定器30とを備え、位相特性推定器30は、合成CWの振幅値に基づいて隣接間位相差を算出する位相差算出部31と、隣接間位相差のデータに基づいて所定の周波数帯域における位相特性を推定する位相特性推定部33とを備える。

(もっと読む)

試験装置および試験方法

【課題】精度良く試験をする。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、被試験デバイスがクロック信号を出力しない期間において、データ取得部によるデータ取得をマスクするマスク部と、データ取得部が取得したデータ信号を期待値と比較した結果に基づいて、被試験デバイスの良否を判定する判定部と、を備える試験装置を提供する。

(もっと読む)

試験装置および試験方法

【課題】確実にデータを取り込んで試験する。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、被試験デバイスが出力するデータ信号をクロック信号に応じたタイミングで取得する取得部と、複数のエントリを有し、クロック信号に応じたタイミングにおいて取得部により取得されたデータ信号を順次各エントリにバッファリングし、当該試験装置の試験周期に応じて発生されるタイミング信号のタイミングで各エントリにバッファリングしたデータ信号を出力するバッファ部と、バッファ部から出力されたデータ信号を期待値と比較する判定部とを備える試験装置を提供する。

(もっと読む)

エミュレータ及びデバッグ方法

【課題】JTAG-ICEにおいて、LSIの入出力状態をトリガとするエミュレーションのブレークを実現する「エミュレータ及びデバッグ方法」を提供する。

【解決手段】エミュレーション処理部23は、LSI31のICE制御ブロック314に命令を発行し、所定のプログラムをコアロジック311に実行させ、スキャン処理部24は、LSI31のコアロジック311のプログラムの1ステップ実行毎のスキャン動作を、LSI31のバウンダリスキャン制御ブロック315に行わせ、LSI31の各入出力端子312の状態をスキャンデータメモリ25に格納する。エミュレーション処理部23は、スキャンデータメモリ25からLSI31の各入出力端子312の状態を読み出し、読み出した各入出力端子312の状態が、予めブレーク条件メモリ26に設定されているブレーク条件にマッチするかどうかを調べ、マッチしていればプログラムの実行をブレークする。

(もっと読む)

スイッチ装置、伝送路切り替え装置、製造方法、および試験装置

【課題】剛性を高めつつ、物理的な破壊を防いだアクチュエータを提供する。

【解決手段】スイッチ装置は、第1接点122が設けられた基体110と、第2接点134を移動させて第1接点122と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層150と、支持層150上に形成され、第1駆動電圧に応じて伸縮する第1圧電膜136と、第1圧電膜136上に絶縁材料で形成され、第1圧電膜136の端部の少なくとも一部において支持層150と接して端部を覆う第1保護膜152と、を有する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

電子部品試験装置、ソケットボード組立体、及びインタフェース装置

【課題】被試験電子部品の品種切替時における作業性の向上を図ることが可能な電子部品試験装置を提供する。

【解決手段】電子部品試験装置1は、DUT90が電気的に接続されるDSA10と、DSA10が着脱可能に装着されるハイフィックス30と、ハイフィックス30が着脱可能に装着されるテストヘッド60と、を備えており、ハイフィックス30は、DSA10に係合するフック431を有し、DSA10は、フック431が係合するフック受け部222と、ハイフィックス30に向かって進退可能なプッシュピン24と、を有し、フック431には、プッシュピン24が当接するピン受け部433が形成されており、プッシュピン24がピン受け部433を押圧することで、フック431の係合が解除される。

(もっと読む)

スイッチ装置および試験装置

【課題】圧電膜の変位を大きくして動作させるスイッチ装置を提供する。

【解決手段】スイッチ装置100は、第1接点122が設けられた接点部120と、第2接点134を有し、第2接点134を移動させて第1接点122と接触または離間させるアクチュエータと、第1駆動電圧を制御する制御部200と、を備え、アクチュエータは、第1駆動電圧に応じて伸縮する第1圧電膜136と、第1圧電膜136上に設けられる支持層と150、を有し、制御部200は、第1圧電膜136に第1の抗電界以下の電界を印加する電圧から、第1圧電膜136に第1の抗電界以上の電界を印加する電圧まで変化させて第1圧電膜136を縮ませ、第1圧電膜136に第2の抗電界未満の電界を印加する電圧を出力して第1圧電膜136を伸ばす。

(もっと読む)

検査システム及びそれを用いた半導体装置並びに検査方法

【課題】 回路面積の増大が少なくコスト増を抑えることが可能な検査システムの提供。

【解決手段】 検査回路3は、第1の回路1と第2の回路2の間に介在する。また、検査回路3は、信号伝達制御機能4と検査出力機能5とを含んでいる。信号伝達制御機能4は、第1の回路1と第2の回路2の間の信号伝達を制御する。また、検査出力機能5は、検査回路3を介し、第1の回路1の出力を検査用に出力する。本発明では、信号伝達制御機能4と検査出力機能5は、互いの機能を実現する回路の一部を共有している。また、第1の回路1と第2の回路2と検査回路3は、同一の基板上に設けられている。検査回路3は信号伝達制御機能4と検査出力機能5とを切り替えて使用する。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

高電圧検査装置

【課題】高耐圧リレーを用いることなく全体構成を簡略化して、規格に適合した電流波形(または電圧波形)で高電圧印加試験を行う。

【解決手段】一または複数の検査対象デバイスに対してESD耐性を検査する本実施形態3のESD試験装置1Dにおいて、一または複数の検査対象デバイス54を搭載したコンタクトステージ53の上下動作により、スイッチ手段としてのスイッチ52がオン/オフして、一または複数の検査対象デバイス54に1対1に対応する各高電圧容量手段としての高圧コンデンサ56の高電圧を充電/放電し、各高圧コンデンサ56からの放電により当該一または複数の検査対象デバイス54のESD検査を行う。

(もっと読む)

画像表示装置

【課題】画像表示装置において、テスト画像を表示させるための画素駆動信号の出力波形をテストパッドを介して取り出せるようにする。

【解決手段】画像表示装置の水平走査用(ソース駆動用)の画素駆動部4は、画素駆動信号を出力するソースドライバICチップ31、ソースドライバICチップ31から出力される画素駆動信号をディスプレイの画素に供給する出力ライン32、及びテストパッド33がフィルム34上に設けられたチップオンフィルム組立体である。テストパッド33−1、33−2、33−3、33−4は、出力ライン32−1、32−4、32−681、32−684に設けられている。出力ライン32−1〜32−3は、ディスプレイの画素に接続されず、出力ライン32−4〜32−684は、ディスプレイの第1〜第681列目の画素列の各画素に接続される。テスト画像として、ディスプレイの最端の画素列を発光させることによる画像を表示する。

(もっと読む)

半導体試験装置および実装補助部材

【課題】半導体試験装置のネストにプリント基板の挿抜する作業中に隣接する他のプリント基板に接触することを防止できるようにする。

【解決手段】ネスト開口部から開口部奥の装着位置までプリント基板を案内する複数のガイドレールを備えた半導体試験装置であって、ガイドレールが開口部外部方向に伸びる機構を備えた半導体試験装置。ネスト開口部から開口部奥の装着位置までプリント基板を案内する複数のガイドレールを備えた半導体試験装置であって、ガイドレールが開口部外部方向にスライドする機構を備えるようにしてもよい。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

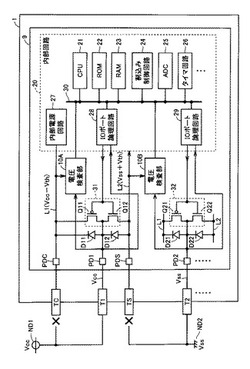

マイクロコンピュータ

【課題】アプリケーションプログラムの完成前に、システム全体の電源回路の最適化が可能なマイクロコンピュータを提供すること。

【解決手段】本発明に係るマイクロコンピュータ100は、CPU101と、CPU101に接続されたバス107と、バス107に接続される通常動作モードと、バス107と遮断される擬似動作モードと、を備える機能ブロック103A〜103Cと、通常動作モードと前記擬似動作モードとのいずれかを選択するための制御信号を出力する選択回路102と、を備え、機能ブロック103A〜103Cが、擬似動作モードにおいて消費電流を生成する擬似動作回路105A〜105Cと、を備えるものである。

(もっと読む)

基板検査装置および基板検査方法

【課題】基板に形成された凹部の深度を、非破壊、非接触で検査できるとともに、高速に検査できるようにする技術を提供する。

【解決手段】基板検査装置100は、ポンプ光の照射に応じて、基板Wに向けてテラヘルツ波を照射する照射部12と、プローブ光の照射に応じて、基板Wを透過したテラヘルツ波の電場強度を検出する検出部13と、テラヘルツ波が検出部13に到達する時間と、検出部13における検出タイミングを遅延させる遅延部14とを備える。また、基板検査装置100は、基板Wの第1領域を透過した第1テラヘルツ波の時間波形を構築する時間波形構築部21と、基板Wの第2領域を透過した第2テラヘルツ波について、特定の検出タイミングで検出される電場強度と、前記時間波形とを比較することにより、第1テラヘルツ波と第2テラヘルツ波の位相差を取得する位相差取得部24とを備える。

(もっと読む)

21 - 40 / 870

[ Back to top ]