Fターム[5J500AK00]の内容

増幅器一般 (93,357) | 回路要素 (18,409)

Fターム[5J500AK00]の下位に属するFターム

演算増幅器(オペアンプ) (1,028)

差動増幅器 (1,173)

インピーダンス変換器(緩衝、バッファ) (308)

反転増幅器(インバータ) (390)

記号又は1本の抵抗の定電流源 (1,226)

その他の定電流源 (132)

記号の可変電流源 (128)

その他の可変電流源 (54)

カレントミラー (1,040)

定電圧発生回路 (216)

バイアス回路 (978)

共振回路、共振器 (109)

同調回路 (26)

遅延回路 (472)

移相器 (300)

電圧、電流比較器 (652)

レベルシフト回路 (119)

ホールド回路 (118)

リミッタ回路 (138)

クランプ回路 (51)

クリップ回路 (27)

減衰回路、アッテネータ (352)

ブートストラップ回路 (4)

時定数回路 (22)

加減算回路 (584)

I−V変換 (156)

電流検出器 (143)

整合器 (603)

微分回路 (12)

積分回路 (193)

発振回路 (358)

デジタル回路(パルス回路) (1,577)

フィルタ (1,427)

単一電源 (565)

複数電源 (153)

電源の切換え、可変電源 (118)

整流回路 (99)

変調器 (588)

復調器、検波器 (416)

チョッパ (20)

直流交流変換(インバータ) (3)

負性抵抗特性を持つ回路 (5)

特徴のあるアース回路 (12)

ジャック、プラグ、コネクタ (24)

スピーカ (516)

ヘッドホン、イヤホン (50)

マイク (49)

冷却装置 (28)

プリント基板 (90)

指示、表示 (15)

その他のマイクロ波要素 (616)

Fターム[5J500AK00]に分類される特許

141 - 160 / 926

可変利得増幅回路

【課題】入出力範囲を電源電圧まで可能とする。

【解決手段】入力段に第1の演算増幅器51が、出力段に第2の演算増幅器52が、それぞれ配されると共に、第1の演算増幅器51の帰還路に第1のトランスコンダクタンス増幅器53が、第1及び第2の演算増幅器51,52の間に、第2のトランスコンダクタンス増幅器54が、それぞれ配されてなり、第1の演算増幅器51には第1の抵抗器61を介して入力信号を印加可能とし、その第1の抵抗器51に流れる電流と、第1の演算増幅器51の負帰還電流を等しくする一方、第2の演算増幅器52の入出力端子間に第2の抵抗器62を設けると共に、第2の演算増幅器52には、その終段がフルスイング可能に構成されたものを用い、第2の抵抗器62に流れる電流と第2のトランスコンダクタンス増幅器54の出力電流を等しくすることで、入出力範囲が電源電圧まで広げられたものとなっている。

(もっと読む)

送信回路及び通信機器

【課題】小型かつ高効率に動作し、高精度に遅延誤差を補償する送信回路を提供する。

【解決手段】信号生成部11は、AMテスト信号及びPMテスト信号を出力する。AMテスト信号は、遅延調整部12とレギュレータ14を介して、乗算器16に入力される。PMテスト信号は、遅延調整部12を介して乗算器16に入力される。電力測定部17は、乗算器16から出力された乗算信号の平均電力を測定し、制御部18に出力する。制御部18は、入力された測定値に基づいて、振幅遅延時間及び位相遅延時間を決定し、遅延調整部12に設定する。

(もっと読む)

周波数変換回路

【課題】変換利得のばらつきを極めて小さく抑制された周波数変換回路を実現する。

【解決手段】入力電圧信号を電流信号に変換するGMアンプ10と、該変換して得られた電流信号をローカル信号でミキシングして周波数変換を行うスイッチング回路部(ミキサ)20と、該周波数変換によって得られた電流信号を電圧信号に変換するIV変換部(IV変換アンプ)30と、GMアンプ10へバイアス電圧を供給するバイアス回路(GM校正回路)40と、を備えGM校正回路40は、GMアンプ10に用いるトランジスタとそのサイズあたりの相互コンダクタンスを同一としたトランジスタを用いたレプリカアンプを内部に有し、該レプリカアンプに、抵抗と第1電流源からの電流との積に相当するDC電圧を入力し、該レプリカアンプからの電流出力が所定値になるように、該レプリカアンプの電圧バイアスを設定し、抵抗の分割点の電圧をGMアンプ10に供給する。

(もっと読む)

誤差増幅器

【課題】誤差増幅器における、受動素子の定数のばらつきに起因する帰還回路の定数のばらつきを抑制する。

【解決手段】誤差増幅器における帰還回路の定数が、受動素子の定数だけでなく、能動素子の利得にも依存して決定される構成にする。この誤差増幅器は、能動素子である電圧電流変換器20を含む構成である。また、第1の端子11、第2の端子13、オペアンプ16、第1の抵抗R1、第2の抵抗R2、第1乃至第5のトランジスタ、第1の電流源14および第2の電流源15を一体の集積回路とし、コンデンサC1を外付けしてもよい。

(もっと読む)

バースト光受信器

【課題】ATC回路を不要とし、かつ受信感度特性に優れたバースト光受信器を得る。

【解決手段】バースト光受信器1において、光バースト信号を電流信号に変換する受光素子2と、電流信号を電圧信号に変換する差動型トランスインピーダンスアンプ回路3と、差動型トランスインピーダンスアンプ回路3からの電圧信号を識別する差動型識別回路4と、一端が電源に接続され他端が受光素子2のカソードに接続された誘導性素子62と、一端が受光素子2のアノードに接続され他端がGNDに接続された誘導性素子61と、一端が誘導性素子62と受光素子2との接続端に接続され他端が差動型トランスインピーダンスアンプ回路3に接続された容量性素子52と、一端が誘導性素子61と受光素子2との接続端に接続され他端が差動型トランスインピーダンスアンプ回路3に接続された容量性素子51と、を備える。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

差動信号生成回路及び周波数変換回路

【課題】差動信号生成回路におけるS/N比の改善を図ること。

【解決手段】差動信号生成回路31は、入力されたRF信号を増幅するソース接地回路311と、増幅されたRF信号の差動信号RF+,RF−を生成するドレイン接地回路312と、生成された差動信号RF+,RF−の位相差を調整する容量部313とを備えて構成される。また、ドレイン接地回路312における第1の抵抗R1及び第2の抵抗R2によって、差動信号RF+,RF−の振幅が同じとなるとともに、容量部313によって、差動信号RF+,RF−の位相差がほぼ180度となるように調整される。

(もっと読む)

電力増幅回路及びフロントエンド回路

所定の送信信号に依存する前置増幅されたドライバー信号(S_DR)を供給するよう適用可能なドライバー段(DR)を備えた電力増幅回路(DIPPA)である。電力増幅回路(DIPPA)はまた、ドライバー段(DR)に電気的に結合されていて、ドライバー信号(S_DR)を第1及び第2の信号(S_1、S_2)へと分離するよう適用可能な周波数選択器(DIP)を備える。第1の信号(S_1)は第1の所定の周波数帯に対応付けられており、第2の信号(S_2)は第2の所定の周波数帯に対応付けられている。電力増幅回路(DIPPA)は、少なくとも第1及び第2の電力増幅段(PA1、PA2)を備える。第1及び第2の電力増幅段(PA1、PA2)は、周波数選択器(DIP)に電気的に結合される。第1及び第2の電力増幅段(PA1、PA2)は、それぞれ第1及び第2の信号(S_1、S_2)に依存する、それぞれ第1及び第2の増幅された信号(S_A1、S_A2)を供給する。 (もっと読む)

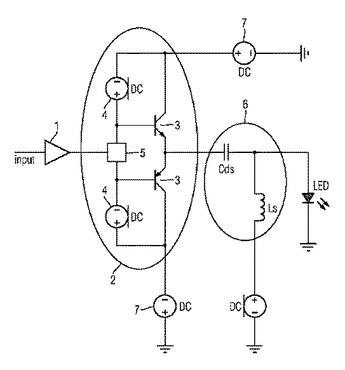

高い出力性能とコンパクトな構造を有する広帯域高線形性LED増幅器

本発明は、発光ダイオードを駆動制御する増幅回路に関する。この増幅回路は、約3オームの小さい出力インピーダンスと、200KHzの下方境界周波数と例えば5MHzの上方境界周波数とを備えた広い帯域幅と、例えば数100mAの出力電流振幅とを有する。この増幅回路は、直流電流供給部(6)によって発光ダイオードを駆動制御するドライバー回路(2)を駆動制御する入力段を有している、という特徴を有している。  (もっと読む)

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

送信回路及び通信機器

【課題】AM/PM歪みを補償し、低歪みかつ高効率に動作する送信回路を提供する。

【解決手段】補償部22は、LPF14,15を通過したIPL、QPL信号のベクトルの大きさを示す振幅信号Mを算出することで、IP',QP'信号がLPF12,13を通過することによって発生する高周波信号Piの包絡線の変動を予測する。補償部22は、算出した振幅信号Mに基づいて、位相補償量θcompを算出し、位相信号θに位相補償量θcompを加算する。

(もっと読む)

増幅装置

【課題】増幅器の振幅歪み、位相歪みを補償する手段を備えることで、高効率で、かつ低歪みな増幅装置を得る。

【解決手段】変調波入力信号を増幅する高周波電力増幅器7と、前記変調波入力信号から包絡線信号を検出する第1の包絡線検出器3と、前記高周波電力増幅器の出力信号を検出する出力信号検出手段100と、前記出力信号検出手段の出力から包絡線信号を検出する第2の包絡線検出器101と、第1と第2の包絡線検出出力を比較して誤差を検出する比較器12と、前記比較器からの誤差信号をデルタ変調するデルタ変調器40と、前記デルタ変調器の出力を増幅するスイッチング増幅器5と、前記スイッチング増幅器の出力を帯域制限する低域通過フィルタ6とを備え、前記高周波電力増幅器7は、前記低域通過フィルタ6の出力を電源電圧として、前記変調波入力信号を増幅する。

(もっと読む)

電荷を電圧に変換するシステムおよびこのシステムを制御する方法

【課題】最終変換利得を低減させることなく、変換デバイスを制御する方法を提供する。

【解決手段】本発明は、増幅器と、増幅器の入力と出力の間に負帰還で取り付けられた少なくとも1つのキャパシタとを含み、それによって前記増幅器を、前記増幅器から電荷を受け取る少なくとも1つの入力段と前記増幅器へ電圧を送る少なくとも1つの出力段との間に接続でき、前記電圧が、入力で受け取った電荷を表す、電荷を電圧に変換するデバイスを制御する方法であって、前記方法が、入力で受け取った電荷の電圧変換を含む少なくとも1つの段階(62)を含む、方法に関する。本発明によれば、変換段階は少なくとも、増幅器が入力段に接続され、また増幅器が出力段から切断される、1つの第1の副段階(64)と、増幅器が入力段から切断され、また増幅器が出力段に接続される、その後の第2の副段階(66)とを含む。

(もっと読む)

ダイナミックバイアスを有するRFバッファ回路

電圧制御発振器(VCO)に対するRFバッファ回路は、出力電圧波形の位相を選択的にフリップするために、ダイナミックバイアス回路を含んでいる。CMOSインプリメンテーションにおいて、PMOS/NMOSペアは、出力パス内に採用される。ハイ(電圧)スイングモード状態の最中に、出力の位相は、出力波形がPMOS/NMOSペアのゲートに出現する電圧に対して同相となるようにフリップされる。本技術は、それによって、ゲート−ドレイン間電圧を減少させ、低位相ノイズ及び低消費電力にしたがった構成内のMOSデバイスの改善された信頼性を許容する。  (もっと読む)

(もっと読む)

オーディオ増幅器

【課題】オーディオ増幅器を提供すること。

【解決手段】オーディオ増幅器は補償部、出力部、及び計測部を含む。補償部は、デジタル入力信号、デジタル基準コード、モード信号、及びデジタル近似コードに基づいて補償信号を生成する。出力部は補償信号に基づいて出力信号を生成する。計測部は、出力信号及びモード信号に基づいて連続近似方法でデジタル近似コードの各ビットを次々と生成する。

(もっと読む)

電力増幅回路

【課題】 出力段のトランジスタの消費電力が極力少なくなるように電源電圧の切り換えを行うことが可能であり、かつ、常に安定して適切なタイミングで電源電圧の切り換えが行われるように設計するのが容易な電力増幅回路を提供する。

【解決手段】 チャージポンプ1は、少なくとも2種類の電源電圧のうちの1種類の電源電圧を選択して発生して負荷駆動部2に供給可能であり、負荷駆動部2に供給される電源電圧CPVDDおよびCPVSSに対して負荷駆動部2の出力信号AMPOのレベルが所定限度を越えて接近したことを示す出力状態検出信号DETOが出力状態検出部3から出力されたとき、負荷駆動部2に供給する電源電圧CPVDDおよびCPVSSをより高い電源電圧に切り換える。

(もっと読む)

電力増幅回路

【課題】音源から与えられるオーディオ信号を複数段のアンプにより順次増幅して出力するオーディオアンプにおいて、それら複数のアンプの全てにオフセットキャンセル回路を設けることなく、ポップノイズを緩和することを可能にする。

【解決手段】電子ボリュームの役割を果たすプリアンプと当該プリアンプにより増幅されたオーディオ信号の信号レベルをスピーカ駆動に適した信号レベルまで増幅して出力するパワーアンプとを備えたオーディオアンプにおいて、パワーアンプにのみオフセットキャンセル回路を設ける。このオーディオアンプの起動時には、まず、プリアンプをミュートした状態でオフセットキャンセル回路を作動させ、その後、増幅率を最小値から利用者により設定された再生音量に応じた値まで時間の経過とともに増加させつつ、音源から与えられるオーディオ信号を増幅して出力する処理を上記プリアンプに実行させる。

(もっと読む)

3−レベルパルス幅変調増幅器及びこれを含むオーディオ処理装置

【課題】3−レベルパルス幅変調器及びこれを含むオーディオ処理装置を提供すること。

【解決手段】ハーフ−ブリッジ3−レベルPWM増幅器が開示される。ハーフブリッジ3−レベルPWM増幅器はプリスケーリング部、PWM生成器及び出力ステージを含む。PWM生成器はプリスケーリング部から提供されるスケーリングされた信号の大きさによって3−レベルパルス幅変調信号を生成する。出力ステージは3−レベルパルス幅変調信号に基づいて出力ノードを駆動する。

(もっと読む)

電力増幅回路

【課題】 出力信号波形にクリップを生じさせぬように常に安定して適切なタイミングで電源電圧の切り換えを行うことができる電力増幅回路を提供する。

【解決手段】 負荷駆動部1は、負荷を駆動する出力信号AMPOを発生して出力端子102に与える差動増幅器10と、入力端子101および出力端子102間の電圧を抵抗R1aおよびR2aにより分圧して差動増幅器10の逆相入力端子に与える分圧回路11と、入力端子101の入力信号AMPOと基準レベルとの間の電圧を抵抗R1bおよびR2bにより分圧した信号を逆相化して差動増幅器10の正相入力端子に与える分圧回路12とを有する。電源制御回路2は、差動増幅器10の正相入力端子に与えられる信号Vpの振幅が閾値を越えた場合に差動増幅器10に供給する電源電圧VDDおよびVSSを電源電圧±V1からより大きい電源電圧±V2に切り換える。

(もっと読む)

D級増幅器

【課題】簡易で均一なスイッチングを可能にするD級増幅器を提供することを目的とする。

【解決手段】第1のトランジスタと、2のトランジスタと、パルストランスと、第3のトランジスタと、第4のトランジスタと、搬送波信号のタイミングを、制御信号に従って調整するタイミング調整部と、電源と、第1のトランジスタおよび第4のトランジスタがオンのとき、または、第2のトランジスタおよび第3のトランジスタがオンのときに、出力側端子から出力信号を出力する出力トランスと、出力トランスの入力側の両端に現れる第1の信号および第2の信号を用いて、タイミング調整部が搬送波信号のタイミングを調整するための制御信号を生成する制御信号生成部とを有する。

(もっと読む)

141 - 160 / 926

[ Back to top ]