半導体装置、及び半導体装置の特性劣化検出方法

【課題】半導体装置の故障に繋がるような特性劣化を検出することができる半導体装置、及び半導体装置の特性劣化検出方法を提供することである。

【解決手段】本発明にかかる半導体装置(IPD)1は、IPD1の初期特性値に基づき定められた設定値を記憶する設定値記憶部3と、所定のタイミングにおけるIPD1の特性値と設定値記憶部3に記憶された設定値とに基づき、IPD1の特性劣化を検出する検出回路4と、を備える。また、本発明にかかる半導体装置(IPD)1の特性劣化検出方法は、初期特性値に基づき定められた設定値を記憶し、所定のタイミングにおけるIPD1の特性値と記憶された設定値とに基づき、IPD1の特性劣化を検出する。

【解決手段】本発明にかかる半導体装置(IPD)1は、IPD1の初期特性値に基づき定められた設定値を記憶する設定値記憶部3と、所定のタイミングにおけるIPD1の特性値と設定値記憶部3に記憶された設定値とに基づき、IPD1の特性劣化を検出する検出回路4と、を備える。また、本発明にかかる半導体装置(IPD)1の特性劣化検出方法は、初期特性値に基づき定められた設定値を記憶し、所定のタイミングにおけるIPD1の特性値と記憶された設定値とに基づき、IPD1の特性劣化を検出する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置、及び半導体装置の特性劣化検出方法に関し、特に所謂インテリジェントパワーデバイス(IPD)である半導体装置の特性劣化を検出する半導体装置、及び半導体装置の特性劣化検出方法に関する。

【背景技術】

【0002】

大きな電力を扱うことが可能なデバイスの一つにパワーMOSFETがある。このパワーMOSFETは、他のパワーデバイスと比べてスイッチング速度が早い等の特徴がある。

【0003】

特許文献1には、電源供給回路のオン、オフを切り替えるスイッチング素子として用いられる半導体素子(パワーMOSFET)のオン故障の兆候を検出し、回路の遮断機能が不能となる前の時点で半導体素子をオフすることにより、電力供給回路を保護することが可能な、電力供給回路のオン故障検出装置が開示されている。特許文献1に開示されている技術では、パワーMOSFETのゲートにゲート抵抗を設け、パワーMOSFETがオンしているときのゲート抵抗の電圧降下を測定することで、絶縁破壊に起因したオン故障を事前に察知することができる。

【0004】

また、特許文献2には、パワーMOSFETが半故障の状態でも故障判定できる故障検知回路に関する技術が開示されている。特許文献2に開示されている技術では、パワーMOSFETを用いたスイッチングモジュールにおいて、出力電圧を比較する比較回路を2つに分け、パワーMOSFETが正常にOFFになっていることを判定する手段と、パワーMOSFETが正常にONになっていることを判定する手段とを独立に設け、更にそれぞれの判定信号を入力し故障を判定する故障判定回路を設けている。

【0005】

また、非特許文献1には、インテリジェントパワーデバイス(IPD)が開示されている。図25は、非特許文献1に開示されているIPDを組み込んだ回路例を示す図である。IPD101は、VCC端子103とGND(接地)端子との間に設置され、コントローラ102の出力端子108から出力される信号を入力端子106で受け、出力端子104に接続されている負荷109の制御を行なう。また、IPD101は自己診断の機能を有し、自己診断の結果をDIAG端子105を通してコントローラ102の入力端子107へ出力する。

【0006】

また、図26は非特許文献1に開示されているIPD101の詳細な回路図である。IPD101は、入力端子106で受けた信号をロジック113で処理し、パワーMOSFET110を制御する。パワーMOSFET110は、ドレインが電源端子(VCC)103と接続され、ソースが出力端子104と接続されている。出力端子104に接続された負荷109に流れる電流はパワーMOSFET110により制御される。また、IPDは、例えば過電流検出回路111、過熱検出回路112等の自己診断機能を有し、予め設定された判定値に達した場合には、パワーMOSFETをカットオフし、その情報を自己診断結果としてDIAG端子105を通してコントローラへフィードバックすることができる。以下で、過電流検出回路111、過熱検出回路112が働く場合の動作について説明する。

【0007】

まず、負荷ショートで過電流検出回路111が動作する場合について説明する。図27(a)は、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流の変化を示す図である。負荷ショートが発生するとパワーMOSFETへ電流定格を超えた過大な電流が流れ、パワーMOSFETは発熱により破壊される。通常、IPDには過大な電流が流れることを防ぐ電流制限回路が設けられている。この電流制限回路を用いることで、図27(b)に示すように過大な電流をある程度まで抑えることが可能である。しかし、この場合も時間と共に発熱しパワーMOSFETは破壊に至る。

【0008】

そこで、図26に示すIPDには、過電流検出回路111が設けられている。この過電流検出回路111は、図27(c)に示すように、パワーMOSFETに流れる電流が、あらかじめIPDに設定されている電流検出閾値を超えた場合、パワーMOSFETをカットオフする機能を有する。この機能によりパワーMOSFETの発熱による破壊を防止することが可能となる。

【0009】

図28は、過電流検出回路111の一例を示す図である。過電流検出回路111はコンパレータ116を含み、コンパレータ116の一方の入力には出力端子104の電位が供給され、他方の入力には電流検出閾値115が供給され、コンパレータ116の出力はロジック113へ入力される。ここで、パワーMOSFET110のオン抵抗を100mΩ、電流定格を2Aとした場合、電流検出閾値は、例えば0.5V(=100mΩ×5A)と設計される。この条件では、パワーMOSFETの出力電流が5Aを超えた場合に、ロジックによりドライバ114が制御され、パワーMOSFET110がカットオフされることになる。

【0010】

次に、負荷ショートで過熱検出回路112が動作する場合について説明する。図29(a)は、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流の変化、及びパワーMOSFETの温度の変化を示す図である。負荷ショートが発生するとパワーMOSFETへ電流定格を超えた電流が流れ、パワーMOSFETは発熱により破壊される。通常、IPDには過大な電流が流れることを防ぐ電流制限回路が設けられている。この電流制限回路を用いることで、図29(b)に示すように過大な電流をある程度まで抑えることが可能である。しかし、この場合も時間と共に発熱しパワーMOSFETは破壊に至る。

【0011】

そこで、図26に示すIPDには、過熱検出回路112が設けられている。この過熱検出回路112は、図29(c)に示すように、パワーMOSFETの温度が、あらかじめIPDに設定されている温度検出閾値を超えた場合、パワーMOSFETをカットオフする機能を有する。この機能によりパワーMOSFETの発熱による破壊を防止することが可能となる。

【0012】

図30は、過熱検出回路112の一例を示す図である。過熱検出回路112は、コンパレータ118を含み、コンパレータ118の一方の入力にはパワーMOSFETと熱的に結合されたダイオード119の電圧降下が供給され、他方の入力には温度検出閾値117が供給され、コンパレータ118の出力はロジック113に入力される。ダイオード119のカソードは定電流源120と接続されている。ここで、27℃のダイオードの電圧降下を0.7V、温度変化を−2mV/℃、温度定格を150℃とした場合、温度検出閾値は0.404V(=0.7V−2mV/℃ × (175℃ −27℃))と設計される。この条件では、パワーMOSFETの温度が175℃を超えた場合に、ロジック113によりドライバ114が制御され、パワーMOSFET110がカットオフされることになる。

【0013】

このように、図26に示したIPDでは、過電流検出回路111、過熱検出回路112がそれぞれ独立に動作をし、異常状態においてパワーMOSFETの破壊を防止することができる。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2007−174756号公報

【特許文献2】実用新案登録第2599788号公報

【非特許文献】

【0015】

【非特許文献1】"MOS集積回路(μPD166005)データ・シート(NECエレクトロニクス)"<URL:http://www.eu.necel.com/_pdf/S19284EJ1V0DS00.PDF>

【発明の概要】

【発明が解決しようとする課題】

【0016】

まず、パワーMOSFETおよびこれを搭載した半導体装置(IPD)の故障に関して説明する。図11はIPDの時間経過に伴う故障率の変化を示した図である。図11に示すように、IPDの故障には、時間順に初期故障領域、偶発故障領域、摩耗故障領域の3つに分けることができる。また、図12はIPDの時間経過に伴う特性値の変化を示した図である。図12に示すように、サージ等の異常状態を経験したIPDでは、異常状態を経験していないIPD(寿命を全うしたIPD)に比べて早く故障する可能性が高い。本発明では、図11における偶発故障領域における故障や、図12における特性が変化する直前(図中のA点、B点)における故障を未然に防ぐことが可能な半導体装置(IPD)を提供する。

【0017】

IPDの故障例としては、(1)パワーMOSFETのオン抵抗増加による故障、(2)パワーMOSFETのリーク電流増加による故障、(3)パワーMOSFETのゲートリーク電流増加による故障、(4)パワーMOSFETを有するIPDの消費電流変動による故障、の4つが挙げられる。以下で、各故障例について説明する。

【0018】

(1)パワーMOSFETのオン抵抗増加による故障

まず、パワーMOSFETのオン抵抗増加による故障について説明する。図13は、負荷ショート等により過大な電流がパワーMOSFETに流れた状態を示す図である。図13に示すように、過大な電流がパワーMOSFETへ流れることにより、パワーMOSFETの金属−半導体の境界でエレクトロマイグレーションが発生する。図14、図15、図16はパワーMOSFETで発生したエレクトロマイグレーションを説明するための図である。図14に示すように、パワーMOSFETに大電流が流れることで金属−半導体の境界においてエレクトロマイグレーションが発生し、パワーMOSFET自体の抵抗が増加する。

【0019】

図15に示すように、このエレクトロマイグレーションが更に成長すると、パワーMOSFETセルのベース領域の抵抗成分に影響を及ぼすようになる。この結果、図16に示すように、パワーMOSFETの寄生バイポーラトランジスタが動作し、特に、スイッチングにおけるターンオフで、パワーMOSFETを構成するセルの中で最も影響を受けたセルへ電流集中が発生する。この寄生バイポーラトランジスタによる電流集中により特定のセルが急に発熱し、パワーMOSFETが故障する。この事例は、パワーMOSFETのオン抵抗の変化は小さなものであるが、このオン抵抗の上昇が瞬時にパワーMOSFETを故障させる場合の事例である。

【0020】

(2)パワーMOSFETのリーク電流増加による故障

図17は、パワーMOSFETの製造ばらつきが原因で、ソース拡散領域(N+)の横広がりが大きくなった場合を示す図である。ソース拡散領域の横広がりが大きいパワーMOSFETでは、パワーMOSFETセルの実行チャネル長が短いため、図18に示すようにドレイン・ソース間電圧が大きくなると他のセルより多くの電流が流れる。そのため、ソレノイドなどのアクチュエータが負荷である場合、負荷の持つインダクタンス成分によりパワーMOSFETのスイッチングにおけるターンオフでパワーMOSFETのドレイン・ソース間電圧に高電圧が発生する。これにより、毎回のスイッチングでそのパワーMOSFETセルに想定以上の電流が流れる。

【0021】

このとき、図19に示すように、該当セルを走る電子がインパクトイオン化を起こし、プラス電荷がパワーMOSFETのゲート酸化膜に取り込まれる場合がある。ゲート酸化膜にプラス電荷が取り込まれると、該当セルにおいてリーク電流が生じ、さらに他のセルよりも多くの電流が流れる(フィードフォワードの現象)。最終的には、該当セルでまかないきれない電流が集中することで、セル自体が急に発熱し故障に至る。この事例は、パワーMOSFETの総リーク電流としては小さな値であるが、電流が特定セルに集中することにより瞬時にパワーMOSFETが故障する場合の事例である。

【0022】

(3)パワーMOSFETのゲートリーク電流増加による故障

次に、パワーMOSFETにサージ電圧が印加され、パワーMOSFETのゲート酸化膜にリーク箇所が生じた場合を考える。図20は、サージ電圧印加によりゲート・ソース間にリーク箇所が生じた場合を示す図である。パワーMOSFETは、図21に示すように、セルと呼ばれる単位構成が複数並列接続されている。このうち、サージ電圧印加により1つのセルのゲート・ソース間にリーク箇所が生じても、リークの値が小さい場合、すなわち、ドライバの電流供給能力がリーク電流に対して大きい場合、パワーMOSFETの動作に影響を与えない。

【0023】

しかし、ゲート・ソース間に電圧が印加され続けると(パワーMOSFETのオン状態)、リーク箇所の電流量が突如増し、不可逆的な遷移を見せることがある。この不可逆的な遷移が生じるとパワーMOSFETの動作に影響を及ぼし、ゲート・ソース電圧を印加してもパワーMOSFETがオン状態とならない、いわゆるオフ故障を起こす。

【0024】

次に、リーク箇所がゲート・ドレイン間である場合について説明する。図22は、サージ電圧印加によりゲート・ドレイン間にリーク箇所が生じた場合を示す図である。上記と同様に、パワーMOSFETは、図23に示すように、セルと呼ばれる単位構成が複数並列接続されている。このうち、サージ電圧印加により1つのセルのゲート・ドレイン間にリーク箇所が生じても、リークの値が小さい場合、すなわち、ドライバの電流供給能力がリーク電流に対して大きい場合、パワーMOSFETの動作に影響を与えない。

【0025】

しかし、ゲート・ドレイン間に電圧が印加され続けると(パワーMOSFETのオン状態)、リーク箇所の電流量が突如増し、不可逆的な遷移を見せることがある。この不可逆的な遷移が生じるとパワーMOSFETの動作に影響を及ぼし、パワーMOSFETがオフ状態とならない、いわゆるオン故障を起こす。

【0026】

この事例は、いずれの場合もパワーMOSFETのゲートリーク電流としては小さな値であるが、電流が突如増すことにより、パワーMOSFETを制御することができなくなる故障の事例である。

【0027】

(4)IPDの消費電流変動による故障

次に、図24(a)に示すように、IPDの制御回路の配線パターン間(配線1と配線2の間)に配線パターンの残りがある場合を考える。IPDの製造段階の検査において、配線1と配線2が電気的にオープン状態となっておりその検査をパスしたとする。しかし、その後のIPD稼動時において、例えば環境温度の変化により、配線パターン残りが伸縮し配線1と配線2が抵抗成分を持ちながら電気的にショート状態となると、配線1と配線2との間に電流が流れる。図24(b)はこの状態を示す回路図である。

【0028】

この場合、配線パターン残りの抵抗が大きいため、IPDの総消費電流の変動は小さく、またIPDの動作に影響を及ぼすものでもない。しかしながら、IPDが更に稼動されると、配線パターン残りの抵抗が小さくなり、突如としてIPDに影響を及ぼす。この影響により、IPDは制御不能となり故障と判断される。この事例は、IPDの総消費電流の増減としては小さな値であるが、配線パターン残りの抵抗成分の変動により突如として故障にいたる場合を示す事例である。

【0029】

以上、4つの故障例で示したとおり、IPDの故障へ至るまでには、パワーMOSFETのオン抵抗、リーク電流(ゲートリーク、オフリーク)、IPDの消費電流の小さな変化があり、その後これらの値が急峻に変化し、故障が生じる。つまり、偶発故障領域の故障を未然に防ぐ、あるいはサージ等の異常状態を経験したIPDのその後の劣化進行による故障を防ぐためには、前述のパワーMOSFETのオン抵抗、リーク電流、IPDの消費電流の小さな変化をモニターすることが必要となる。

【0030】

また、前述の通り、図25、図26で説明したIPDは、異常状態からパワーMOSFETを保護するために、過電流検出回路、過熱検出回路を備えている。しかしながら、IPDが突然状態遷移を起こし、IPDの機能が損なわれる場合には、過電流検出回路、過熱検出回路で充分にIPDを保護できるわけではない。

【0031】

例えば、異常状態として負荷がショートした場合を考える。前述の通り、負荷のショートにより、たとえ電流制限によりパワーMOSFETへ流れる電流が制限されたとしても、一時的にはパワーMOSFETへは定格を超えた大電流が流れる。この大電流により、パワーMOSFETを構成するセルのうち電流密度の高い一部のセルにエレクトロマイグレーションが発生する。そして、IPDが稼動している間エレクトロマイグレーションが進行し、IPDの特性としては出力オン抵抗が若干高くなる。

【0032】

例えば、IPDのパワーMOSFETを構成するセルが15000セルあり、その中の1000セルがエレクトロマイグレーションにより抵抗値が高くなるとする。この場合、オープン状態、すなわち抵抗値が無限大となると、IPDのパワーMOSFETのオン抵抗は15000/14000倍となる。つまり、製造初期のオン抵抗が100mΩである場合、エレクトロマイグレーションによるオン抵抗は107.143mΩとなる。

【0033】

この場合、IPDのその後の稼動が定格以内、例えば出力電流が2A以内であれば、パワーMOSFETの電圧降下は最大214.286mVととなり、前述の過電流検出回路は当然ながら働かない(過電流検出の閾値を500mVとした場合)。また過熱検出回路も通常動作において温度定格(例えば150℃)に充分なマージンをとり、例えば100℃以下となるように、IPDの使用条件を設定しているため、過熱検出回路も働かない(過熱検出の閾値を175℃とした場合)。

【0034】

しかしながら、上述したIPDの故障例の「(1)パワーMOSFETのオン抵抗増加による故障」で説明したとおり、パワーMOSFETのセルにおけるエレクトロマイグレーションは通常動作のスイッチング、特にターンオフで寄生バイポーラトランジスタが動作する。この寄生バイポーラトランジスタによる電流集中により特定のセルが急に発熱し、パワーMOSFETが故障する。このように、パワーMOSFETは突然の状態遷移により突如破壊に至る場合もある。よって、背景技術で説明したIPDが備える過電流検出回路や過熱検出回路では突然の状態遷移に対しては対応できないため、IPDが故障する場合があるという問題があった。

【課題を解決するための手段】

【0035】

本発明にかかる半導体装置は、半導体装置の初期特性値に基づき定められた設定値を記憶する設定値記憶部と、所定のタイミングにおける前記半導体装置の特性値と前記設定値記憶部に記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する検出回路と、を備える。

【0036】

本発明にかかる半導体装置では、半導体装置の初期特性値に基づき定められた設定値と所定のタイミングにおける前記半導体装置の特性値とに基づき、半導体装置の故障に繋がるような特性劣化を検出することができるので、半導体装置の故障を未然に防ぐことができる。

【0037】

本発明にかかる半導体装置の特性劣化検出方法は、前記半導体装置の初期特性値に基づき定められた設定値を記憶し、所定のタイミングにおける前記半導体装置の特性値と前記記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する。

【0038】

本発明にかかる半導体装置の特性劣化検出方法では、半導体装置の初期特性値に基づき定められた設定値と所定のタイミングにおける前記半導体装置の特性値とに基づき、半導体装置の故障に繋がるような特性劣化を検出することができるので、半導体装置の故障を未然に防ぐことができる。

【発明の効果】

【0039】

本発明により半導体装置の故障に繋がるような特性劣化を検出することができる半導体装置、及び半導体装置の特性劣化検出方法を提供することができる。

【図面の簡単な説明】

【0040】

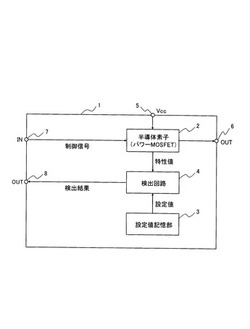

【図1】実施の形態1にかかる半導体装置(IPD)を示すブロック図である。

【図2】実施の形態1にかかる半導体装置(IPD)の詳細を説明するためのブロック図である。

【図3】実施の形態1にかかる半導体装置(IPD)のオン抵抗検出回路の一例を示す回路図である。

【図4】実施の形態1にかかる半導体装置(IPD)のゲートリーク検出回路の一例を示す回路図である。

【図5】実施の形態1にかかる半導体装置(IPD)のオフリーク検出回路の一例を示す回路図である。

【図6】実施の形態1にかかる半導体装置(IPD)の消費電流検出回路の一例を示す回路図である。

【図7】実施の形態1にかかる半導体装置(IPD)の設定値記憶部の一例を示す回路図である。

【図8】実施の形態1にかかる半導体装置(IPD)の製造から異常検出までのフローを説明するためのフローチャートである。

【図9】実施の形態2にかかる半導体装置(IPD)を示すブロック図である。

【図10】実施の形態2にかかる半導体装置(IPD)の製造から異常検出までのフローを説明するためのフローチャートである。

【図11】IPDの時間経過に伴う故障率の変化を示す図である。

【図12】IPDの時間経過に伴う特性値の変化を示す図である。

【図13】負荷ショートによりパワーMOSFETに過大な電流が流れた場合を示す図である。

【図14】パワーMOSFETにエレクトロマイグレーションが発生した状態を示す部分断面図である。

【図15】パワーMOSFETにエレクトロマイグレーションが発生した状態を示す部分断面図である。

【図16】パワーMOSFETに寄生バイポーラトランジスタが発生した状態を示す部分断面図である。

【図17】パワーMOSFETのソース拡散領域の横広がりが大きい場合を示す部分断面図である。

【図18】パワーMOSFETのソース拡散領域の横広がりが大きい場合のドレイン・ソース間電圧と電流値との関係を示す図である。

【図19】パワーMOSFETのゲート酸化膜にプラス電荷が取り込まれた場合を示す部分断面図である。

【図20】サージ電圧印可によりパワーMOSFETのゲート・ソース間にリーク箇所が生じた場合を示す部分断面図である。

【図21】パワーMOSFETのゲート・ソース間にリーク箇所が生じた場合の等価回路図である。

【図22】サージ電圧印可によりパワーMOSFETのゲート・ドレイン間にリーク箇所が生じた場合を示す部分断面図である。

【図23】パワーMOSFETのゲート・ドレイン間にリーク箇所が生じた場合の等価回路図である。

【図24】(a)IPDの制御回路の配線パターン間(配線1と配線2の間)に配線パターンの残りがある場合を示す部分平面図である。(b)配線パターン間(配線1と配線2の間)がショートした場合の回路図である。

【図25】背景技術にかかるインテリジェントパワーデバイス(IPD)を組み込んだ回路例を示すブロック図である。

【図26】背景技術にかかるIPDのブロック図である。

【図27】背景技術にかかるIPDにおいて、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流の変化を示す図である。(a)は電流制限回路、過電流検出回路を有しない場合。(b)は電流制限回路を有する場合。(c)は電流制限回路および過電流検出回路を有する場合。

【図28】過電流検出回路の一例を示す回路図である。

【図29】背景技術にかかるIPDにおいて、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流と温度の変化を示す図である。(a)は電流制限回路、過熱検出回路を有しない場合。(b)は電流制限回路を有する場合。(c)は電流制限回路および過熱検出回路を有する場合。

【図30】過熱検出回路の一例を示す回路図である。

【発明を実施するための形態】

【0041】

実施の形態1

以下、図面を参照して本発明の実施の形態1について説明する。図1は、本実施の形態にかかるIPD(半導体装置)1を示すブロック図である。本実施の形態にかかるIPD1は、半導体製造工程により製造され、半導体チップ(またはウェハ)が完成した状態のIPD1の初期特性値に基づき定められた設定値を記憶する設定値記憶部3と、IPD1がECU(エンジンコントロールユニット)等のシステムに設置された状態での所定のタイミングにおけるIPD1の特性値と、設定値記憶部3に記憶された設定値とに基づき、IPD1の特性劣化を検出する検出回路4と、を備える。

【0042】

本実施の形態にかかるIPD1が備えるパワー半導体素子は、例えばパワーMOSFET2である。パワーMOSFET2は、例えばN型のパワーMOSFETであり、ドレインが電源端子(Vcc)5と接続され、ソースが出力端子(OUT)6と接続され、ゲートが入力端子(IN)と接続されている。パワーMOSFET2のゲートには制御信号が供給される。なお、本実施の形態にかかる半導体装置1では、パワーMOSFET2と入力端子7との間にドライバ回路を設けてもよい。また、出力端子6には負荷が接続される。なお、パワー半導体素子は、パワーMOSFETに限らず、IGBT(Insulated Gate Bipolar Transistor)でも良い。

【0043】

本実施の形態にかかるIPD1において検出回路4とは、例えばパワーMOSFET2のオン抵抗の特性劣化を検出するための回路、パワーMOSFET2のゲートリークの特性劣化を検出するための回路、パワーMOSFET2のオフリークの特性劣化を検出するための回路、IPD1に流れる消費電流の特性劣化(電圧降下)を検出するための回路である。なお、本実施の形態ではこれら以外にも、IPDの特性劣化を検出するために用いることができる特性値であればどのようなものを用いてもよい。

【0044】

また、本実施の形態にかかるIPD1では、検出回路4から検出結果が出力され、この検出結果は出力端子8から出力される。つまり、出力端子8からは、検出回路4が異常を検出した場合には異常を知らせる信号が出力され、検出回路4が異常を検出しない場合は正常を知らせる信号が出力される。IPD1を制御するコントローラ(図2のマイクロコンピュータ10)は、出力端子8から異常を知らせる信号が出力されると、例えば、IPD1を交換する必要があることを知らせるメッセージを表示したり、IPD1の制御パラメータを変更したり、IPD1の動作を停止する。

【0045】

また、検出回路4がIPD1の特性劣化を検出する際に用いる、所定のタイミングにおけるIPD1の特性値とは、例えばIPD1の電源投入時における特性値、IPD1の入力端子7に制御信号が入力されたタイミングにおける特性値、コントローラからIPD1へIPD1の特性劣化を検出する旨の命令信号が入力されたタイミングにおける特性値、IPD1の稼働中における一定周期毎における特性値などである。なお、IPD1の特性値を取得する所定のタイミングは、これら以外にも任意に設定することができる。

【0046】

次に、本実施の形態にかかるIPD(半導体装置)の詳細な構成について図2を用いて説明する。図2は本実施の形態にかかるIPD1の詳細な構成を示すブロック図である。本実施の形態にかかるIPD1は、パワーMOSFET2、ドライバ回路12、電流制限回路13、オープン検出回路14、電流検出回路15、温度検出回路16、DIAG出力端子9を備える。

【0047】

パワーMOSFET2のドレインは電源端子(Vcc)5と接続され、ゲートはドライバ12と接続され、ソースは出力端子(OUT)6と接続されている。また、パワーMOSFET2のゲート・ソース間には、電流制限回路13が接続されている。出力端子(OUT)6には負荷RLが接続されており、パワーMOSFET2は負荷RLに対して電流を供給する。また、ドライバ回路12はパワーMOSFET2を駆動するための回路である。

【0048】

電流制限回路13は、異常状態、例えば出力端子6と負荷のGND端子が短絡された負荷ショートにより、パワーMOSFET2に過大電流が流れることでパワーMOSFET2が劣化・破壊することを防止するために出力電流を制限する回路である。電流制限回路13を内蔵していない場合は、例えば100A以上の過大電流がパワーMOSFET2に流れる。しかし、電流制限回路13を設けることで、パワーMOSFET2に流れる電流を15A程度に制限することができる。

【0049】

オープン検出回路14は、出力端子(OUT)6のオープン状態を検出するための回路である。つまり、オープン検出回路14は、本来、出力端子6に接続されているべき負荷RLが接続されていないことを検出する回路である。

【0050】

電流検出回路15は、パワーMOSFET2に定格電流以上の電流が流れているかを検出する回路である。例えば、パワーMOSFET2の定格電流が2Aの場合、何らかの異常(例えば、前述の負荷ショート)によりパワーMOSFET2に15Aの電流が流れた場合に電流検出される。

【0051】

温度検出回路16は、異常状態(例えば、前述の負荷ショート)により、パワーMOSFET2の温度が予め設定された温度(例えば175℃)を超えた場合に異常を検出する回路である。

【0052】

オープン検出回路14、電流検出回路15、温度検出回路16の各出力はAND回路17に入力される。そして、オープン検出回路14、電流検出回路15、温度検出回路16の各出力のすべてがHレベル(Highレベル、正常)である場合、AND回路17はHレベルの信号をインバータ18とAND回路11に出力する。インバータ18はAND回路17からのHレベル信号をLレベル(Lowレベル)信号に反転し、Lレベル信号をN型MOSトランジスタMN1のゲートに供給する。この場合、MN1のゲートはLレベルであるため、DIAG出力端子9からは正常を示すHレベル信号が出力される。

【0053】

一方、オープン検出回路14、電流検出回路15、温度検出回路16の各出力のうちいずれかがLレベル(異常)である場合、AND回路17はLレベルの信号をインバータ18に出力する。インバータ18はAND回路17からのLレベル信号をHレベル信号に反転し、Hレベル信号をN型MOSトランジスタMN1のゲートに供給する。MN1のゲートはHレベルであるため、DIAG出力端子9からは異常を示すLレベル信号が出力される。

【0054】

つまり、DIAG出力端子9からは、オープン検出回路14が出力端子(OUT)6に負荷が接続されていない状態を検出した場合、電流検出回路15が過大な電流が流れている状態を検出した場合、温度検出回路16が過大な温度となっている状態を検出した場合、のいずれか1つ以上の場合に、コントローラ(マイクロコンピュータ)10へ異常を通知する信号が出力される。

【0055】

また、IPD1を制御するコントローラ(マイクロコンピュータ)10は、IPD1の入力端子(IN)7にIPD1をオン/オフする制御信号を出力する。この制御信号は、IPD1のAND回路11に入力される。また、AND回路11には、AND回路17からの出力も入力される。よって、AND回路11は、マイクロコンピュータ10からの信号がHレベルで、かつAND回路17からの信号がHレベルである場合に、Hレベル信号をドライバ回路12へ出力する。一方、AND回路11は、マイクロコンピュータ10からの信号とAND回路17からの信号の少なくとも1つがLレベルである場合に、Lレベル信号をドライバ回路12へ出力する。ドライバ回路12は、AND回路11がHレベル信号を出力した場合はパワーMOSFET2を駆動し、AND回路11がLレベル信号を出力した場合はパワーMOSFET2を駆動しない。すなわち、オープン検出回路14、電流検出回路15、温度検出回路16のいずれかが異常を示している場合は、ドライバ回路12はパワーMOSFET2を駆動しないように制御する。

【0056】

また、図2に示すように本実施の形態にかかるIPD1は、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50を備える。オン抵抗検出回路20の中には、図1に示した設定値記憶部3に対応する回路と検出回路4に対応する回路がそれぞれ設けられている。ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50についても同様である。また、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50には、IPD1に電源が投入されたことを通知するための電源投入信号が入力される。

【0057】

オン抵抗検出回路20は、パワーMOSFET2のオン抵抗の初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおけるオン抵抗の特性値がオン抵抗の初期特性値に基づき定められた設定値の1.1倍以上になった場合に、オン抵抗検出回路20が異常を検出するものとする。

【0058】

ゲートリーク検出回路30は、オフ状態、又はオン状態において、パワーMOSFET2のゲートリークの初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおけるゲートリークの特性値が、ゲートリークの初期特性値(製造時の特性値)に基づき定められた設定値である1μA以上となった場合に、ゲートリーク検出回路30が異常を検出するものとする。ここで、初期特性値に基づき定められた設定値とは、ゲートリークの初期特性値(例えば、0μA)に対して任意の値(例えば、1μA)を加えた値を設定値(=0μA+1μA)とすることである。

【0059】

オフリーク検出回路40は、パワーMOSFET2のオフリークの初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるパワーMOSFET2のオフリークの特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおけるオフリークの特性値が、オフリークの初期特性値(製造時の特性値)に基づき定められた設定値である1μA以上となった場合に、オフリーク検出回路40が異常を検出するものとする。ここで、初期特性値に基づき定められた設定値とは、オフリークの初期特性値(例えば、0μA)に対して任意の値(例えば、1μA)を加えた値を設定値(=0μA+1μA)とすることである。

【0060】

消費電流検出回路50は、IPD1の内部GND配線(内部基準配線)55に流れる消費電流Icの初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるIPD1の消費電流の特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおける消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.1倍以上になった場合に、消費電流検出回路50が異常を検出するものとする。

【0061】

オン抵抗検出回路20の出力21、ゲートリーク検出回路30の出力31、オフリーク検出回路40の出力41、消費電流検出回路50の出力51はそれぞれ、NAND回路19に入力される。本実施の形態では、例えば各出力21、31、41、51がHレベルの時は正常であり、Lレベルの時は異常であるとしている。NAND回路19の出力はN型MOSトランジスタMN2のゲートに接続されており、NAND回路19がLレベルの信号を出力する場合は、出力端子(Warning)8から正常を示すHレベルの信号が出力される。一方、NAND回路19がHレベルの信号を出力する場合は、出力端子(Warning)8から異常を示すLレベルの信号が出力される。

【0062】

すなわち、次の(1)から(4)の少なくとも1つ以上の条件が満たされた場合は、出力端子(Warning)8から異常を示すLレベル信号が出力され、次の(1)から(4)のいずれの条件も満たさない場合は、出力端子(Warning)8から正常を示すHレベル信号が出力される。

(1)所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値が、パワーMOSFET2のオン抵抗の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

(2)所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、設定値である1μA以上となった場合。

(3)所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、設定値である1μA以上となった場合。

(4)所定のタイミングにおけるIPD1の消費電流の特性値が、IPD1の消費電流の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

【0063】

マイクロコンピュータ10は、出力端子(Warning)8からの信号を入力することで、IPD1の経時劣化の状態等を判断することができる。また、マイクロコンピュータ10は、異常を示す信号を入力した場合は、例えば、IPD1を交換する必要があることを知らせるメッセージを表示したり、IPD1の制御パラメータを変更したり、IPD1の動作を停止することができる。

【0064】

また、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50がIPD1の特性劣化を検出する際に用いる、所定のタイミングにおけるIPD1の特性値とは、例えばIPD1の電源投入時における特性値、IPD1の入力端子7に制御信号が入力されたタイミングにおける特性値、コントローラからIPD1へIPD1の特性劣化を検出する旨の命令信号が入力されたタイミングにおける特性値、IPD1の稼働中における一定周期毎における特性値などである。なお、IPD1の特性値を取得する所定のタイミングは、これら以外にも任意に設定することができる。

【0065】

次に、本実施の形態にかかるIPD1のオン抵抗検出回路20の具体的な回路構成の一例について説明する。図3は、本実施の形態にかかるIPD1のオン抵抗検出回路20の一例を示す回路図である。オン抵抗検出回路20は、抵抗(第1の抵抗)Rs、抵抗(第2の抵抗)Rf、可変抵抗(第1の可変抵抗)Ra1、コンパレータ(第1のコンパレータ)25を有する。

【0066】

抵抗Rsは、一方がパワーMOSFET2のソース側のノード(第1のノード)24に接続され、他方がノード(第2のノード)26と接続されている。可変抵抗Ra1は、一方がパワーMOSFET2のドレイン側のノード22と接続され、他方がノード(第3のノード)23と接続されている。抵抗Rfは、一方がノード23と接続され、他方がノード26と接続されている。また、コンパレータ25は、入力がノード23、ノード24と接続され、出力21が図2のNANDの入力に接続されている。

【0067】

図3に示すオン抵抗検出回路20において、パワーMOSFET2をオンさせると、パワーMOSFET2のソースから電流Ioutが流れる。このとき、電源端子(Vcc)5とノード26(出力端子(OUT)6)との間の電圧Vcc−Voutと、パワーMOSFET2のドレイン・ソース間電圧Vdsを測定すると、次の関係が成り立つ。

【0068】

Vds/(Vcc−Vout)=Ron×Iout/(Ron×Iout+Rs×Iout)=Ron/(Ron+Rs)・・・式1

【0069】

式1において、RonはパワーMOSFET2のオン抵抗の初期特性値に基づき定められた設定値である。よって、パワーMOSFET2のオン抵抗が、オン抵抗の初期特性値に基づき定められた設定値の1.1倍となるようなRa1を、次の関係式を用いて求めることができる。

【0070】

Ron×1.1/(Ron×1.1+Rs)=Ra1/(Ra1+Rf)・・・式2

【0071】

例えば、オン抵抗の設定値をRon=100mΩ、Rs=10mΩ、Rf=10kΩとすると、式2を用いて、Ra1=110kΩとなる。よって、この値の抵抗値をオン抵抗検出回路20の設定値とする。

【0072】

このとき、図3に示すオン抵抗検出回路20のノード23には、電源端子(Vcc)5と出力端子(OUT)6との間の電圧Vcc−Voutを、抵抗Ra1と抵抗Rfの抵抗値に基づき分割された電圧値であるVrefが発生する(Vrefは設定値なので不変)。また、オン抵抗検出回路20のノード24には、電源端子(Vcc)5と出力端子(OUT)6との間の電圧Vcc−Voutを、パワーMOSFET2のオン抵抗Ronと抵抗Rsの値に基づき分割された電圧値であるVmが発生する。

【0073】

ここで、初期状態では、Ra1=110kΩ、Rf=10kΩであり、また、Ron=100mΩ、Rs=10mΩであるため、ノード23の電圧Vrefは、ノード24の電圧Vmよりも小さい。コンパレータ25は、ノード23の電圧Vrefとノード24の電圧Vmを比較し、Vref<Vmの場合は正常を示す信号(Hレベル)を出力する。

【0074】

一方、パワーMOSFET2の特性劣化により、オン抵抗Ronの値が大きくなるにつれて、ノード24の電圧Vmも次第に小さくなる。よって、コンパレータ25は、ノード23の電圧Vrefとノード24の電圧Vmとを比較し、Vref≧Vmの場合は異常を示す信号(Lレベル)を出力する。つまり、パワーMOSFET2のオン抵抗がRon×1.1(すなわち、110mΩ)以上になった場合、ノード23の電圧Vrefとノード24の電圧VmはVref≧Vmとなるため、この大小関係をコンパレータ25を用いて比較することで、パワーMOSFET2のオン抵抗の異常を検出することができる。

【0075】

なお、図3に示したオン抵抗検出回路は一例であり、パワーMOSFET2のオン抵抗を検出することができる回路であれば、どのような回路を用いてもよい。

【0076】

また、Ra1の値をオン抵抗検出回路20の設定値とする場合は、例えば図7に示す回路(設定値記憶部)を用いることができる。図7に示す回路は、ノード60とノード61との間に直列に接続された複数の抵抗を備える。図7に示す抵抗の値は一例であり、任意に変更可能である。また、ノード60は図3のオン抵抗検出回路20のノード22に対応し、ノード61は図3のオン抵抗検出回路20のノード23に対応している。直列に接続された複数の抵抗の各々の両端には、それぞれP型MOSトランジスタMP10〜MP16のソース・ドレインが接続されている。また、P型MOSトランジスタMP10〜MP16のゲートには、それぞれ定電流源62−1〜62−7が接続されている。定電流源62−1〜62−7と基準電源との間には、P型MOSトランジスタMP10〜MP16に対応した位置にトリミング抵抗63−1〜63−7が設けられている。ここで、基準電源はP型MOSトランジスタMP10〜MP16をオンさせることのできる電位であればよく、例えばIPD1の内部GND配線(内部基準配線)に接続されている。

【0077】

例えば、本実施の形態で説明したようにRa1=110kΩに設定する場合は、64kΩ+32kΩ+8kΩ+4kΩ+2kΩの抵抗を選択する(図7の場合は、64kΩは必ず選択される)。つまり、トリミング抵抗63−2、63−3、63−5、63−7を、レーザを照射して切断することで、P型MOSトランジスタMP11、MP12、MP14、MP16がオフする。よって、2kΩ、4kΩ、8kΩ、32kΩの抵抗が選択されるため、ノード60とノード61との間の抵抗値は110kΩとなる。

【0078】

図7に示す回路では、64kΩ〜132kΩまで、1kΩ単位でRa1を設定することができる。よって、パワーMOSFET2のオン抵抗Ronが個体に80mΩ〜120mΩでばらついたとしても、オン抵抗Ronの1.1倍の検出点を設定することができる。つまり、Ra1を88kΩ〜132kΩの範囲で設定すればよい。なお、図7に示したRa1を設定する回路は一例であり、Ra1を設定することができる回路であればどのような回路を用いてもよい。

【0079】

次に、本実施の形態にかかるIPD1のゲートリーク検出回路30の具体的な回路構成の一例について説明する。図4は、本実施の形態にかかるIPD1のゲートリーク検出回路30の一例を示す回路図である。ゲートリーク検出回路30は、抵抗(第3の抵抗)Rg、可変抵抗(第2の可変抵抗)Ra2、抵抗(第5の抵抗)Rd、定電圧源(第1の定電圧源)Vini、オペアンプ(第1のオペアンプ)32、コンパレータ(第2のコンパレータ)33を有する。

【0080】

抵抗Rgは、パワーMOSFET2のゲートに接続されており、一方がオペアンプ32の一方の入力に接続され、他方がオペアンプ32の他方の入力に接続される。可変抵抗Ra2は、一方がパワーMOSFET2のドレイン側のノード35に接続され、他方がノード34と接続されている。抵抗Rdは、一方がノード34と接続され、他方が定電圧源Viniの一方と接続されている。また、定電圧源Viniの他方はノード35と接続されている。オペアンプ32の入力は抵抗Rgの両端に接続され、出力はコンパレータ33の一方の入力に接続されている。コンパレータ33の入力の他方はノード34と接続されており、出力31は図2のNANDの入力に接続されている。

【0081】

ノード34には、定電圧源Viniの電圧値と可変抵抗Ra2の抵抗値と抵抗Rdの抵抗値とに基づき決定された電圧が発生する。ノード34の電圧値は、基準電圧Vrefとしてコンパレータ33に入力される。この基準電圧Vrefは、可変抵抗Ra2の値を変更することで任意に変更することができる。

【0082】

また、パワーMOSFET2にゲートリークがない場合、抵抗Rgにはゲートリーク電流Igが流れない。この場合は、抵抗Rgの両端、つまりオペアンプ32の入力には電位差が生じない。しかし、パワーMOSFET2にゲートリークがある場合、抵抗Rgにはゲートリーク電流Igが流れるため、抵抗Rgの両端、つまりオペアンプ32の入力には電位差が生じる。オペアンプ32は、抵抗Rgの両端の電位差に基づいて信号を出力する。つまり、ゲートリーク電流Igが大きくなるほど、抵抗Rgの両端の電位差が大きくなり、オペアンプ32の出力電圧は大きくなる。オペアンプ32の出力電圧はコンパレータ33の入力の一方に入力され、可変抵抗Ra2により設定された基準電圧Vrefと比較される。コンパレータ33は、オペアンプ32の出力電圧が基準電圧Vrefよりも小さい場合は、正常を示すHレベル信号を出力し、オペアンプ32の出力電圧が基準電圧Vref以上である場合は、異常を示すLレベル信号を出力する。

【0083】

例えば、ゲートリーク検出回路30を用いてゲートリーク電流Igが1μA以上となった場合を検出する際は、次のように可変抵抗Ra2の抵抗値を設定する。まず、ゲートリーク電流Igが1μA流れた時に抵抗Rgの両端に生じる電位差を求める。次に、この電位差がオペアンプ32に入力された際にオペアンプ32が出力する電圧値を求める。次に、この電圧値と基準電圧Vrefとが等しくなるように、可変抵抗Ra2の抵抗値を決定する。このように可変抵抗Ra2の抵抗値を設定することで、ゲートリーク電流Igが1μAよりも小さい場合は、コンパレータ33は正常を示すHレベル信号を出力し、ゲートリーク電流Igが1μA以上の場合は、コンパレータ33は異常を示すLレベル信号を出力するように、設定することができる。

【0084】

なお、ゲートリーク検出回路30においても可変抵抗Ra2の設定には、図7に示す回路を用いることができる。また、図4に示したゲートリーク検出回路は一例であり、パワーMOSFET2のゲートリークを検出することができる回路であれば、どのような回路を用いてもよい。

【0085】

次に、本実施の形態にかかるIPD1のオフリーク検出回路40の具体的な回路構成の一例について説明する。図5は、本実施の形態にかかるIPD1のオフリーク検出回路40の一例を示す回路図である。オフリーク検出回路40は、抵抗(第6の抵抗)Rs、可変抵抗(第3の可変抵抗)Ra3、定電圧源(第2の定電圧源)Vini、N型MOSトランジスタMN3〜MN5、P型MOSトランジスタMP1、MP2、オペアンプ(第3のオペアンプ)43を有する。

【0086】

抵抗Rsは、パワーMOSFET2のソースに接続されている。また、抵抗Rsの両端は、それぞれオペアンプ43の入力に接続されている。オペアンプ43の出力はN型MOSトランジスタ(第1のトランジスタ)MN3のゲートに接続されている。N型MOSトランジスタMN3のドレインはパワーMOSFET2のソースに、ソースはノード(第4のノード)44に接続されている。ノード44は、N型MOSトランジスタMN5のドレイン及びゲートに接続されている。N型MOSトランジスタMN5のソースはN型MOSトランジスタMN4のソースに、ゲートはN型MOSトランジスタMN4のゲートに接続されている。N型MOSトランジスタMN4のドレインはノード(第5のノード)42に接続されている。ここで、N型MOSトランジスタMN4、MN5はカレントミラー回路(第1のカレントミラー回路)を構成する。

【0087】

また、P型MOSトランジスタMP1のソースはP型MOSトランジスタMP2のソース、電源端子(Vcc)5、及び定電圧源(第2の定電圧源)Viniの一方と接続されている。また、P型MOSトランジスタMP1のゲート及びドレインは、P型MOSトランジスタMP2のゲート及び可変抵抗(第3の可変抵抗)Ra3の一方と接続されている。可変抵抗Ra3の他方は、定電圧源Viniの他方と接続されている。また、P型MOSトランジスタMP2のドレインはノード42に接続されている。ここで、P型MOSトランジスタMP1、MP2はカレントミラー回路(第2のカレントミラー回路)を構成する。また、ノード42の出力41は、図2のNANDの入力に接続されている。

【0088】

ノード42には、定電圧源Viniの電圧値と可変抵抗Ra3の抵抗値とに基づき決定された電流Iaが流れる。また、オフリーク電流Ioffが流れていない場合は、抵抗Rsの両端には電位差が生じないため、オペアンプ43の出力はLレベル信号となり、N型MOSトランジスタMN3はオンしない。この場合は、ノード44には電流が流れないため、N型MOSトランジスタMN4にも電流が流れない。よって、ノード42に流れる電流はIaのままとなる。この場合は、ノード42がHレベルとなり、オフリーク検出回路40は正常を示すHレベル信号を出力する。

【0089】

一方、抵抗Rsにオフリーク電流Ioffが流れると、抵抗Rsの両端に電位差が生じる。オペアンプ43の入力にはこの電位差が入力されるため、オペアンプ43はこの電位差に応じた信号(Hレベル信号)をN型MOSトランジスタMN3のゲートに出力する。N型MOSトランジスタMN3のゲートにHレベル信号が入力されると、ノード44には電流Ibが流れる。この電流Ibの値は、オフリーク電流Ioffの大きさに応じて変化する。ノード44に電流Ibが流れると、N型MOSトランジスタMN4にも電流Ibが流れる。このため、ノード42を流れる電流は、Ia−Ibとなる。よって、オフリーク電流Ioffの大きさが大きくなるにつれてIbも大きくなるので、ノード42に流れる電流Ia−Ibは次第に小さくなる。そして、最終的にはノード42はLレベルとなり、オフリーク検出回路40は異常を示すLレベル信号を出力する。

【0090】

例えば、オフリーク検出回路40を用いてオフリーク電流Ioffが1μA以上となった場合を検出する際は、次のように可変抵抗Ra3の抵抗値を設定する。まず、オフリーク電流Ioffが1μA流れた時に抵抗Rgの両端に生じる電位差を求める。次に、この電位差がオペアンプ43に入力された際にオペアンプ43が出力する電圧値を求める。次に、この電圧値がN型MOSトランジスタMN3のゲートに印加された場合にノード44に流れる電流Ibを求める。そして、この電流IbがN型MOSトランジスタMN4に流れた場合に、出力41がLレベル信号を出力するような電流Iaの値を決定する。そして、電流IbがN型MOSトランジスタMN4に流れていない状態で、この電流Iaがノード42に流れるように可変抵抗Ra3の抵抗値を決定する。このように可変抵抗Ra3の抵抗値を設定することで、オフリーク電流Ioffが1μAよりも小さい場合は、出力41は正常を示すHレベル信号を出力し、オフリーク電流Ioffが1μA以上の場合は、出力41は異常を示すLレベル信号を出力するように、設定することができる。

【0091】

なお、オフリーク検出回路40においても可変抵抗Ra3の設定には、図7に示す回路を用いることができる。また、図5に示したオフリーク検出回路は一例であり、パワーMOSFET2のオフリークを検出することができる回路であれば、どのような回路を用いてもよい。

【0092】

次に、本実施の形態にかかるIPD1の消費電流検出回路50の具体的な回路構成の一例について説明する。図6は、本実施の形態にかかるIPD1の消費電流検出回路50の一例を示す回路図である。消費電流検出回路50は、抵抗(第4の抵抗)Rc、可変抵抗(第2の可変抵抗)Ra4、抵抗(第5の抵抗)Re、定電圧源(第1の定電圧源)Vini、オペアンプ(第2のオペアンプ)52、コンパレータ(第3のコンパレータ)53を有する。

【0093】

抵抗Rcは、IPD1の内部GND配線(内部基準配線)55、つまり、オープン検出回路14、電流検出回路15、温度検出回路16、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、AND回路17、インバータ18、N型MOSトランジスタMN1、NAND回路19、N型MOSトランジスタMN2のLレベルとなる配線とIPD1のGND端子間に接続されており、一方がオペアンプ52の一方の入力に接続され、他方がオペアンプ52の他方の入力に接続される。オペアンプ52の出力はコンパレータ53の一方の入力に接続されている。コンパレータ53の入力の他方はノード54と接続されており、出力51は図2のNAND回路19の入力に接続されている。可変抵抗Ra4は、一方がノード54と接続され、他方が定電圧源Viniの一方と接続されている。抵抗Reは一方がノード54と接続され、他方が定電圧源Viniの他方およびGND端子と接続されている。

【0094】

ノード54には、定電圧源Viniの電圧値と可変抵抗Ra4の抵抗値と抵抗Reの抵抗値とに基づき決定された電圧が発生する。ノード54の電圧値は、基準電圧Vrefとしてコンパレータ53に入力される。この基準電圧Vrefは、可変抵抗Ra4の値を変更することで任意に変更することができる。

【0095】

通常動作時、抵抗Rcには通常レベルの消費電流Icが流れ、そのレベルに応じた電位差が抵抗Rcの両端に生じる。オペアンプ52は、抵抗Rcの両端の電位差を入力し、この電位差に応じた出力電圧をコンパレータ53の一方の入力に出力する。コンパレータ53に入力されたこの出力電圧は、可変抵抗Ra4により設定された基準電圧Vrefと比較される。通常動作時は、オペアンプ52の出力電圧は基準電圧Vrefよりも小さいため、コンパレータ53は正常を示すHレベル信号を出力する。しかし、パワーMOSFET2の特性劣化により、抵抗Rcに流れる消費電流Icが上昇すると、抵抗Rcの両端の電位差が上昇し、オペアンプ52の出力電圧は大きくなる。そして、コンパレータ53は、オペアンプ52の出力電圧が基準電圧Vref以上である場合は、異常を示すLレベル信号を出力する。

【0096】

例えば、消費電流検出回路50を用いて消費電流Icが初期特性値に基づき定められた設定値の1.1倍以上になった場合を検出する際は、次のように可変抵抗Ra4の抵抗値を設定する。まず、初期特性値に基づき定められた設定値の1.1倍の消費電流Icが流れた時に抵抗Rcの両端に生じる電位差を求める。次に、この電位差がオペアンプ52に入力された際にオペアンプ52が出力する電圧値を求める。そして、この電圧値と基準電圧Vrefが等しくなるように、可変抵抗Ra4の抵抗値を決定する。このように可変抵抗Ra4の抵抗値を設定することで、消費電流Icが初期特性値に基づき定められた設定値の1.1倍よりも小さい場合は、コンパレータ53は正常を示すHレベル信号を出力し、消費電流Icが初期特性値に基づき定められた設定値の1.1倍以上の場合は、コンパレータ53は異常を示すLレベル信号を出力するように、設定することができる。

【0097】

なお、消費電流検出回路50においても可変抵抗Ra4の設定には、図7に示す回路を用いることができる。また、図6に示した消費電流検出回路は一例であり、消費電流を検出することができる回路であれば、どのような回路を用いてもよい。

【0098】

次に、本実施の形態にかかる半導体装置の製造から異常検出までのフローを図8を用いて説明する。まず、本実施の形態にかかる半導体装置であるインテリジェントパワーデバイス(IPD1)を製造する(ステップS1)。次に、パワーMOSFETの初期特性を測定し、この初期特性値に基づき定められた設定値を記録する(ステップS2)。より具体的には、半導体チップ(またはウェハ)の状態で初期特性値(例えば、オン抵抗Ron)を測定し、これに基づいて設定値(例えば可変抵抗Ra1)となるようにトリミング抵抗をレーザ等で切断し、その後半導体チップのリードフレームへの組立・樹脂封止・リードフレームからの切断を行ない、個々のIPD1を完成する。設定値を記録する際は、例えば前述の抵抗値Ra1〜Ra4の値を設定値とする。次に、IPD1をECU(エンジンコントロールユニット)等のシステムに設置する(ステップS3)。次に、IPD1の電源をオンにする(ステップS4)。IPD1の電源がオンになると、IPD1の性能が測定される(ステップS5)。つまり、IPD1は、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50がIPD1の特性値を測定する。

【0099】

そして、ステップS5で測定したIPD1の各特性値と、初期値(初期特性値に基づき定められた設定値)とを比較する(ステップS6)。そして、ステップS5で測定した特性値に問題があるか判断される(ステップS7)。ステップS5で測定した特性値に問題がある場合は、IPD1のコントローラ(マイクロコンピュータ)へ警告(Warning)を出力する(ステップS8)。その後、コントローラから半導体装置の点検をすべき旨のメッセージを出力する(ステップS9)。つまり、コントローラであるマイクロコンピュータからドライバや自動車ディーラー等のユーザへ点検を勧めるメッセージが出力される。そして、このメッセージによりシステム(自動車)の点検が促進され自動車修理工場などで調整、修理が行われることになる(ステップS10)。そのためIPD1が破壊に至ることがなく、安全にシステムを稼動することができる。

【0100】

一方、ステップS5で測定した特性値に問題がない場合、及びステップS8においてマイクロコンピュータへ警告を出力した後、IPD1を動作させる(ステップS11)。その後、入力端子7からIPD1aをオフする制御信号が入力されれば、IPD1の電源をオフし(ステップS12)、ステップS4へと移動し、ステップS4以降の動作を繰り返す。

【0101】

以上で説明したように、本実施の形態にかかるIPD1では、IPD1の初期特性値に基づき定められた設定値と所定のタイミングにおけるIPD1の特性値とに基づき、IPD1の故障に繋がるような特性劣化を検出することができるので、IPD1の故障を未然に防ぐことができる。

【0102】

また、本実施の形態にかかるIPD1では、IPD1に故障の兆候がある場合は、マイクロコンピュータによりドライバ等のユーザへ警告を発することができるので、システム(自動車等)の動作不具合を回避することができ、その結果、システムの安全性を飛躍的に向上させることができる。

【0103】

なお、特許文献1には、パワーMOSFETのゲートにゲート抵抗を設け、パワーMOSFETがオンしているときのゲート抵抗の電圧降下を測定することで、絶縁破壊に起因したオン故障を事前に察知する技術が開示されている。また、特許文献2には、パワーMOSFETが半故障の状態でも故障判定できる故障検知回路に関する技術が開示されている。しかしながら、特許文献1、及び特許文献2にかかる技術では、本実施の形態にかかる発明のように、IPDの初期特性値(製造時の特性値)に基づき定められた設定値を記憶し、当該設定値と所定のタイミングにおけるIPDの特性値とに基づき、IPDの故障に繋がるような特性劣化を検出する点について開示されていない。これに対して本発明は、半導体チップを樹脂封止する前にIPDの初期特性値を測定し、トリミング抵抗を切断して設定値を当該半導体チップに書き込み、その後樹脂封止してIPDを完成している。これにより、IPDを使用するユーザは、改めて初期特性値を測定したり、特性劣化状態を検出するための設定値を定めたり、特性劣化検出回路を追加したりすることなく、IPDの劣化状態を知ることができる。

【0104】

実施の形態2

以下、図面を参照して発明の実施の形態2について説明する。図9は、本実施の形態にかかるIPD(半導体装置)を示すブロック図である。本実施の形態にかかるIPD1aでは、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50の出力が、それぞれAND回路70にも出力され、AND回路70の出力がAND回路11に入力されている。これ以外の部分については、実施の形態1で説明したIPD1と同一であるため、重複した説明を省略する。なお、実施の形態1で説明したIPD1と同一の構成部分には同一の符号を付している。また、図9では、図面が複雑になるため、IPD1aを構成する各要素のLレベルとなる配線と消費電流検出回路50との接続関係の記載を省略しているが、図9においても、図2の場合と同様に消費電流検出回路50は、IPD1aを構成する各要素のLレベルとなる配線、つまり内部GND配線(内部基準配線)とIPD1aのGND端子と接続されている。

【0105】

図9に示す本実施の形態にかかるIPD1aでは、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50のそれぞれに、実施の形態1で設定された初期特性値に基づき定められた設定値(第1の設定値)と、第1の設定値とは異なる値に定められた設定値(第2の設定値)とが記憶されている。そして、本実施の形態で設定された第1の設定値と、所定のタイミングにおけるIPD1aの特性値との比較結果が、AND回路19に出力される。また、第2の設定値についても同時に比較され、比較結果が、AND回路70に出力される。

【0106】

オン抵抗検出回路20は、例えば所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値がオン抵抗の初期特性値に基づき定められた設定値の1.1倍(第1の設定値)以上になった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号21を出力する。また、オン抵抗検出回路20は、例えば所定のタイミングにおけるオン抵抗の特性値がオン抵抗の初期特性値の1.5倍(第2の設定値)以上になった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号71を出力する。

【0107】

ゲートリーク検出回路30は、例えば所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、ゲートリークの初期特性値に基づき定められた設定値である1μA(第1の設定値)以上となった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号31を出力する。また、ゲートリーク検出回路30は、例えば所定のタイミングにおけるゲートリークの特性値が、ゲートリークの初期特性値に基づき定められた設定値である10μA(第2の設定値)以上となった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号72を出力する。

【0108】

オフリーク検出回路40は、例えば所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、オフリークの初期特性値に基づき定められた設定値である1μA(第1の設定値)以上となった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号21を出力する。また、オフリーク検出回路40は、例えば所定のタイミングにおけるオフリークの特性値が、オフリークの初期特性値に基づき定められた設定値である10μA(第2の設定値)以上となった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号73を出力する。

【0109】

消費電流検出回路50は、例えば所定のタイミングにおけるIPD1a消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.1倍(第1の設定値)以上になった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号51を出力する。また、消費電流検出回路50は、例えば所定のタイミングにおける消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.5倍(第2の設定値)以上になった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号74を出力する。

【0110】

すなわち、第1の設定値の条件である次の(1)から(4)の少なくとも1つ以上の条件が満たされた場合は、出力端子(Warning)8から異常を示すLレベル信号が出力される。また、第1の設定値の条件である次の(1)から(4)のいずれの条件も満たさない場合は、出力端子(Warning)8から正常を示すHレベル信号が出力される。

(1)所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値がオン抵抗の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

(2)所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、設定値である1μA以上となった場合。

(3)所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、設定値である1μA以上となった場合。

(4)所定のタイミングにおけるIPD1a消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

【0111】

また、第2の設定値の条件である次の(5)から(8)の少なくとも1つ以上の条件が満たされた場合は、AND回路70はLレベル信号をAND回路11に出力する。そして、AND回路11はドライバ回路12にLレベル信号を出力するので、IPD1aは動作停止となる。一方、第2の設定値の条件である次の(5)から(8)のいずれの条件も満たさない場合は、AND回路70はHレベル信号をAND回路11に出力する。そして、AND回路11はドライバ回路12にHレベル信号を出力するので、IPD1aは動作可能となる。

(5)所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値が、オン抵抗の初期特性値に基づき定められた設定値の1.5倍以上になった場合。

(6)所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、設定値である10μA以上となった場合。

(7)所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、設定値である10μA以上となった場合。

(8)所定のタイミングにおけるIPD1aの消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.5倍以上になった場合。

【0112】

なお、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50に第1の設定値と第2の設定値を検出させる場合は、例えば実施の形態1で説明した図3〜図6で説明した各検出回路をそれぞれ2つ用い、そのそれぞれについて、図7で説明した回路(設定値記憶部)を用いる。

【0113】

次に、本実施の形態にかかる半導体装置の製造から異常検出までのフローを図10を用いて説明する。まず、本実施の形態にかかる半導体装置であるインテリジェントパワーデバイス(IPD)を製造する(ステップS11)。次に、IPD1aの初期特性を測定し、この初期特性値に基づき定められた設定値(第1の設定値と第2の設定値)を記録する(ステップS12)。設定値を記録する際は、例えば前述の抵抗値Ra1〜Ra4の値を設定値とする。次に、IPD1aをECU(エンジンコントロールユニット)等のシステムに設置する(ステップS13)。次に、IPD1aの電源をオンにする(ステップS14)。IPD1aの電源がオンになると、IPD1aの性能が測定される(ステップS15)。つまり、IPD1aは、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50がIPD1aの特性値を測定する。

【0114】

そして、ステップS15で測定したIPD1aの各特性値と、初期値(初期特性値に基づき定められた設定値)とを比較する(ステップS16)。そして、ステップS15で測定した特性値に問題があるか第1の設定値を基準に判断される(ステップS17)。更に、ステップS15で測定した特性値に重大な問題があるか、第2の設定値を基準に判断される(ステップS18)。ステップS15で測定した特性値が第2の設定値の許容範囲外である場合、つまり重大な問題がある場合は、IPD1aはコントローラ(マイクロコンピュータ)へ自己診断を命令し(ステップS22)、IPD1aの電源をオフにし、IPD1aを動作させない(ステップS23)。また、ステップS15で測定した特性値が第2の設定値の許容範囲内である場合、つまり重大な問題がない場合は、IPD1aのコントローラへ警告(Warning)を出力する(ステップS21)。

【0115】

ステップS22、ステップS23の後、コントローラからIPD1aの点検をすべき旨のメッセージを出力する(ステップS24)。つまり、コントローラであるマイクロコンピュータ10からドライバや自動車ディーラーなどへ点検を勧めるメッセージが出力される。そして、このメッセージによりシステム(自動車)の点検が促進され自動車修理工場などで調整、修理が行われることになる(ステップS25)。そのためIPD1aが破壊に至ることがなく、安全にシステムを稼動することができる。

【0116】

一方、ステップS15で測定した特性値に問題がない場合、及びステップS21においてコントローラへ警告を出力した後、IPD1aを動作させる(ステップS19)。その後、入力端子7からIPD1aをオフする制御信号が入力されれば、IPD1aの電源をオフし(ステップS20)、ステップS14へと移動し、ステップS14以降の動作を繰り返す。

【0117】

以上で説明したように、本実施の形態にかかるIPD1aでは、IPD1aの初期特性値に基づき定められた設定値と所定のタイミングにおけるIPD1aの特性値とに基づき、IPD1aの故障に繋がるような特性劣化を検出することができるので、IPD1aの故障を未然に防ぐことができる。

【0118】

特に、本実施の形態にかかるIPD1aでは、IPD1aの初期特性値に基づき定められた設定値を2つ設定し、IPD1aの破壊に近い設定値(第2の設定値)を満たす場合は、IPD1aの動作を停止することができるので、IPD1aの故障により負荷が暴走することを防止することができる。

【0119】

以上、本発明を上記実施形態に即して説明したが、上記実施形態の構成にのみ限定されるものではなく、本願特許請求の範囲の請求項の発明の範囲内で当業者であればなし得る各種変形、修正、組み合わせを含むことは勿論である。

【符号の説明】

【0120】

1、1a 半導体装置(IPD)

2 半導体素子(パワーMOSFET)

3 設定値記憶部

4 検出回路

5 電源端子(Vcc)

6 出力端子(OUT)

7 入力端子

8 出力端子

9 DIAG出力端子

10 コントローラ(マイクロコンピュータ)

11、17、70 AND回路

12 ドライバ回路

13 電流制限回路

14 オープン検出回路

15 電流検出回路

16 温度検出回路

18 インバータ

19 NAND回路

20 オン抵抗検出回路

30 ゲートリーク検出回路

40 オフリーク検出回路

50 消費電流検出回路

【技術分野】

【0001】

本発明は半導体装置、及び半導体装置の特性劣化検出方法に関し、特に所謂インテリジェントパワーデバイス(IPD)である半導体装置の特性劣化を検出する半導体装置、及び半導体装置の特性劣化検出方法に関する。

【背景技術】

【0002】

大きな電力を扱うことが可能なデバイスの一つにパワーMOSFETがある。このパワーMOSFETは、他のパワーデバイスと比べてスイッチング速度が早い等の特徴がある。

【0003】

特許文献1には、電源供給回路のオン、オフを切り替えるスイッチング素子として用いられる半導体素子(パワーMOSFET)のオン故障の兆候を検出し、回路の遮断機能が不能となる前の時点で半導体素子をオフすることにより、電力供給回路を保護することが可能な、電力供給回路のオン故障検出装置が開示されている。特許文献1に開示されている技術では、パワーMOSFETのゲートにゲート抵抗を設け、パワーMOSFETがオンしているときのゲート抵抗の電圧降下を測定することで、絶縁破壊に起因したオン故障を事前に察知することができる。

【0004】

また、特許文献2には、パワーMOSFETが半故障の状態でも故障判定できる故障検知回路に関する技術が開示されている。特許文献2に開示されている技術では、パワーMOSFETを用いたスイッチングモジュールにおいて、出力電圧を比較する比較回路を2つに分け、パワーMOSFETが正常にOFFになっていることを判定する手段と、パワーMOSFETが正常にONになっていることを判定する手段とを独立に設け、更にそれぞれの判定信号を入力し故障を判定する故障判定回路を設けている。

【0005】

また、非特許文献1には、インテリジェントパワーデバイス(IPD)が開示されている。図25は、非特許文献1に開示されているIPDを組み込んだ回路例を示す図である。IPD101は、VCC端子103とGND(接地)端子との間に設置され、コントローラ102の出力端子108から出力される信号を入力端子106で受け、出力端子104に接続されている負荷109の制御を行なう。また、IPD101は自己診断の機能を有し、自己診断の結果をDIAG端子105を通してコントローラ102の入力端子107へ出力する。

【0006】

また、図26は非特許文献1に開示されているIPD101の詳細な回路図である。IPD101は、入力端子106で受けた信号をロジック113で処理し、パワーMOSFET110を制御する。パワーMOSFET110は、ドレインが電源端子(VCC)103と接続され、ソースが出力端子104と接続されている。出力端子104に接続された負荷109に流れる電流はパワーMOSFET110により制御される。また、IPDは、例えば過電流検出回路111、過熱検出回路112等の自己診断機能を有し、予め設定された判定値に達した場合には、パワーMOSFETをカットオフし、その情報を自己診断結果としてDIAG端子105を通してコントローラへフィードバックすることができる。以下で、過電流検出回路111、過熱検出回路112が働く場合の動作について説明する。

【0007】

まず、負荷ショートで過電流検出回路111が動作する場合について説明する。図27(a)は、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流の変化を示す図である。負荷ショートが発生するとパワーMOSFETへ電流定格を超えた過大な電流が流れ、パワーMOSFETは発熱により破壊される。通常、IPDには過大な電流が流れることを防ぐ電流制限回路が設けられている。この電流制限回路を用いることで、図27(b)に示すように過大な電流をある程度まで抑えることが可能である。しかし、この場合も時間と共に発熱しパワーMOSFETは破壊に至る。

【0008】

そこで、図26に示すIPDには、過電流検出回路111が設けられている。この過電流検出回路111は、図27(c)に示すように、パワーMOSFETに流れる電流が、あらかじめIPDに設定されている電流検出閾値を超えた場合、パワーMOSFETをカットオフする機能を有する。この機能によりパワーMOSFETの発熱による破壊を防止することが可能となる。

【0009】

図28は、過電流検出回路111の一例を示す図である。過電流検出回路111はコンパレータ116を含み、コンパレータ116の一方の入力には出力端子104の電位が供給され、他方の入力には電流検出閾値115が供給され、コンパレータ116の出力はロジック113へ入力される。ここで、パワーMOSFET110のオン抵抗を100mΩ、電流定格を2Aとした場合、電流検出閾値は、例えば0.5V(=100mΩ×5A)と設計される。この条件では、パワーMOSFETの出力電流が5Aを超えた場合に、ロジックによりドライバ114が制御され、パワーMOSFET110がカットオフされることになる。

【0010】

次に、負荷ショートで過熱検出回路112が動作する場合について説明する。図29(a)は、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流の変化、及びパワーMOSFETの温度の変化を示す図である。負荷ショートが発生するとパワーMOSFETへ電流定格を超えた電流が流れ、パワーMOSFETは発熱により破壊される。通常、IPDには過大な電流が流れることを防ぐ電流制限回路が設けられている。この電流制限回路を用いることで、図29(b)に示すように過大な電流をある程度まで抑えることが可能である。しかし、この場合も時間と共に発熱しパワーMOSFETは破壊に至る。

【0011】

そこで、図26に示すIPDには、過熱検出回路112が設けられている。この過熱検出回路112は、図29(c)に示すように、パワーMOSFETの温度が、あらかじめIPDに設定されている温度検出閾値を超えた場合、パワーMOSFETをカットオフする機能を有する。この機能によりパワーMOSFETの発熱による破壊を防止することが可能となる。

【0012】

図30は、過熱検出回路112の一例を示す図である。過熱検出回路112は、コンパレータ118を含み、コンパレータ118の一方の入力にはパワーMOSFETと熱的に結合されたダイオード119の電圧降下が供給され、他方の入力には温度検出閾値117が供給され、コンパレータ118の出力はロジック113に入力される。ダイオード119のカソードは定電流源120と接続されている。ここで、27℃のダイオードの電圧降下を0.7V、温度変化を−2mV/℃、温度定格を150℃とした場合、温度検出閾値は0.404V(=0.7V−2mV/℃ × (175℃ −27℃))と設計される。この条件では、パワーMOSFETの温度が175℃を超えた場合に、ロジック113によりドライバ114が制御され、パワーMOSFET110がカットオフされることになる。

【0013】

このように、図26に示したIPDでは、過電流検出回路111、過熱検出回路112がそれぞれ独立に動作をし、異常状態においてパワーMOSFETの破壊を防止することができる。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2007−174756号公報

【特許文献2】実用新案登録第2599788号公報

【非特許文献】

【0015】

【非特許文献1】"MOS集積回路(μPD166005)データ・シート(NECエレクトロニクス)"<URL:http://www.eu.necel.com/_pdf/S19284EJ1V0DS00.PDF>

【発明の概要】

【発明が解決しようとする課題】

【0016】

まず、パワーMOSFETおよびこれを搭載した半導体装置(IPD)の故障に関して説明する。図11はIPDの時間経過に伴う故障率の変化を示した図である。図11に示すように、IPDの故障には、時間順に初期故障領域、偶発故障領域、摩耗故障領域の3つに分けることができる。また、図12はIPDの時間経過に伴う特性値の変化を示した図である。図12に示すように、サージ等の異常状態を経験したIPDでは、異常状態を経験していないIPD(寿命を全うしたIPD)に比べて早く故障する可能性が高い。本発明では、図11における偶発故障領域における故障や、図12における特性が変化する直前(図中のA点、B点)における故障を未然に防ぐことが可能な半導体装置(IPD)を提供する。

【0017】

IPDの故障例としては、(1)パワーMOSFETのオン抵抗増加による故障、(2)パワーMOSFETのリーク電流増加による故障、(3)パワーMOSFETのゲートリーク電流増加による故障、(4)パワーMOSFETを有するIPDの消費電流変動による故障、の4つが挙げられる。以下で、各故障例について説明する。

【0018】

(1)パワーMOSFETのオン抵抗増加による故障

まず、パワーMOSFETのオン抵抗増加による故障について説明する。図13は、負荷ショート等により過大な電流がパワーMOSFETに流れた状態を示す図である。図13に示すように、過大な電流がパワーMOSFETへ流れることにより、パワーMOSFETの金属−半導体の境界でエレクトロマイグレーションが発生する。図14、図15、図16はパワーMOSFETで発生したエレクトロマイグレーションを説明するための図である。図14に示すように、パワーMOSFETに大電流が流れることで金属−半導体の境界においてエレクトロマイグレーションが発生し、パワーMOSFET自体の抵抗が増加する。

【0019】

図15に示すように、このエレクトロマイグレーションが更に成長すると、パワーMOSFETセルのベース領域の抵抗成分に影響を及ぼすようになる。この結果、図16に示すように、パワーMOSFETの寄生バイポーラトランジスタが動作し、特に、スイッチングにおけるターンオフで、パワーMOSFETを構成するセルの中で最も影響を受けたセルへ電流集中が発生する。この寄生バイポーラトランジスタによる電流集中により特定のセルが急に発熱し、パワーMOSFETが故障する。この事例は、パワーMOSFETのオン抵抗の変化は小さなものであるが、このオン抵抗の上昇が瞬時にパワーMOSFETを故障させる場合の事例である。

【0020】

(2)パワーMOSFETのリーク電流増加による故障

図17は、パワーMOSFETの製造ばらつきが原因で、ソース拡散領域(N+)の横広がりが大きくなった場合を示す図である。ソース拡散領域の横広がりが大きいパワーMOSFETでは、パワーMOSFETセルの実行チャネル長が短いため、図18に示すようにドレイン・ソース間電圧が大きくなると他のセルより多くの電流が流れる。そのため、ソレノイドなどのアクチュエータが負荷である場合、負荷の持つインダクタンス成分によりパワーMOSFETのスイッチングにおけるターンオフでパワーMOSFETのドレイン・ソース間電圧に高電圧が発生する。これにより、毎回のスイッチングでそのパワーMOSFETセルに想定以上の電流が流れる。

【0021】

このとき、図19に示すように、該当セルを走る電子がインパクトイオン化を起こし、プラス電荷がパワーMOSFETのゲート酸化膜に取り込まれる場合がある。ゲート酸化膜にプラス電荷が取り込まれると、該当セルにおいてリーク電流が生じ、さらに他のセルよりも多くの電流が流れる(フィードフォワードの現象)。最終的には、該当セルでまかないきれない電流が集中することで、セル自体が急に発熱し故障に至る。この事例は、パワーMOSFETの総リーク電流としては小さな値であるが、電流が特定セルに集中することにより瞬時にパワーMOSFETが故障する場合の事例である。

【0022】

(3)パワーMOSFETのゲートリーク電流増加による故障

次に、パワーMOSFETにサージ電圧が印加され、パワーMOSFETのゲート酸化膜にリーク箇所が生じた場合を考える。図20は、サージ電圧印加によりゲート・ソース間にリーク箇所が生じた場合を示す図である。パワーMOSFETは、図21に示すように、セルと呼ばれる単位構成が複数並列接続されている。このうち、サージ電圧印加により1つのセルのゲート・ソース間にリーク箇所が生じても、リークの値が小さい場合、すなわち、ドライバの電流供給能力がリーク電流に対して大きい場合、パワーMOSFETの動作に影響を与えない。

【0023】

しかし、ゲート・ソース間に電圧が印加され続けると(パワーMOSFETのオン状態)、リーク箇所の電流量が突如増し、不可逆的な遷移を見せることがある。この不可逆的な遷移が生じるとパワーMOSFETの動作に影響を及ぼし、ゲート・ソース電圧を印加してもパワーMOSFETがオン状態とならない、いわゆるオフ故障を起こす。

【0024】

次に、リーク箇所がゲート・ドレイン間である場合について説明する。図22は、サージ電圧印加によりゲート・ドレイン間にリーク箇所が生じた場合を示す図である。上記と同様に、パワーMOSFETは、図23に示すように、セルと呼ばれる単位構成が複数並列接続されている。このうち、サージ電圧印加により1つのセルのゲート・ドレイン間にリーク箇所が生じても、リークの値が小さい場合、すなわち、ドライバの電流供給能力がリーク電流に対して大きい場合、パワーMOSFETの動作に影響を与えない。

【0025】

しかし、ゲート・ドレイン間に電圧が印加され続けると(パワーMOSFETのオン状態)、リーク箇所の電流量が突如増し、不可逆的な遷移を見せることがある。この不可逆的な遷移が生じるとパワーMOSFETの動作に影響を及ぼし、パワーMOSFETがオフ状態とならない、いわゆるオン故障を起こす。

【0026】

この事例は、いずれの場合もパワーMOSFETのゲートリーク電流としては小さな値であるが、電流が突如増すことにより、パワーMOSFETを制御することができなくなる故障の事例である。

【0027】

(4)IPDの消費電流変動による故障

次に、図24(a)に示すように、IPDの制御回路の配線パターン間(配線1と配線2の間)に配線パターンの残りがある場合を考える。IPDの製造段階の検査において、配線1と配線2が電気的にオープン状態となっておりその検査をパスしたとする。しかし、その後のIPD稼動時において、例えば環境温度の変化により、配線パターン残りが伸縮し配線1と配線2が抵抗成分を持ちながら電気的にショート状態となると、配線1と配線2との間に電流が流れる。図24(b)はこの状態を示す回路図である。

【0028】

この場合、配線パターン残りの抵抗が大きいため、IPDの総消費電流の変動は小さく、またIPDの動作に影響を及ぼすものでもない。しかしながら、IPDが更に稼動されると、配線パターン残りの抵抗が小さくなり、突如としてIPDに影響を及ぼす。この影響により、IPDは制御不能となり故障と判断される。この事例は、IPDの総消費電流の増減としては小さな値であるが、配線パターン残りの抵抗成分の変動により突如として故障にいたる場合を示す事例である。

【0029】

以上、4つの故障例で示したとおり、IPDの故障へ至るまでには、パワーMOSFETのオン抵抗、リーク電流(ゲートリーク、オフリーク)、IPDの消費電流の小さな変化があり、その後これらの値が急峻に変化し、故障が生じる。つまり、偶発故障領域の故障を未然に防ぐ、あるいはサージ等の異常状態を経験したIPDのその後の劣化進行による故障を防ぐためには、前述のパワーMOSFETのオン抵抗、リーク電流、IPDの消費電流の小さな変化をモニターすることが必要となる。

【0030】

また、前述の通り、図25、図26で説明したIPDは、異常状態からパワーMOSFETを保護するために、過電流検出回路、過熱検出回路を備えている。しかしながら、IPDが突然状態遷移を起こし、IPDの機能が損なわれる場合には、過電流検出回路、過熱検出回路で充分にIPDを保護できるわけではない。

【0031】

例えば、異常状態として負荷がショートした場合を考える。前述の通り、負荷のショートにより、たとえ電流制限によりパワーMOSFETへ流れる電流が制限されたとしても、一時的にはパワーMOSFETへは定格を超えた大電流が流れる。この大電流により、パワーMOSFETを構成するセルのうち電流密度の高い一部のセルにエレクトロマイグレーションが発生する。そして、IPDが稼動している間エレクトロマイグレーションが進行し、IPDの特性としては出力オン抵抗が若干高くなる。

【0032】

例えば、IPDのパワーMOSFETを構成するセルが15000セルあり、その中の1000セルがエレクトロマイグレーションにより抵抗値が高くなるとする。この場合、オープン状態、すなわち抵抗値が無限大となると、IPDのパワーMOSFETのオン抵抗は15000/14000倍となる。つまり、製造初期のオン抵抗が100mΩである場合、エレクトロマイグレーションによるオン抵抗は107.143mΩとなる。

【0033】

この場合、IPDのその後の稼動が定格以内、例えば出力電流が2A以内であれば、パワーMOSFETの電圧降下は最大214.286mVととなり、前述の過電流検出回路は当然ながら働かない(過電流検出の閾値を500mVとした場合)。また過熱検出回路も通常動作において温度定格(例えば150℃)に充分なマージンをとり、例えば100℃以下となるように、IPDの使用条件を設定しているため、過熱検出回路も働かない(過熱検出の閾値を175℃とした場合)。

【0034】

しかしながら、上述したIPDの故障例の「(1)パワーMOSFETのオン抵抗増加による故障」で説明したとおり、パワーMOSFETのセルにおけるエレクトロマイグレーションは通常動作のスイッチング、特にターンオフで寄生バイポーラトランジスタが動作する。この寄生バイポーラトランジスタによる電流集中により特定のセルが急に発熱し、パワーMOSFETが故障する。このように、パワーMOSFETは突然の状態遷移により突如破壊に至る場合もある。よって、背景技術で説明したIPDが備える過電流検出回路や過熱検出回路では突然の状態遷移に対しては対応できないため、IPDが故障する場合があるという問題があった。

【課題を解決するための手段】

【0035】

本発明にかかる半導体装置は、半導体装置の初期特性値に基づき定められた設定値を記憶する設定値記憶部と、所定のタイミングにおける前記半導体装置の特性値と前記設定値記憶部に記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する検出回路と、を備える。

【0036】

本発明にかかる半導体装置では、半導体装置の初期特性値に基づき定められた設定値と所定のタイミングにおける前記半導体装置の特性値とに基づき、半導体装置の故障に繋がるような特性劣化を検出することができるので、半導体装置の故障を未然に防ぐことができる。

【0037】

本発明にかかる半導体装置の特性劣化検出方法は、前記半導体装置の初期特性値に基づき定められた設定値を記憶し、所定のタイミングにおける前記半導体装置の特性値と前記記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する。

【0038】

本発明にかかる半導体装置の特性劣化検出方法では、半導体装置の初期特性値に基づき定められた設定値と所定のタイミングにおける前記半導体装置の特性値とに基づき、半導体装置の故障に繋がるような特性劣化を検出することができるので、半導体装置の故障を未然に防ぐことができる。

【発明の効果】

【0039】

本発明により半導体装置の故障に繋がるような特性劣化を検出することができる半導体装置、及び半導体装置の特性劣化検出方法を提供することができる。

【図面の簡単な説明】

【0040】

【図1】実施の形態1にかかる半導体装置(IPD)を示すブロック図である。

【図2】実施の形態1にかかる半導体装置(IPD)の詳細を説明するためのブロック図である。

【図3】実施の形態1にかかる半導体装置(IPD)のオン抵抗検出回路の一例を示す回路図である。

【図4】実施の形態1にかかる半導体装置(IPD)のゲートリーク検出回路の一例を示す回路図である。

【図5】実施の形態1にかかる半導体装置(IPD)のオフリーク検出回路の一例を示す回路図である。

【図6】実施の形態1にかかる半導体装置(IPD)の消費電流検出回路の一例を示す回路図である。

【図7】実施の形態1にかかる半導体装置(IPD)の設定値記憶部の一例を示す回路図である。

【図8】実施の形態1にかかる半導体装置(IPD)の製造から異常検出までのフローを説明するためのフローチャートである。

【図9】実施の形態2にかかる半導体装置(IPD)を示すブロック図である。

【図10】実施の形態2にかかる半導体装置(IPD)の製造から異常検出までのフローを説明するためのフローチャートである。

【図11】IPDの時間経過に伴う故障率の変化を示す図である。

【図12】IPDの時間経過に伴う特性値の変化を示す図である。

【図13】負荷ショートによりパワーMOSFETに過大な電流が流れた場合を示す図である。

【図14】パワーMOSFETにエレクトロマイグレーションが発生した状態を示す部分断面図である。

【図15】パワーMOSFETにエレクトロマイグレーションが発生した状態を示す部分断面図である。

【図16】パワーMOSFETに寄生バイポーラトランジスタが発生した状態を示す部分断面図である。

【図17】パワーMOSFETのソース拡散領域の横広がりが大きい場合を示す部分断面図である。

【図18】パワーMOSFETのソース拡散領域の横広がりが大きい場合のドレイン・ソース間電圧と電流値との関係を示す図である。

【図19】パワーMOSFETのゲート酸化膜にプラス電荷が取り込まれた場合を示す部分断面図である。

【図20】サージ電圧印可によりパワーMOSFETのゲート・ソース間にリーク箇所が生じた場合を示す部分断面図である。

【図21】パワーMOSFETのゲート・ソース間にリーク箇所が生じた場合の等価回路図である。

【図22】サージ電圧印可によりパワーMOSFETのゲート・ドレイン間にリーク箇所が生じた場合を示す部分断面図である。

【図23】パワーMOSFETのゲート・ドレイン間にリーク箇所が生じた場合の等価回路図である。

【図24】(a)IPDの制御回路の配線パターン間(配線1と配線2の間)に配線パターンの残りがある場合を示す部分平面図である。(b)配線パターン間(配線1と配線2の間)がショートした場合の回路図である。

【図25】背景技術にかかるインテリジェントパワーデバイス(IPD)を組み込んだ回路例を示すブロック図である。

【図26】背景技術にかかるIPDのブロック図である。

【図27】背景技術にかかるIPDにおいて、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流の変化を示す図である。(a)は電流制限回路、過電流検出回路を有しない場合。(b)は電流制限回路を有する場合。(c)は電流制限回路および過電流検出回路を有する場合。

【図28】過電流検出回路の一例を示す回路図である。

【図29】背景技術にかかるIPDにおいて、パワーMOSFETがオンし、その後、負荷ショートが発生した時のパワーMOSFETの出力電流と温度の変化を示す図である。(a)は電流制限回路、過熱検出回路を有しない場合。(b)は電流制限回路を有する場合。(c)は電流制限回路および過熱検出回路を有する場合。

【図30】過熱検出回路の一例を示す回路図である。

【発明を実施するための形態】

【0041】

実施の形態1

以下、図面を参照して本発明の実施の形態1について説明する。図1は、本実施の形態にかかるIPD(半導体装置)1を示すブロック図である。本実施の形態にかかるIPD1は、半導体製造工程により製造され、半導体チップ(またはウェハ)が完成した状態のIPD1の初期特性値に基づき定められた設定値を記憶する設定値記憶部3と、IPD1がECU(エンジンコントロールユニット)等のシステムに設置された状態での所定のタイミングにおけるIPD1の特性値と、設定値記憶部3に記憶された設定値とに基づき、IPD1の特性劣化を検出する検出回路4と、を備える。

【0042】

本実施の形態にかかるIPD1が備えるパワー半導体素子は、例えばパワーMOSFET2である。パワーMOSFET2は、例えばN型のパワーMOSFETであり、ドレインが電源端子(Vcc)5と接続され、ソースが出力端子(OUT)6と接続され、ゲートが入力端子(IN)と接続されている。パワーMOSFET2のゲートには制御信号が供給される。なお、本実施の形態にかかる半導体装置1では、パワーMOSFET2と入力端子7との間にドライバ回路を設けてもよい。また、出力端子6には負荷が接続される。なお、パワー半導体素子は、パワーMOSFETに限らず、IGBT(Insulated Gate Bipolar Transistor)でも良い。

【0043】

本実施の形態にかかるIPD1において検出回路4とは、例えばパワーMOSFET2のオン抵抗の特性劣化を検出するための回路、パワーMOSFET2のゲートリークの特性劣化を検出するための回路、パワーMOSFET2のオフリークの特性劣化を検出するための回路、IPD1に流れる消費電流の特性劣化(電圧降下)を検出するための回路である。なお、本実施の形態ではこれら以外にも、IPDの特性劣化を検出するために用いることができる特性値であればどのようなものを用いてもよい。

【0044】

また、本実施の形態にかかるIPD1では、検出回路4から検出結果が出力され、この検出結果は出力端子8から出力される。つまり、出力端子8からは、検出回路4が異常を検出した場合には異常を知らせる信号が出力され、検出回路4が異常を検出しない場合は正常を知らせる信号が出力される。IPD1を制御するコントローラ(図2のマイクロコンピュータ10)は、出力端子8から異常を知らせる信号が出力されると、例えば、IPD1を交換する必要があることを知らせるメッセージを表示したり、IPD1の制御パラメータを変更したり、IPD1の動作を停止する。

【0045】

また、検出回路4がIPD1の特性劣化を検出する際に用いる、所定のタイミングにおけるIPD1の特性値とは、例えばIPD1の電源投入時における特性値、IPD1の入力端子7に制御信号が入力されたタイミングにおける特性値、コントローラからIPD1へIPD1の特性劣化を検出する旨の命令信号が入力されたタイミングにおける特性値、IPD1の稼働中における一定周期毎における特性値などである。なお、IPD1の特性値を取得する所定のタイミングは、これら以外にも任意に設定することができる。

【0046】

次に、本実施の形態にかかるIPD(半導体装置)の詳細な構成について図2を用いて説明する。図2は本実施の形態にかかるIPD1の詳細な構成を示すブロック図である。本実施の形態にかかるIPD1は、パワーMOSFET2、ドライバ回路12、電流制限回路13、オープン検出回路14、電流検出回路15、温度検出回路16、DIAG出力端子9を備える。

【0047】

パワーMOSFET2のドレインは電源端子(Vcc)5と接続され、ゲートはドライバ12と接続され、ソースは出力端子(OUT)6と接続されている。また、パワーMOSFET2のゲート・ソース間には、電流制限回路13が接続されている。出力端子(OUT)6には負荷RLが接続されており、パワーMOSFET2は負荷RLに対して電流を供給する。また、ドライバ回路12はパワーMOSFET2を駆動するための回路である。

【0048】

電流制限回路13は、異常状態、例えば出力端子6と負荷のGND端子が短絡された負荷ショートにより、パワーMOSFET2に過大電流が流れることでパワーMOSFET2が劣化・破壊することを防止するために出力電流を制限する回路である。電流制限回路13を内蔵していない場合は、例えば100A以上の過大電流がパワーMOSFET2に流れる。しかし、電流制限回路13を設けることで、パワーMOSFET2に流れる電流を15A程度に制限することができる。

【0049】

オープン検出回路14は、出力端子(OUT)6のオープン状態を検出するための回路である。つまり、オープン検出回路14は、本来、出力端子6に接続されているべき負荷RLが接続されていないことを検出する回路である。

【0050】

電流検出回路15は、パワーMOSFET2に定格電流以上の電流が流れているかを検出する回路である。例えば、パワーMOSFET2の定格電流が2Aの場合、何らかの異常(例えば、前述の負荷ショート)によりパワーMOSFET2に15Aの電流が流れた場合に電流検出される。

【0051】

温度検出回路16は、異常状態(例えば、前述の負荷ショート)により、パワーMOSFET2の温度が予め設定された温度(例えば175℃)を超えた場合に異常を検出する回路である。

【0052】

オープン検出回路14、電流検出回路15、温度検出回路16の各出力はAND回路17に入力される。そして、オープン検出回路14、電流検出回路15、温度検出回路16の各出力のすべてがHレベル(Highレベル、正常)である場合、AND回路17はHレベルの信号をインバータ18とAND回路11に出力する。インバータ18はAND回路17からのHレベル信号をLレベル(Lowレベル)信号に反転し、Lレベル信号をN型MOSトランジスタMN1のゲートに供給する。この場合、MN1のゲートはLレベルであるため、DIAG出力端子9からは正常を示すHレベル信号が出力される。

【0053】

一方、オープン検出回路14、電流検出回路15、温度検出回路16の各出力のうちいずれかがLレベル(異常)である場合、AND回路17はLレベルの信号をインバータ18に出力する。インバータ18はAND回路17からのLレベル信号をHレベル信号に反転し、Hレベル信号をN型MOSトランジスタMN1のゲートに供給する。MN1のゲートはHレベルであるため、DIAG出力端子9からは異常を示すLレベル信号が出力される。

【0054】

つまり、DIAG出力端子9からは、オープン検出回路14が出力端子(OUT)6に負荷が接続されていない状態を検出した場合、電流検出回路15が過大な電流が流れている状態を検出した場合、温度検出回路16が過大な温度となっている状態を検出した場合、のいずれか1つ以上の場合に、コントローラ(マイクロコンピュータ)10へ異常を通知する信号が出力される。

【0055】

また、IPD1を制御するコントローラ(マイクロコンピュータ)10は、IPD1の入力端子(IN)7にIPD1をオン/オフする制御信号を出力する。この制御信号は、IPD1のAND回路11に入力される。また、AND回路11には、AND回路17からの出力も入力される。よって、AND回路11は、マイクロコンピュータ10からの信号がHレベルで、かつAND回路17からの信号がHレベルである場合に、Hレベル信号をドライバ回路12へ出力する。一方、AND回路11は、マイクロコンピュータ10からの信号とAND回路17からの信号の少なくとも1つがLレベルである場合に、Lレベル信号をドライバ回路12へ出力する。ドライバ回路12は、AND回路11がHレベル信号を出力した場合はパワーMOSFET2を駆動し、AND回路11がLレベル信号を出力した場合はパワーMOSFET2を駆動しない。すなわち、オープン検出回路14、電流検出回路15、温度検出回路16のいずれかが異常を示している場合は、ドライバ回路12はパワーMOSFET2を駆動しないように制御する。

【0056】

また、図2に示すように本実施の形態にかかるIPD1は、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50を備える。オン抵抗検出回路20の中には、図1に示した設定値記憶部3に対応する回路と検出回路4に対応する回路がそれぞれ設けられている。ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50についても同様である。また、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50には、IPD1に電源が投入されたことを通知するための電源投入信号が入力される。

【0057】

オン抵抗検出回路20は、パワーMOSFET2のオン抵抗の初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおけるオン抵抗の特性値がオン抵抗の初期特性値に基づき定められた設定値の1.1倍以上になった場合に、オン抵抗検出回路20が異常を検出するものとする。

【0058】

ゲートリーク検出回路30は、オフ状態、又はオン状態において、パワーMOSFET2のゲートリークの初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおけるゲートリークの特性値が、ゲートリークの初期特性値(製造時の特性値)に基づき定められた設定値である1μA以上となった場合に、ゲートリーク検出回路30が異常を検出するものとする。ここで、初期特性値に基づき定められた設定値とは、ゲートリークの初期特性値(例えば、0μA)に対して任意の値(例えば、1μA)を加えた値を設定値(=0μA+1μA)とすることである。

【0059】

オフリーク検出回路40は、パワーMOSFET2のオフリークの初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるパワーMOSFET2のオフリークの特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおけるオフリークの特性値が、オフリークの初期特性値(製造時の特性値)に基づき定められた設定値である1μA以上となった場合に、オフリーク検出回路40が異常を検出するものとする。ここで、初期特性値に基づき定められた設定値とは、オフリークの初期特性値(例えば、0μA)に対して任意の値(例えば、1μA)を加えた値を設定値(=0μA+1μA)とすることである。

【0060】

消費電流検出回路50は、IPD1の内部GND配線(内部基準配線)55に流れる消費電流Icの初期特性値(製造時の特性値)に基づき定められた設定値と、所定のタイミングにおけるIPD1の消費電流の特性値とに基づき、IPD1の特性劣化を検出する回路である。本実施の形態では、例として、所定のタイミングにおける消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.1倍以上になった場合に、消費電流検出回路50が異常を検出するものとする。

【0061】

オン抵抗検出回路20の出力21、ゲートリーク検出回路30の出力31、オフリーク検出回路40の出力41、消費電流検出回路50の出力51はそれぞれ、NAND回路19に入力される。本実施の形態では、例えば各出力21、31、41、51がHレベルの時は正常であり、Lレベルの時は異常であるとしている。NAND回路19の出力はN型MOSトランジスタMN2のゲートに接続されており、NAND回路19がLレベルの信号を出力する場合は、出力端子(Warning)8から正常を示すHレベルの信号が出力される。一方、NAND回路19がHレベルの信号を出力する場合は、出力端子(Warning)8から異常を示すLレベルの信号が出力される。

【0062】

すなわち、次の(1)から(4)の少なくとも1つ以上の条件が満たされた場合は、出力端子(Warning)8から異常を示すLレベル信号が出力され、次の(1)から(4)のいずれの条件も満たさない場合は、出力端子(Warning)8から正常を示すHレベル信号が出力される。

(1)所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値が、パワーMOSFET2のオン抵抗の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

(2)所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、設定値である1μA以上となった場合。

(3)所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、設定値である1μA以上となった場合。

(4)所定のタイミングにおけるIPD1の消費電流の特性値が、IPD1の消費電流の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

【0063】

マイクロコンピュータ10は、出力端子(Warning)8からの信号を入力することで、IPD1の経時劣化の状態等を判断することができる。また、マイクロコンピュータ10は、異常を示す信号を入力した場合は、例えば、IPD1を交換する必要があることを知らせるメッセージを表示したり、IPD1の制御パラメータを変更したり、IPD1の動作を停止することができる。

【0064】

また、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50がIPD1の特性劣化を検出する際に用いる、所定のタイミングにおけるIPD1の特性値とは、例えばIPD1の電源投入時における特性値、IPD1の入力端子7に制御信号が入力されたタイミングにおける特性値、コントローラからIPD1へIPD1の特性劣化を検出する旨の命令信号が入力されたタイミングにおける特性値、IPD1の稼働中における一定周期毎における特性値などである。なお、IPD1の特性値を取得する所定のタイミングは、これら以外にも任意に設定することができる。

【0065】

次に、本実施の形態にかかるIPD1のオン抵抗検出回路20の具体的な回路構成の一例について説明する。図3は、本実施の形態にかかるIPD1のオン抵抗検出回路20の一例を示す回路図である。オン抵抗検出回路20は、抵抗(第1の抵抗)Rs、抵抗(第2の抵抗)Rf、可変抵抗(第1の可変抵抗)Ra1、コンパレータ(第1のコンパレータ)25を有する。

【0066】

抵抗Rsは、一方がパワーMOSFET2のソース側のノード(第1のノード)24に接続され、他方がノード(第2のノード)26と接続されている。可変抵抗Ra1は、一方がパワーMOSFET2のドレイン側のノード22と接続され、他方がノード(第3のノード)23と接続されている。抵抗Rfは、一方がノード23と接続され、他方がノード26と接続されている。また、コンパレータ25は、入力がノード23、ノード24と接続され、出力21が図2のNANDの入力に接続されている。

【0067】

図3に示すオン抵抗検出回路20において、パワーMOSFET2をオンさせると、パワーMOSFET2のソースから電流Ioutが流れる。このとき、電源端子(Vcc)5とノード26(出力端子(OUT)6)との間の電圧Vcc−Voutと、パワーMOSFET2のドレイン・ソース間電圧Vdsを測定すると、次の関係が成り立つ。

【0068】

Vds/(Vcc−Vout)=Ron×Iout/(Ron×Iout+Rs×Iout)=Ron/(Ron+Rs)・・・式1

【0069】

式1において、RonはパワーMOSFET2のオン抵抗の初期特性値に基づき定められた設定値である。よって、パワーMOSFET2のオン抵抗が、オン抵抗の初期特性値に基づき定められた設定値の1.1倍となるようなRa1を、次の関係式を用いて求めることができる。

【0070】

Ron×1.1/(Ron×1.1+Rs)=Ra1/(Ra1+Rf)・・・式2

【0071】

例えば、オン抵抗の設定値をRon=100mΩ、Rs=10mΩ、Rf=10kΩとすると、式2を用いて、Ra1=110kΩとなる。よって、この値の抵抗値をオン抵抗検出回路20の設定値とする。

【0072】

このとき、図3に示すオン抵抗検出回路20のノード23には、電源端子(Vcc)5と出力端子(OUT)6との間の電圧Vcc−Voutを、抵抗Ra1と抵抗Rfの抵抗値に基づき分割された電圧値であるVrefが発生する(Vrefは設定値なので不変)。また、オン抵抗検出回路20のノード24には、電源端子(Vcc)5と出力端子(OUT)6との間の電圧Vcc−Voutを、パワーMOSFET2のオン抵抗Ronと抵抗Rsの値に基づき分割された電圧値であるVmが発生する。

【0073】

ここで、初期状態では、Ra1=110kΩ、Rf=10kΩであり、また、Ron=100mΩ、Rs=10mΩであるため、ノード23の電圧Vrefは、ノード24の電圧Vmよりも小さい。コンパレータ25は、ノード23の電圧Vrefとノード24の電圧Vmを比較し、Vref<Vmの場合は正常を示す信号(Hレベル)を出力する。

【0074】

一方、パワーMOSFET2の特性劣化により、オン抵抗Ronの値が大きくなるにつれて、ノード24の電圧Vmも次第に小さくなる。よって、コンパレータ25は、ノード23の電圧Vrefとノード24の電圧Vmとを比較し、Vref≧Vmの場合は異常を示す信号(Lレベル)を出力する。つまり、パワーMOSFET2のオン抵抗がRon×1.1(すなわち、110mΩ)以上になった場合、ノード23の電圧Vrefとノード24の電圧VmはVref≧Vmとなるため、この大小関係をコンパレータ25を用いて比較することで、パワーMOSFET2のオン抵抗の異常を検出することができる。

【0075】

なお、図3に示したオン抵抗検出回路は一例であり、パワーMOSFET2のオン抵抗を検出することができる回路であれば、どのような回路を用いてもよい。

【0076】

また、Ra1の値をオン抵抗検出回路20の設定値とする場合は、例えば図7に示す回路(設定値記憶部)を用いることができる。図7に示す回路は、ノード60とノード61との間に直列に接続された複数の抵抗を備える。図7に示す抵抗の値は一例であり、任意に変更可能である。また、ノード60は図3のオン抵抗検出回路20のノード22に対応し、ノード61は図3のオン抵抗検出回路20のノード23に対応している。直列に接続された複数の抵抗の各々の両端には、それぞれP型MOSトランジスタMP10〜MP16のソース・ドレインが接続されている。また、P型MOSトランジスタMP10〜MP16のゲートには、それぞれ定電流源62−1〜62−7が接続されている。定電流源62−1〜62−7と基準電源との間には、P型MOSトランジスタMP10〜MP16に対応した位置にトリミング抵抗63−1〜63−7が設けられている。ここで、基準電源はP型MOSトランジスタMP10〜MP16をオンさせることのできる電位であればよく、例えばIPD1の内部GND配線(内部基準配線)に接続されている。

【0077】

例えば、本実施の形態で説明したようにRa1=110kΩに設定する場合は、64kΩ+32kΩ+8kΩ+4kΩ+2kΩの抵抗を選択する(図7の場合は、64kΩは必ず選択される)。つまり、トリミング抵抗63−2、63−3、63−5、63−7を、レーザを照射して切断することで、P型MOSトランジスタMP11、MP12、MP14、MP16がオフする。よって、2kΩ、4kΩ、8kΩ、32kΩの抵抗が選択されるため、ノード60とノード61との間の抵抗値は110kΩとなる。

【0078】

図7に示す回路では、64kΩ〜132kΩまで、1kΩ単位でRa1を設定することができる。よって、パワーMOSFET2のオン抵抗Ronが個体に80mΩ〜120mΩでばらついたとしても、オン抵抗Ronの1.1倍の検出点を設定することができる。つまり、Ra1を88kΩ〜132kΩの範囲で設定すればよい。なお、図7に示したRa1を設定する回路は一例であり、Ra1を設定することができる回路であればどのような回路を用いてもよい。

【0079】

次に、本実施の形態にかかるIPD1のゲートリーク検出回路30の具体的な回路構成の一例について説明する。図4は、本実施の形態にかかるIPD1のゲートリーク検出回路30の一例を示す回路図である。ゲートリーク検出回路30は、抵抗(第3の抵抗)Rg、可変抵抗(第2の可変抵抗)Ra2、抵抗(第5の抵抗)Rd、定電圧源(第1の定電圧源)Vini、オペアンプ(第1のオペアンプ)32、コンパレータ(第2のコンパレータ)33を有する。

【0080】

抵抗Rgは、パワーMOSFET2のゲートに接続されており、一方がオペアンプ32の一方の入力に接続され、他方がオペアンプ32の他方の入力に接続される。可変抵抗Ra2は、一方がパワーMOSFET2のドレイン側のノード35に接続され、他方がノード34と接続されている。抵抗Rdは、一方がノード34と接続され、他方が定電圧源Viniの一方と接続されている。また、定電圧源Viniの他方はノード35と接続されている。オペアンプ32の入力は抵抗Rgの両端に接続され、出力はコンパレータ33の一方の入力に接続されている。コンパレータ33の入力の他方はノード34と接続されており、出力31は図2のNANDの入力に接続されている。

【0081】

ノード34には、定電圧源Viniの電圧値と可変抵抗Ra2の抵抗値と抵抗Rdの抵抗値とに基づき決定された電圧が発生する。ノード34の電圧値は、基準電圧Vrefとしてコンパレータ33に入力される。この基準電圧Vrefは、可変抵抗Ra2の値を変更することで任意に変更することができる。

【0082】

また、パワーMOSFET2にゲートリークがない場合、抵抗Rgにはゲートリーク電流Igが流れない。この場合は、抵抗Rgの両端、つまりオペアンプ32の入力には電位差が生じない。しかし、パワーMOSFET2にゲートリークがある場合、抵抗Rgにはゲートリーク電流Igが流れるため、抵抗Rgの両端、つまりオペアンプ32の入力には電位差が生じる。オペアンプ32は、抵抗Rgの両端の電位差に基づいて信号を出力する。つまり、ゲートリーク電流Igが大きくなるほど、抵抗Rgの両端の電位差が大きくなり、オペアンプ32の出力電圧は大きくなる。オペアンプ32の出力電圧はコンパレータ33の入力の一方に入力され、可変抵抗Ra2により設定された基準電圧Vrefと比較される。コンパレータ33は、オペアンプ32の出力電圧が基準電圧Vrefよりも小さい場合は、正常を示すHレベル信号を出力し、オペアンプ32の出力電圧が基準電圧Vref以上である場合は、異常を示すLレベル信号を出力する。

【0083】

例えば、ゲートリーク検出回路30を用いてゲートリーク電流Igが1μA以上となった場合を検出する際は、次のように可変抵抗Ra2の抵抗値を設定する。まず、ゲートリーク電流Igが1μA流れた時に抵抗Rgの両端に生じる電位差を求める。次に、この電位差がオペアンプ32に入力された際にオペアンプ32が出力する電圧値を求める。次に、この電圧値と基準電圧Vrefとが等しくなるように、可変抵抗Ra2の抵抗値を決定する。このように可変抵抗Ra2の抵抗値を設定することで、ゲートリーク電流Igが1μAよりも小さい場合は、コンパレータ33は正常を示すHレベル信号を出力し、ゲートリーク電流Igが1μA以上の場合は、コンパレータ33は異常を示すLレベル信号を出力するように、設定することができる。

【0084】

なお、ゲートリーク検出回路30においても可変抵抗Ra2の設定には、図7に示す回路を用いることができる。また、図4に示したゲートリーク検出回路は一例であり、パワーMOSFET2のゲートリークを検出することができる回路であれば、どのような回路を用いてもよい。

【0085】

次に、本実施の形態にかかるIPD1のオフリーク検出回路40の具体的な回路構成の一例について説明する。図5は、本実施の形態にかかるIPD1のオフリーク検出回路40の一例を示す回路図である。オフリーク検出回路40は、抵抗(第6の抵抗)Rs、可変抵抗(第3の可変抵抗)Ra3、定電圧源(第2の定電圧源)Vini、N型MOSトランジスタMN3〜MN5、P型MOSトランジスタMP1、MP2、オペアンプ(第3のオペアンプ)43を有する。

【0086】

抵抗Rsは、パワーMOSFET2のソースに接続されている。また、抵抗Rsの両端は、それぞれオペアンプ43の入力に接続されている。オペアンプ43の出力はN型MOSトランジスタ(第1のトランジスタ)MN3のゲートに接続されている。N型MOSトランジスタMN3のドレインはパワーMOSFET2のソースに、ソースはノード(第4のノード)44に接続されている。ノード44は、N型MOSトランジスタMN5のドレイン及びゲートに接続されている。N型MOSトランジスタMN5のソースはN型MOSトランジスタMN4のソースに、ゲートはN型MOSトランジスタMN4のゲートに接続されている。N型MOSトランジスタMN4のドレインはノード(第5のノード)42に接続されている。ここで、N型MOSトランジスタMN4、MN5はカレントミラー回路(第1のカレントミラー回路)を構成する。

【0087】

また、P型MOSトランジスタMP1のソースはP型MOSトランジスタMP2のソース、電源端子(Vcc)5、及び定電圧源(第2の定電圧源)Viniの一方と接続されている。また、P型MOSトランジスタMP1のゲート及びドレインは、P型MOSトランジスタMP2のゲート及び可変抵抗(第3の可変抵抗)Ra3の一方と接続されている。可変抵抗Ra3の他方は、定電圧源Viniの他方と接続されている。また、P型MOSトランジスタMP2のドレインはノード42に接続されている。ここで、P型MOSトランジスタMP1、MP2はカレントミラー回路(第2のカレントミラー回路)を構成する。また、ノード42の出力41は、図2のNANDの入力に接続されている。

【0088】

ノード42には、定電圧源Viniの電圧値と可変抵抗Ra3の抵抗値とに基づき決定された電流Iaが流れる。また、オフリーク電流Ioffが流れていない場合は、抵抗Rsの両端には電位差が生じないため、オペアンプ43の出力はLレベル信号となり、N型MOSトランジスタMN3はオンしない。この場合は、ノード44には電流が流れないため、N型MOSトランジスタMN4にも電流が流れない。よって、ノード42に流れる電流はIaのままとなる。この場合は、ノード42がHレベルとなり、オフリーク検出回路40は正常を示すHレベル信号を出力する。

【0089】

一方、抵抗Rsにオフリーク電流Ioffが流れると、抵抗Rsの両端に電位差が生じる。オペアンプ43の入力にはこの電位差が入力されるため、オペアンプ43はこの電位差に応じた信号(Hレベル信号)をN型MOSトランジスタMN3のゲートに出力する。N型MOSトランジスタMN3のゲートにHレベル信号が入力されると、ノード44には電流Ibが流れる。この電流Ibの値は、オフリーク電流Ioffの大きさに応じて変化する。ノード44に電流Ibが流れると、N型MOSトランジスタMN4にも電流Ibが流れる。このため、ノード42を流れる電流は、Ia−Ibとなる。よって、オフリーク電流Ioffの大きさが大きくなるにつれてIbも大きくなるので、ノード42に流れる電流Ia−Ibは次第に小さくなる。そして、最終的にはノード42はLレベルとなり、オフリーク検出回路40は異常を示すLレベル信号を出力する。

【0090】

例えば、オフリーク検出回路40を用いてオフリーク電流Ioffが1μA以上となった場合を検出する際は、次のように可変抵抗Ra3の抵抗値を設定する。まず、オフリーク電流Ioffが1μA流れた時に抵抗Rgの両端に生じる電位差を求める。次に、この電位差がオペアンプ43に入力された際にオペアンプ43が出力する電圧値を求める。次に、この電圧値がN型MOSトランジスタMN3のゲートに印加された場合にノード44に流れる電流Ibを求める。そして、この電流IbがN型MOSトランジスタMN4に流れた場合に、出力41がLレベル信号を出力するような電流Iaの値を決定する。そして、電流IbがN型MOSトランジスタMN4に流れていない状態で、この電流Iaがノード42に流れるように可変抵抗Ra3の抵抗値を決定する。このように可変抵抗Ra3の抵抗値を設定することで、オフリーク電流Ioffが1μAよりも小さい場合は、出力41は正常を示すHレベル信号を出力し、オフリーク電流Ioffが1μA以上の場合は、出力41は異常を示すLレベル信号を出力するように、設定することができる。

【0091】

なお、オフリーク検出回路40においても可変抵抗Ra3の設定には、図7に示す回路を用いることができる。また、図5に示したオフリーク検出回路は一例であり、パワーMOSFET2のオフリークを検出することができる回路であれば、どのような回路を用いてもよい。

【0092】

次に、本実施の形態にかかるIPD1の消費電流検出回路50の具体的な回路構成の一例について説明する。図6は、本実施の形態にかかるIPD1の消費電流検出回路50の一例を示す回路図である。消費電流検出回路50は、抵抗(第4の抵抗)Rc、可変抵抗(第2の可変抵抗)Ra4、抵抗(第5の抵抗)Re、定電圧源(第1の定電圧源)Vini、オペアンプ(第2のオペアンプ)52、コンパレータ(第3のコンパレータ)53を有する。

【0093】

抵抗Rcは、IPD1の内部GND配線(内部基準配線)55、つまり、オープン検出回路14、電流検出回路15、温度検出回路16、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、AND回路17、インバータ18、N型MOSトランジスタMN1、NAND回路19、N型MOSトランジスタMN2のLレベルとなる配線とIPD1のGND端子間に接続されており、一方がオペアンプ52の一方の入力に接続され、他方がオペアンプ52の他方の入力に接続される。オペアンプ52の出力はコンパレータ53の一方の入力に接続されている。コンパレータ53の入力の他方はノード54と接続されており、出力51は図2のNAND回路19の入力に接続されている。可変抵抗Ra4は、一方がノード54と接続され、他方が定電圧源Viniの一方と接続されている。抵抗Reは一方がノード54と接続され、他方が定電圧源Viniの他方およびGND端子と接続されている。

【0094】

ノード54には、定電圧源Viniの電圧値と可変抵抗Ra4の抵抗値と抵抗Reの抵抗値とに基づき決定された電圧が発生する。ノード54の電圧値は、基準電圧Vrefとしてコンパレータ53に入力される。この基準電圧Vrefは、可変抵抗Ra4の値を変更することで任意に変更することができる。

【0095】

通常動作時、抵抗Rcには通常レベルの消費電流Icが流れ、そのレベルに応じた電位差が抵抗Rcの両端に生じる。オペアンプ52は、抵抗Rcの両端の電位差を入力し、この電位差に応じた出力電圧をコンパレータ53の一方の入力に出力する。コンパレータ53に入力されたこの出力電圧は、可変抵抗Ra4により設定された基準電圧Vrefと比較される。通常動作時は、オペアンプ52の出力電圧は基準電圧Vrefよりも小さいため、コンパレータ53は正常を示すHレベル信号を出力する。しかし、パワーMOSFET2の特性劣化により、抵抗Rcに流れる消費電流Icが上昇すると、抵抗Rcの両端の電位差が上昇し、オペアンプ52の出力電圧は大きくなる。そして、コンパレータ53は、オペアンプ52の出力電圧が基準電圧Vref以上である場合は、異常を示すLレベル信号を出力する。

【0096】

例えば、消費電流検出回路50を用いて消費電流Icが初期特性値に基づき定められた設定値の1.1倍以上になった場合を検出する際は、次のように可変抵抗Ra4の抵抗値を設定する。まず、初期特性値に基づき定められた設定値の1.1倍の消費電流Icが流れた時に抵抗Rcの両端に生じる電位差を求める。次に、この電位差がオペアンプ52に入力された際にオペアンプ52が出力する電圧値を求める。そして、この電圧値と基準電圧Vrefが等しくなるように、可変抵抗Ra4の抵抗値を決定する。このように可変抵抗Ra4の抵抗値を設定することで、消費電流Icが初期特性値に基づき定められた設定値の1.1倍よりも小さい場合は、コンパレータ53は正常を示すHレベル信号を出力し、消費電流Icが初期特性値に基づき定められた設定値の1.1倍以上の場合は、コンパレータ53は異常を示すLレベル信号を出力するように、設定することができる。

【0097】

なお、消費電流検出回路50においても可変抵抗Ra4の設定には、図7に示す回路を用いることができる。また、図6に示した消費電流検出回路は一例であり、消費電流を検出することができる回路であれば、どのような回路を用いてもよい。

【0098】

次に、本実施の形態にかかる半導体装置の製造から異常検出までのフローを図8を用いて説明する。まず、本実施の形態にかかる半導体装置であるインテリジェントパワーデバイス(IPD1)を製造する(ステップS1)。次に、パワーMOSFETの初期特性を測定し、この初期特性値に基づき定められた設定値を記録する(ステップS2)。より具体的には、半導体チップ(またはウェハ)の状態で初期特性値(例えば、オン抵抗Ron)を測定し、これに基づいて設定値(例えば可変抵抗Ra1)となるようにトリミング抵抗をレーザ等で切断し、その後半導体チップのリードフレームへの組立・樹脂封止・リードフレームからの切断を行ない、個々のIPD1を完成する。設定値を記録する際は、例えば前述の抵抗値Ra1〜Ra4の値を設定値とする。次に、IPD1をECU(エンジンコントロールユニット)等のシステムに設置する(ステップS3)。次に、IPD1の電源をオンにする(ステップS4)。IPD1の電源がオンになると、IPD1の性能が測定される(ステップS5)。つまり、IPD1は、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50がIPD1の特性値を測定する。

【0099】

そして、ステップS5で測定したIPD1の各特性値と、初期値(初期特性値に基づき定められた設定値)とを比較する(ステップS6)。そして、ステップS5で測定した特性値に問題があるか判断される(ステップS7)。ステップS5で測定した特性値に問題がある場合は、IPD1のコントローラ(マイクロコンピュータ)へ警告(Warning)を出力する(ステップS8)。その後、コントローラから半導体装置の点検をすべき旨のメッセージを出力する(ステップS9)。つまり、コントローラであるマイクロコンピュータからドライバや自動車ディーラー等のユーザへ点検を勧めるメッセージが出力される。そして、このメッセージによりシステム(自動車)の点検が促進され自動車修理工場などで調整、修理が行われることになる(ステップS10)。そのためIPD1が破壊に至ることがなく、安全にシステムを稼動することができる。

【0100】

一方、ステップS5で測定した特性値に問題がない場合、及びステップS8においてマイクロコンピュータへ警告を出力した後、IPD1を動作させる(ステップS11)。その後、入力端子7からIPD1aをオフする制御信号が入力されれば、IPD1の電源をオフし(ステップS12)、ステップS4へと移動し、ステップS4以降の動作を繰り返す。

【0101】

以上で説明したように、本実施の形態にかかるIPD1では、IPD1の初期特性値に基づき定められた設定値と所定のタイミングにおけるIPD1の特性値とに基づき、IPD1の故障に繋がるような特性劣化を検出することができるので、IPD1の故障を未然に防ぐことができる。

【0102】

また、本実施の形態にかかるIPD1では、IPD1に故障の兆候がある場合は、マイクロコンピュータによりドライバ等のユーザへ警告を発することができるので、システム(自動車等)の動作不具合を回避することができ、その結果、システムの安全性を飛躍的に向上させることができる。

【0103】

なお、特許文献1には、パワーMOSFETのゲートにゲート抵抗を設け、パワーMOSFETがオンしているときのゲート抵抗の電圧降下を測定することで、絶縁破壊に起因したオン故障を事前に察知する技術が開示されている。また、特許文献2には、パワーMOSFETが半故障の状態でも故障判定できる故障検知回路に関する技術が開示されている。しかしながら、特許文献1、及び特許文献2にかかる技術では、本実施の形態にかかる発明のように、IPDの初期特性値(製造時の特性値)に基づき定められた設定値を記憶し、当該設定値と所定のタイミングにおけるIPDの特性値とに基づき、IPDの故障に繋がるような特性劣化を検出する点について開示されていない。これに対して本発明は、半導体チップを樹脂封止する前にIPDの初期特性値を測定し、トリミング抵抗を切断して設定値を当該半導体チップに書き込み、その後樹脂封止してIPDを完成している。これにより、IPDを使用するユーザは、改めて初期特性値を測定したり、特性劣化状態を検出するための設定値を定めたり、特性劣化検出回路を追加したりすることなく、IPDの劣化状態を知ることができる。

【0104】

実施の形態2

以下、図面を参照して発明の実施の形態2について説明する。図9は、本実施の形態にかかるIPD(半導体装置)を示すブロック図である。本実施の形態にかかるIPD1aでは、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50の出力が、それぞれAND回路70にも出力され、AND回路70の出力がAND回路11に入力されている。これ以外の部分については、実施の形態1で説明したIPD1と同一であるため、重複した説明を省略する。なお、実施の形態1で説明したIPD1と同一の構成部分には同一の符号を付している。また、図9では、図面が複雑になるため、IPD1aを構成する各要素のLレベルとなる配線と消費電流検出回路50との接続関係の記載を省略しているが、図9においても、図2の場合と同様に消費電流検出回路50は、IPD1aを構成する各要素のLレベルとなる配線、つまり内部GND配線(内部基準配線)とIPD1aのGND端子と接続されている。

【0105】

図9に示す本実施の形態にかかるIPD1aでは、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50のそれぞれに、実施の形態1で設定された初期特性値に基づき定められた設定値(第1の設定値)と、第1の設定値とは異なる値に定められた設定値(第2の設定値)とが記憶されている。そして、本実施の形態で設定された第1の設定値と、所定のタイミングにおけるIPD1aの特性値との比較結果が、AND回路19に出力される。また、第2の設定値についても同時に比較され、比較結果が、AND回路70に出力される。

【0106】

オン抵抗検出回路20は、例えば所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値がオン抵抗の初期特性値に基づき定められた設定値の1.1倍(第1の設定値)以上になった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号21を出力する。また、オン抵抗検出回路20は、例えば所定のタイミングにおけるオン抵抗の特性値がオン抵抗の初期特性値の1.5倍(第2の設定値)以上になった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号71を出力する。

【0107】

ゲートリーク検出回路30は、例えば所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、ゲートリークの初期特性値に基づき定められた設定値である1μA(第1の設定値)以上となった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号31を出力する。また、ゲートリーク検出回路30は、例えば所定のタイミングにおけるゲートリークの特性値が、ゲートリークの初期特性値に基づき定められた設定値である10μA(第2の設定値)以上となった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号72を出力する。

【0108】

オフリーク検出回路40は、例えば所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、オフリークの初期特性値に基づき定められた設定値である1μA(第1の設定値)以上となった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号21を出力する。また、オフリーク検出回路40は、例えば所定のタイミングにおけるオフリークの特性値が、オフリークの初期特性値に基づき定められた設定値である10μA(第2の設定値)以上となった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号73を出力する。

【0109】

消費電流検出回路50は、例えば所定のタイミングにおけるIPD1a消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.1倍(第1の設定値)以上になった場合に、第1の設定値に対応するレベルの異常であることを検出し、AND回路19に異常を示す信号51を出力する。また、消費電流検出回路50は、例えば所定のタイミングにおける消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.5倍(第2の設定値)以上になった場合に、第2の設定値に対応するレベルの異常であることを検出し、AND回路70に異常を示す信号74を出力する。

【0110】

すなわち、第1の設定値の条件である次の(1)から(4)の少なくとも1つ以上の条件が満たされた場合は、出力端子(Warning)8から異常を示すLレベル信号が出力される。また、第1の設定値の条件である次の(1)から(4)のいずれの条件も満たさない場合は、出力端子(Warning)8から正常を示すHレベル信号が出力される。

(1)所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値がオン抵抗の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

(2)所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、設定値である1μA以上となった場合。

(3)所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、設定値である1μA以上となった場合。

(4)所定のタイミングにおけるIPD1a消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.1倍以上になった場合。

【0111】

また、第2の設定値の条件である次の(5)から(8)の少なくとも1つ以上の条件が満たされた場合は、AND回路70はLレベル信号をAND回路11に出力する。そして、AND回路11はドライバ回路12にLレベル信号を出力するので、IPD1aは動作停止となる。一方、第2の設定値の条件である次の(5)から(8)のいずれの条件も満たさない場合は、AND回路70はHレベル信号をAND回路11に出力する。そして、AND回路11はドライバ回路12にHレベル信号を出力するので、IPD1aは動作可能となる。

(5)所定のタイミングにおけるパワーMOSFET2のオン抵抗の特性値が、オン抵抗の初期特性値に基づき定められた設定値の1.5倍以上になった場合。

(6)所定のタイミングにおけるパワーMOSFET2のゲートリークの特性値が、設定値である10μA以上となった場合。

(7)所定のタイミングにおけるパワーMOSFET2のオフリークの特性値が、設定値である10μA以上となった場合。

(8)所定のタイミングにおけるIPD1aの消費電流の特性値が、消費電流の初期特性値に基づき定められた設定値の1.5倍以上になった場合。

【0112】

なお、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50に第1の設定値と第2の設定値を検出させる場合は、例えば実施の形態1で説明した図3〜図6で説明した各検出回路をそれぞれ2つ用い、そのそれぞれについて、図7で説明した回路(設定値記憶部)を用いる。

【0113】

次に、本実施の形態にかかる半導体装置の製造から異常検出までのフローを図10を用いて説明する。まず、本実施の形態にかかる半導体装置であるインテリジェントパワーデバイス(IPD)を製造する(ステップS11)。次に、IPD1aの初期特性を測定し、この初期特性値に基づき定められた設定値(第1の設定値と第2の設定値)を記録する(ステップS12)。設定値を記録する際は、例えば前述の抵抗値Ra1〜Ra4の値を設定値とする。次に、IPD1aをECU(エンジンコントロールユニット)等のシステムに設置する(ステップS13)。次に、IPD1aの電源をオンにする(ステップS14)。IPD1aの電源がオンになると、IPD1aの性能が測定される(ステップS15)。つまり、IPD1aは、オン抵抗検出回路20、ゲートリーク検出回路30、オフリーク検出回路40、消費電流検出回路50がIPD1aの特性値を測定する。

【0114】

そして、ステップS15で測定したIPD1aの各特性値と、初期値(初期特性値に基づき定められた設定値)とを比較する(ステップS16)。そして、ステップS15で測定した特性値に問題があるか第1の設定値を基準に判断される(ステップS17)。更に、ステップS15で測定した特性値に重大な問題があるか、第2の設定値を基準に判断される(ステップS18)。ステップS15で測定した特性値が第2の設定値の許容範囲外である場合、つまり重大な問題がある場合は、IPD1aはコントローラ(マイクロコンピュータ)へ自己診断を命令し(ステップS22)、IPD1aの電源をオフにし、IPD1aを動作させない(ステップS23)。また、ステップS15で測定した特性値が第2の設定値の許容範囲内である場合、つまり重大な問題がない場合は、IPD1aのコントローラへ警告(Warning)を出力する(ステップS21)。

【0115】

ステップS22、ステップS23の後、コントローラからIPD1aの点検をすべき旨のメッセージを出力する(ステップS24)。つまり、コントローラであるマイクロコンピュータ10からドライバや自動車ディーラーなどへ点検を勧めるメッセージが出力される。そして、このメッセージによりシステム(自動車)の点検が促進され自動車修理工場などで調整、修理が行われることになる(ステップS25)。そのためIPD1aが破壊に至ることがなく、安全にシステムを稼動することができる。

【0116】

一方、ステップS15で測定した特性値に問題がない場合、及びステップS21においてコントローラへ警告を出力した後、IPD1aを動作させる(ステップS19)。その後、入力端子7からIPD1aをオフする制御信号が入力されれば、IPD1aの電源をオフし(ステップS20)、ステップS14へと移動し、ステップS14以降の動作を繰り返す。

【0117】

以上で説明したように、本実施の形態にかかるIPD1aでは、IPD1aの初期特性値に基づき定められた設定値と所定のタイミングにおけるIPD1aの特性値とに基づき、IPD1aの故障に繋がるような特性劣化を検出することができるので、IPD1aの故障を未然に防ぐことができる。

【0118】

特に、本実施の形態にかかるIPD1aでは、IPD1aの初期特性値に基づき定められた設定値を2つ設定し、IPD1aの破壊に近い設定値(第2の設定値)を満たす場合は、IPD1aの動作を停止することができるので、IPD1aの故障により負荷が暴走することを防止することができる。

【0119】

以上、本発明を上記実施形態に即して説明したが、上記実施形態の構成にのみ限定されるものではなく、本願特許請求の範囲の請求項の発明の範囲内で当業者であればなし得る各種変形、修正、組み合わせを含むことは勿論である。

【符号の説明】

【0120】

1、1a 半導体装置(IPD)

2 半導体素子(パワーMOSFET)

3 設定値記憶部

4 検出回路

5 電源端子(Vcc)

6 出力端子(OUT)

7 入力端子

8 出力端子

9 DIAG出力端子

10 コントローラ(マイクロコンピュータ)

11、17、70 AND回路

12 ドライバ回路

13 電流制限回路

14 オープン検出回路

15 電流検出回路

16 温度検出回路

18 インバータ

19 NAND回路

20 オン抵抗検出回路

30 ゲートリーク検出回路

40 オフリーク検出回路

50 消費電流検出回路

【特許請求の範囲】

【請求項1】

半導体装置の初期特性値に基づき定められた設定値を記憶する設定値記憶部と、

所定のタイミングにおける前記半導体装置の特性値と前記設定値記憶部に記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する検出回路と、

を備える半導体装置。

【請求項2】

前記検出回路は、前記半導体素子のオン抵抗を検出するオン抵抗検出回路である、請求項1に記載の半導体装置。

【請求項3】

前記オン抵抗検出回路は、

一方が前記半導体素子のソースと第1のノードにおいて接続され、他方が第2のノードと接続された第1の抵抗と、

一方が前記半導体素子のドレインと接続され、他方が第3のノードと接続された第1の可変抵抗と、

一方が前記第3のノードと接続され、他方が前記第2のノードと接続された第2の抵抗と、

前記第1のノードの電圧値と前記第3のノードの電圧値とを入力し、当該第1のノードの電圧値と当該第3のノードの電圧値との電位差に基づき信号を出力する第1のコンパレータと、を備える、請求項2に記載の半導体装置。

【請求項4】

前記検出回路は、前記半導体素子のゲートリークを検出するゲートリーク検出回路である、請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記ゲートリーク検出回路は、

前記半導体素子のゲートに接続された第3の抵抗と、

前記第3の抵抗の両端に生じる電位差を入力し、当該電位差に基づき電圧信号を出力する第1のオペアンプと、

前記第1のオペアンプの電圧信号と基準電圧とを入力し、当該第1のオペアンプの電圧信号と前記基準電圧との比較結果に基づき信号を出力する第2のコンパレータと、を備える、請求項4に記載の半導体装置。

【請求項6】

前記検出回路は、前記半導体装置の消費電流を検出する消費電流検出回路である、請求項1乃至5のいずれか一項に記載の半導体装置。

【請求項7】

前記消費電流検出回路は、

前記半導体装置の内部基準配線に接続された第4の抵抗と、

前記第4の抵抗の両端に生じる電位差を入力し、当該電位差に基づき電圧信号を出力する第2のオペアンプと、

前記第2のオペアンプの電圧信号と基準電圧とを入力し、当該第2のオペアンプの電圧信号と前記基準電圧との比較結果に基づき信号を出力する第3のコンパレータと、を備える、請求項6に記載の半導体装置。

【請求項8】

前記基準電圧は、第1の定電圧源と、当該第1の定電圧源の電圧を分割する第2の可変抵抗および第5の抵抗と、を有する回路を用いて設定される、請求項5または7に記載の半導体装置。

【請求項9】

前記検出回路は、前記半導体素子のオフリークを検出するオフリーク検出回路である、請求項1乃至8のいずれか一項に記載の半導体装置。

【請求項10】

前記オフリーク検出回路は、

前記半導体素子のソースに接続された第6の抵抗と、

前記第6の抵抗の両端に生じる電位差を入力し、当該電位差に基づき信号を出力する第3のオペアンプと、

前記第3のオペアンプの出力がゲートに接続され、ソースが第4のノードに接続された第1のトランジスタと、

前記第4のノードに第1の電流経路が接続され、基準電流が流れる第5のノードに第2の電流経路が接続された第1のカレントミラー回路と、を備える、請求項9に記載の半導体装置。

【請求項11】

前記基準電流は、第2の定電圧源および第3の可変抵抗が接続された第3の電流経路と、前記第2の電流経路が接続された第2のカレントミラー回路を用いて設定される、請求項10に記載の半導体装置。

【請求項12】

前記第1乃至3の可変抵抗は、

直列に接続された複数の抵抗と、

前記複数の抵抗に対応して設けられ、当該複数の抵抗のそれぞれの両端にソース・ドレインが接続された複数のP型トランジスタと、

前記複数のP型トランジスタのゲートのそれぞれに接続された定電流源と、

前記複数のP型トランジスタのゲートのそれぞれと基準電源との間に設けられたトリミング抵抗と、を備え、

前記トリミング抵抗を切断することで抵抗値を設定する、請求項2乃至11に記載の半導体装置。

【請求項13】

前記設定値記憶部には、前記半導体装置の初期特性値に基づき定められた第1の設定値と第2の設定値とが記憶され、

前記検出回路は、所定のタイミングにおける前記半導体装置の特性値と前記第1の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき警報を出力し、

所定のタイミングにおける前記半導体装置の特性値と前記第2の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき前記半導体装置の動作を停止する、請求項1乃至12のいずれか一項に記載の半導体装置。

【請求項14】

前記所定のタイミングは、前記半導体装置に電源が投入されたタイミング、前記半導体装置の入力端子に制御信号が入力されたタイミング、前記半導体装置を制御するコントローラから前記半導体装置へ前記半導体装置の特性劣化を検出する旨の命令信号が入力されたタイミング、前記半導体装置の稼働中における一定周期毎のタイミング、である請求項1乃至13のいずれか一項に記載の半導体装置。

【請求項15】

半導体装置の特性劣化を検出する方法であって、

前記半導体装置の初期特性値に基づき定められた設定値を記憶し、

所定のタイミングにおける前記半導体装置の特性値と前記記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する、半導体装置の特性劣化検出方法。

【請求項16】

前記半導体素子のオン抵抗、ゲートリーク、オフリーク、および前記半導体装置の消費電流のうちの少なくとも1つに基づき前記半導体装置の特性劣化を検出する、請求項15に記載の半導体装置の特性劣化検出方法。

【請求項17】

前記半導体装置の初期特性値に基づき定められた第1の設定値と第2の設定値とを記憶し、

所定のタイミングにおける前記半導体装置の特性値と前記第1の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき警報を出力し、

所定のタイミングにおける前記半導体装置の特性値と前記第2の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき前記半導体装置の動作を停止する、請求項15または16に記載の半導体装置の特性劣化検出方法。

【請求項1】

半導体装置の初期特性値に基づき定められた設定値を記憶する設定値記憶部と、

所定のタイミングにおける前記半導体装置の特性値と前記設定値記憶部に記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する検出回路と、

を備える半導体装置。

【請求項2】

前記検出回路は、前記半導体素子のオン抵抗を検出するオン抵抗検出回路である、請求項1に記載の半導体装置。

【請求項3】

前記オン抵抗検出回路は、

一方が前記半導体素子のソースと第1のノードにおいて接続され、他方が第2のノードと接続された第1の抵抗と、

一方が前記半導体素子のドレインと接続され、他方が第3のノードと接続された第1の可変抵抗と、

一方が前記第3のノードと接続され、他方が前記第2のノードと接続された第2の抵抗と、

前記第1のノードの電圧値と前記第3のノードの電圧値とを入力し、当該第1のノードの電圧値と当該第3のノードの電圧値との電位差に基づき信号を出力する第1のコンパレータと、を備える、請求項2に記載の半導体装置。

【請求項4】

前記検出回路は、前記半導体素子のゲートリークを検出するゲートリーク検出回路である、請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記ゲートリーク検出回路は、

前記半導体素子のゲートに接続された第3の抵抗と、

前記第3の抵抗の両端に生じる電位差を入力し、当該電位差に基づき電圧信号を出力する第1のオペアンプと、

前記第1のオペアンプの電圧信号と基準電圧とを入力し、当該第1のオペアンプの電圧信号と前記基準電圧との比較結果に基づき信号を出力する第2のコンパレータと、を備える、請求項4に記載の半導体装置。

【請求項6】

前記検出回路は、前記半導体装置の消費電流を検出する消費電流検出回路である、請求項1乃至5のいずれか一項に記載の半導体装置。

【請求項7】

前記消費電流検出回路は、

前記半導体装置の内部基準配線に接続された第4の抵抗と、

前記第4の抵抗の両端に生じる電位差を入力し、当該電位差に基づき電圧信号を出力する第2のオペアンプと、

前記第2のオペアンプの電圧信号と基準電圧とを入力し、当該第2のオペアンプの電圧信号と前記基準電圧との比較結果に基づき信号を出力する第3のコンパレータと、を備える、請求項6に記載の半導体装置。

【請求項8】

前記基準電圧は、第1の定電圧源と、当該第1の定電圧源の電圧を分割する第2の可変抵抗および第5の抵抗と、を有する回路を用いて設定される、請求項5または7に記載の半導体装置。

【請求項9】

前記検出回路は、前記半導体素子のオフリークを検出するオフリーク検出回路である、請求項1乃至8のいずれか一項に記載の半導体装置。

【請求項10】

前記オフリーク検出回路は、

前記半導体素子のソースに接続された第6の抵抗と、

前記第6の抵抗の両端に生じる電位差を入力し、当該電位差に基づき信号を出力する第3のオペアンプと、

前記第3のオペアンプの出力がゲートに接続され、ソースが第4のノードに接続された第1のトランジスタと、

前記第4のノードに第1の電流経路が接続され、基準電流が流れる第5のノードに第2の電流経路が接続された第1のカレントミラー回路と、を備える、請求項9に記載の半導体装置。

【請求項11】

前記基準電流は、第2の定電圧源および第3の可変抵抗が接続された第3の電流経路と、前記第2の電流経路が接続された第2のカレントミラー回路を用いて設定される、請求項10に記載の半導体装置。

【請求項12】

前記第1乃至3の可変抵抗は、

直列に接続された複数の抵抗と、

前記複数の抵抗に対応して設けられ、当該複数の抵抗のそれぞれの両端にソース・ドレインが接続された複数のP型トランジスタと、

前記複数のP型トランジスタのゲートのそれぞれに接続された定電流源と、

前記複数のP型トランジスタのゲートのそれぞれと基準電源との間に設けられたトリミング抵抗と、を備え、

前記トリミング抵抗を切断することで抵抗値を設定する、請求項2乃至11に記載の半導体装置。

【請求項13】

前記設定値記憶部には、前記半導体装置の初期特性値に基づき定められた第1の設定値と第2の設定値とが記憶され、

前記検出回路は、所定のタイミングにおける前記半導体装置の特性値と前記第1の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき警報を出力し、

所定のタイミングにおける前記半導体装置の特性値と前記第2の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき前記半導体装置の動作を停止する、請求項1乃至12のいずれか一項に記載の半導体装置。

【請求項14】

前記所定のタイミングは、前記半導体装置に電源が投入されたタイミング、前記半導体装置の入力端子に制御信号が入力されたタイミング、前記半導体装置を制御するコントローラから前記半導体装置へ前記半導体装置の特性劣化を検出する旨の命令信号が入力されたタイミング、前記半導体装置の稼働中における一定周期毎のタイミング、である請求項1乃至13のいずれか一項に記載の半導体装置。

【請求項15】

半導体装置の特性劣化を検出する方法であって、

前記半導体装置の初期特性値に基づき定められた設定値を記憶し、

所定のタイミングにおける前記半導体装置の特性値と前記記憶された設定値とに基づき、前記半導体装置の特性劣化を検出する、半導体装置の特性劣化検出方法。

【請求項16】

前記半導体素子のオン抵抗、ゲートリーク、オフリーク、および前記半導体装置の消費電流のうちの少なくとも1つに基づき前記半導体装置の特性劣化を検出する、請求項15に記載の半導体装置の特性劣化検出方法。

【請求項17】

前記半導体装置の初期特性値に基づき定められた第1の設定値と第2の設定値とを記憶し、

所定のタイミングにおける前記半導体装置の特性値と前記第1の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき警報を出力し、

所定のタイミングにおける前記半導体装置の特性値と前記第2の設定値とに基づき前記半導体装置の特性劣化を検出し、当該検出結果に基づき前記半導体装置の動作を停止する、請求項15または16に記載の半導体装置の特性劣化検出方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【公開番号】特開2011−71174(P2011−71174A)

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願番号】特願2009−218824(P2009−218824)

【出願日】平成21年9月24日(2009.9.24)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願日】平成21年9月24日(2009.9.24)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]