Fターム[5J056CC00]の内容

論理回路 (30,215) | 構成要素(回路) (5,601)

Fターム[5J056CC00]の下位に属するFターム

定電流源 (480)

ミラー回路、カレントミラー回路 (296)

電源回路 (715)

遅延回路 (349)

フィルタ回路 (82)

積分回路 (27)

微分回路 (11)

比較器 (432)

オペアンプ (171)

シュミット回路 (34)

クランプ回路 (62)

リミッタ回路 (17)

双安定回路(フリップフロップ、ラッチ) (577)

単安定回路 (17)

非安定回路、発振回路 (126)

カウンタ (157)

シフトレジスタ (106)

プリチャージ回路 (44)

ディスチャージ回路 (10)

レベルシフト回路 (574)

ダーリントン (1)

エミッタホロワ (6)

オープンコレクタ (3)

ソースホロワ (26)

オープンドレイン (10)

ドット論理、ワイヤード論理 (8)

表示回路 (13)

昇圧回路(ブートストラップ) (120)

ポンプ回路 (36)

Fターム[5J056CC00]に分類される特許

81 - 100 / 1,091

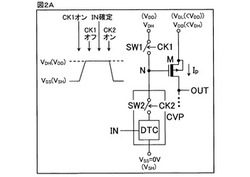

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

磁気レベルシフタ

【課題】多チャンネル化しても形成面積の増大を抑えることができる磁気レベルシフタを提供する。

【解決手段】レベルシフタは、入力信号が印加される磁界発生用配線112と、磁界発生用配線112が発生した磁界に対応した値をとる検出信号を出力する検出用磁気抵抗効果素子11と、一定の値をとる参照信号を出力する参照用磁気抵抗効果素子21,31を備える。当該レベルシフタは、検出信号と参照電圧の差に基づいて出力信号を生成する。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

半導体装置およびその制御方法

【課題】半導体装置のデータ入力回路における消費電力を削減すること。

【解決手段】半導体装置は、クロック信号の立ち上がりエッジおよび立ち下がりエッジの少なくともいずれか一方の近傍の期間において活性状態となる制御信号を生成して出力する制御信号生成回路と、制御信号が活性状態である期間においてデータ信号を受信可能な活性状態となり、それ以外の期間において非活性状態となるデータ入力回路と、を備えている。

(もっと読む)

半導体デバイス回路

【課題】MTCMOS回路を用いた半導体デバイス回路において、アクセススピードを損なわず、スタンバイ電流が少なく、スタンバイ状態からの復帰が早い半導体デバイス回路を提供する。

【解決手段】第1のPMOSFETと第1のNMOSFETとを含む機能回路を備えた半導体デバイス回路において、アクティブモード時に第1のPMOSFETを電源電圧源に接続し、スタンバイモード時に電源電圧源に接続しないように制御する第2のPMOSFETと、アクティブモード時に第1のNMOSFETを接地側電圧源に接続し、スタンバイモード時に接地側電圧源に接続しないように制御する第2のNMOSFETと、電源電圧源に接続されかつ第1のPMOSFETに並列に接続されその出力信号を保持する第3のPMOSFETと、接地側電圧源に接続されかつ第1のNMOSFETに並列に接続されその出力信号を保持する第3のNMOSFETとを備えた。

(もっと読む)

半導体集積回路

【課題】電源遮断時に、電源遮断対象ブロックへの電源配線を有効に活用することのできる半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1の電源パッドと、第2の電源パッドと、第1の電源パッドに接続された第1の電源配線と、第2の電源パッドに接続された第2の電源配線と、を備え、第1のスイッチを介して第1の電源配線に接続される電源遮断対象ブロックと、第2の電源配線に接続される常時電源供給対象ブロックと、第1の電源配線と第2の電源配線との間に接続された第2のスイッチと、を備える。

(もっと読む)

回路装置及びシステム

【課題】出力モードを切り換えることにより効率的な通信ができる回路装置及びシステム等を提供すること。

【解決手段】回路装置100は、バスHBSを介してホスト装置200に信号を出力する出力回路110と、出力回路110を制御する出力制御回路120とを含む。出力回路110は、出力ノードNQと第1の電源ノードVSSとの間に設けられる第1の導電型のトランジスターTNと、出力ノードNQと第2の電源ノードVDDとの間に設けられる第2の導電型のトランジスターTPとを含む。出力制御回路120は、第1の出力モードでは、第1の導電型のトランジスターTN及び第2の導電型のトランジスターTPのいずれか一方をオフにし、他方をオン・オフする制御を行い、第2の出力モードでは、第1の導電型のトランジスターTN及び第2の導電型のトランジスターTPを排他的にオン・オフする制御を行う。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

切替回路及び受信回路

【課題】2つのクロック信号を切り替えて出力する切替回路において、出力信号のデューティ比を、入力されるクロック信号のデューティ比に保つこと。

【解決手段】切替回路100は、制御信号CONTに応じて、入力信号IN1,IN2を切り替えて出力信号OUTとして出力する。具体的には、制御信号CONTが「Lレベル」のときには、クロックドインバーターX2が動作し、信号IN1が信号OUTとして出力され、制御信号CONTが「Hレベル」のときには、クロックドインバーターX4が動作し、信号IN2が信号OUTとして出力される。

(もっと読む)

信号変換装置、波形測定装置および半導体試験装置

【課題】シングルエンド信号および差動信号を入力してシングルエンド信号を出力するときに、広帯域でノイズや歪みが少ない高品質なシングルエンド信号を出力することを目的とする。

【解決手段】信号変換装置3にパルストランス12を用い、シングルエンド信号を入力したときには、パルストランス12の1次入力側と2次入力側とのうちシングルエンド信号を入力した入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続し、差動信号を入力したときには、1次入力側および2次入力側との両方の入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続する制御を行っている。

(もっと読む)

モードコントロール回路

【課題】 パワーダウンモードを含む複数の動作モードを有する半導体集積回路において、モード切り換えを行うモードコントロール回路の消費電力を少なくする。

【解決手段】 制御電圧VCに基づきパワーダウンを設定するか解除するかの判定を行う回路としてオフセット付き電圧比較器30Aを設けた。制御電圧VCがオフセット電圧V0よりも低く、オフセット付き電圧比較器30Aがパワーダウン解除信号MD0を非アクティブレベルとしている間は、基準電圧発生回路10Aを動作させず、制御電圧VCとの比較に用いる基準電圧V1〜V3を出力させない。制御電圧VCがオフセット電圧V0を越えて上昇し、パワーダウン解除信号MD0がアクティブレベルになったとき、基準電圧発生回路10Aを動作させ、基準電圧V1〜V3と制御電圧VCとの比較によるモード切り換えを行わせる。

(もっと読む)

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

電圧レベルシフト回路および半導体装置

【課題】電圧レベルシフト回路において、入力信号の信号レベルによる応答特性の差違を抑制する。

【解決手段】電圧レベルシフト回路は、入力信号とは異なる電圧振幅を有する出力信号VOUTを生成する。インバータINV2は、入力信号にしたがってVSS〜VDDIの範囲の電圧V1を生成する。インバータINV3は、入力信号にしたがってVSS〜VPERIの範囲の電圧V2を生成する。インバータINV4は、V1およびV2にしたがって出力信号VOUTを生成する。

(もっと読む)

半導体装置

【課題】外部電圧が変動したときにも半導体装置の動作安定性を維持する。

【解決手段】入力信号判定部116は、第1電流源122から供給される電源電位によって動作する。入力信号判定部116は、入力信号VINと参照電位Vrefを比較する。比較結果はインバータINV1により反転され、出力信号V0となる。電源センサ回路120は、第1の電源ラインVDDIの電位を監視する。外部電位VDDIが基準電位VXよりも低くなると、電源センサ回路120は第2電流源124をオンする。第2電流源124がオンされると、判定部126には、第1電流源122に加えて第2電流源124からも動作電流が供給される。

(もっと読む)

信号駆動回路

【課題】DCオフセットを低減し、正確な出力アナログ電圧値を得る信号駆動回路を提供する。

【解決手段】信号駆動回路は、デジタルデータに基づいて第一アナログ電圧を発生するデジタル/アナログコンバータ(DAC)と、第一アナログ電圧に基づいてアナログバッファによって第二アナログ電圧をロードに選択的に出力、またはアナログバッファを通過することなしに第一アナログ電圧をロードに選択的に出力する出力回路とを含む。

(もっと読む)

データ伝送回路及び伝送方法並びにデータ伝送回路を備えるメモリ装置

【課題】データを伝送するデータ伝送回路を提供すること。

【解決手段】データを第1のラインに駆動する第1のドライバと、前記第1のラインに伝達されたデータのパターンを変更するパターン変更部と、該パターン変更部によってパターンが変更されたデータを第2のラインに駆動する第2のドライバと、前記第2のラインに伝達されたデータのパターンを元通りに復元するパターン復元部とを備えることを特徴とする。

(もっと読む)

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

半導体集積回路および高周波モジュール

【課題】出力波形のリップルを低減可能な半導体集積回路を提供する。

【解決手段】例えば、高周波スイッチ回路RFSWと、そのオン・オフを制御するスイッチ制御回路SWCTLを備え、SWCTLは、2個のダウンコンバータ回路VGEN1,VGEN2と、レベルシフト回路LS[1]〜LS[4]を備える。各LS[n]は、レベルシフト段LSSG[n]とその後段に接続された出力段OTSG[n]を持ち、RFSWは、OTSG[n]からの制御信号OUT[n]によって制御される。LSSG[n]は、VGEN1からの負の電源電圧(−VSS1)を用いて動作し、OTSG[n]は、VGEN2からの負の電源電圧(−VSS2)を用いて動作する。−VSS1では、LSSG[n]のレベルシフト動作に伴いリップルが生じ得るが、−VSS2ではOTSG[n]の動作がスイッチング動作であるためリップルが生じ難い。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

81 - 100 / 1,091

[ Back to top ]