Fターム[5J056CC00]の内容

論理回路 (30,215) | 構成要素(回路) (5,601)

Fターム[5J056CC00]の下位に属するFターム

定電流源 (480)

ミラー回路、カレントミラー回路 (296)

電源回路 (715)

遅延回路 (349)

フィルタ回路 (82)

積分回路 (27)

微分回路 (11)

比較器 (432)

オペアンプ (171)

シュミット回路 (34)

クランプ回路 (62)

リミッタ回路 (17)

双安定回路(フリップフロップ、ラッチ) (577)

単安定回路 (17)

非安定回路、発振回路 (126)

カウンタ (157)

シフトレジスタ (106)

プリチャージ回路 (44)

ディスチャージ回路 (10)

レベルシフト回路 (574)

ダーリントン (1)

エミッタホロワ (6)

オープンコレクタ (3)

ソースホロワ (26)

オープンドレイン (10)

ドット論理、ワイヤード論理 (8)

表示回路 (13)

昇圧回路(ブートストラップ) (120)

ポンプ回路 (36)

Fターム[5J056CC00]に分類される特許

121 - 140 / 1,091

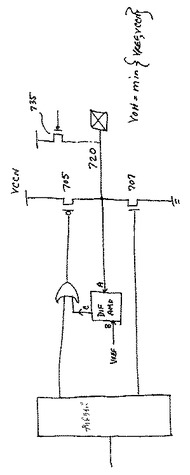

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

レベル変換回路

【課題】第1及び第2入力信号の電圧レベルが変化する範囲に拘わらず、常時、適切なレベルで振幅する出力信号を出力することが可能なレベル変換回路を提供する。

【解決手段】N型トランジスタ21、22を入力差動対として有し、外部から入力される第1及び第2入力信号IN1、IN2をN型トランジスタ21、22のゲートに受ける第1差動増幅部2と、P型トランジスタ31、32を入力差動対として有し、第1及び第2入力信号IN1、IN2をP型トランジスタ31、32のゲートに受ける第2差動増幅部3と、第1及び第2入力信号IN1、IN2の電圧レベルを所定の基準電位VREFと比較し、各々の電圧レベルが基準電位VREFよりも高いか否かを判定する入力判定部4と、入力判定部4の判定結果に応じて第1及び第2差動増幅部2、3のいずれか一方の出力を選択する出力選択部5とを備えたレベル変換回路1。

(もっと読む)

半導体集積回路装置

【課題】

複数の電源を有する半導体集積回路装置において、複数の電源が半導体集積回路装置の外部、内部であるに関わらず、それら電源の立ち上げ順序に依存せずに各回路のオン状態を一意に制御するためのシーケンス制御信号を生成することができる半導体集積回路装置を提供する。

【解決手段】

半導体集積回路装置100は、第1電源VCC1で動作する第1電子回路120と、第2電源VCC2で動作する第2電子回路140と、第1電源VCC1および第2電源VCC2の電圧の大きさを所定の検知レベルで検出し、第1電子回路120のオン動作を制御するためのシーケンス制御信号PS1、および第2電子回路140の所期化を行うためのパワーオンリセット信号PORを生成するシーケンス制御回路180を備える。

(もっと読む)

ディプレッション型FET用バイアス印加回路

【課題】単電源駆動の構成において常に所望のバイアス条件が得られると共に、生産性の向上、コストの低減を図ることができるようにする。

【解決手段】N−chディプレッション型FET1を単一の正電源3で駆動する構成において、FET1のソースと接地との間に、ソース電圧を制御するための第1(NPN)トランジスタQ1 が接続され、この第1トランジスタQ1 のベースには、このベースにFET1のドレイン電流の大きさに応じた調整用電流を供給するための第2(PNP)トランジスタQ2 が接続される。また、FET1のドレインと正電源3との間に、ドレイン電流検出用の抵抗R3が接続され、上記第1トランジスタQ1 によりFET1のソース電圧を制御することで、FET1のドレイン電流が常に一定となるように自動調整を行う。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

レベルシフタ回路及び半導体装置

【課題】電源電圧の低電圧化に対応可能とし高速化を実現するレベルシフタ回路の提供。

【解決手段】第1の電源と基準電源に対応した振幅の入力信号に応答してオン・オフが制御される第1のトランジスタと、入力信号の相補信号に応答してオン・オフが制御される第2のトランジスタと、縦積み接続された第3、第4、第5、第6のトランジスタと、を備え、第1及び第2のトランジスタは第1導電型で、第3乃至第6のトランジスタは第2導電型で、第1、第3、第5のトランジスタは、基準電源と、第1の電源電圧と異なる電圧の第2の電源との間に接続され、第2、第4、第6のトランジスタは、基準電源と、第2の電源との間に接続され、第1のノードは、第4トランジスタの入力端子と第5のトランジスタの入力端子に共通に接続され、第2のノードは、第3トランジスタの入力端子と第6のトランジスタの入力端子に共通に接続する。

(もっと読む)

半導体装置

【課題】同一電源系統に接続された複数の主バッファの動作台数の変化により生じる半導体装置の出力のばらつきを抑制すること。

【解決手段】本発明の一態様に係る半導体装置は、入力されるデータに応じて複数の信号線を駆動する、複数の主バッファを備える主バッファ回路2と、主バッファと同数のダミーバッファを備えるダミーバッファ回路5と、主バッファ回路2及びダミーバッファ回路5に接続された電源と、主バッファ回路2が接続された主バッファ配線と、ダミーバッファ回路5に接続され、主バッファ配線と略同一の負荷を有するダミーバッファ配線と、主バッファ回路の複数の主バッファのスイッチング状況を検知するスイッチング検出回路3と、スイッチング検知結果に基づいて、ダミーバッファのスイッチング数を制御するダミーバッファスイッチング回路4とを備える。

(もっと読む)

半導体メモリのデータ出力回路及びその制御方法

【課題】カップリングノイズを減少させることができる半導体メモリのデータ出力回路およびその制御方法を提供すること。

【解決手段】複数のグローバルラインと、複数のデータを互いに異なるタイミングで複数のグローバルラインに出力するように構成されたセンスアンプブロックと、複数のグローバルラインを介して伝送された複数のデータを互いに異なるタイミングでラッチするように構成されたパイプラッチブロックと、アドレス信号を用いてセンスアンプブロックの出力タイミングとパイプラッチブロックのラッチタイミングとを制御するように構成された制御部とを備えることを特徴とする。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

半導体集積回路、動作電圧制御方法

【課題】動作電圧を制御してプロセスばらつきを補償する条件で設計した半導体集積回路の起動問題を解消する。

【解決手段】本発明による半導体集積回路は、プロセスばらつきに対して第1のコーナー条件で設計された第1回路部1と、第1の条件より狭い第2のコーナー条件で設計された第2回路部2と、第1回路部1における遅延量に応じて、第1回路部1及び第2回路部2に供給する動作電圧を変更し、動作電圧の変化による遅延特性が第2コーナー条件における遅延特性に適合した場合、第2回路2を起動する制御部12とを具備する。

(もっと読む)

半導体装置

【課題】省電力化および信頼性の向上、または小面積化を実現可能な半導体装置を提供する。

【解決手段】電源遮断が行われない内部電源Vint0と電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWと、電源遮断が行われる内部電源Vint1の電圧を判定する内部電圧判定回路VINTDETを設ける。電源遮断が行われる内部電源Vint1は、外部電源Vextからレギュレータ回路VREGを用いて生成する。Vint1の電源遮断時は、SWをオフにし、VREGのオフおよびVREG出力の接地電位GNDへのショートを行い、Vint1の電源復帰時は、VREGのオンおよびショートの解除を行い、上昇したVint1の電圧をVINTDETで判定した上で回路ブロックBLK1の動作開始およびSWのオンを行う。

(もっと読む)

レベルシフト回路

【課題】レベル変換における動作範囲を広くする。

【解決手段】第1の電位(VDD1)の波高値を有する入力パルス信号(VIN)を入力するCMOSインバータ回路(P1、N1)と、第1の電位よりも高電位となる第2の電位(VDD2)の電源で動作し、一端(ND1)をCMOSインバータ回路の出力端に接続し、他端から第2の電位の波高値を有し入力パルス信号と同相の出力パルス信号(VOUT)を出力するラッチ回路(INV1、P3)と、第1の電位以上かつ第2の電位未満の電源供給をCMOSインバータ回路に対して行う電源供給回路(P2、INV2)と、を備え、電源供給回路は、入力パルス信号が少なくとも接地レベルとなる場合に電源供給を制限するように機能する。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

波形発生装置および半導体試験装置

【課題】複数のタイミングエッジ発生回路のそれぞれのタイミング補正を行うときに、タイミング補正を行うための設定内容を単純化させることを目的とする。

【解決手段】波形を発生する波形発生装置1であって、波形のタイミングを規定するタイミングエッジデータTEDを生成する複数のタイミングエッジデータ生成部3と、タイミングエッジデータTEDを入力して、この入力したタイミングエッジデータTEDのタイミングでタイミングエッジTEを発生する複数のタイミングエッジ発生部4と、タイミングエッジに基づいて波形を発生するフリップフロップ7と、タイミングエッジデータTEDの出力先を任意のタイミングエッジ発生部4に変更可能にした出力変更部14と、を備えている。

(もっと読む)

電源変動緩和回路を有する集積回路

【課題】

内部回路の一部の回路が起動または停止したときに内部電源電圧の変動が緩和されるようにした集積回路を提供する。

【解決手段】

電源が供給される集積回路において,電源が供給され内部電源を内部に供給する電源配線と,内部電源を供給される第1及び第2の内部回路と,第2の内部回路を非動作状態から動作状態に制御するイネーブル信号を第2の内部回路に供給するイネーブル信号供給回路とを有し,イネーブル信号供給回路は,イネーブル信号が非動作状態から動作状態に変化したときに動作状態の期間を間欠的に発生する調整イネーブル信号を生成し第2の内部回路に供給する。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

レベルシフト回路

【課題】変換する電位差が大きくても、小規模な回路で、高速に、低電圧から高電圧へ信号レベルを変換することのできるレベルシフト回路を提供する。

【解決手段】低電圧電源電圧VDDLで動作する低電圧部100からは、入力信号Sinと同相の同相信号Sおよび逆相の逆相信号SNが出力され、能動バイアス制御部1は、入力された逆相信号SNの信号レベルに応じて、出力するバイアス信号VMの電位を、高電圧電源電圧VDDHに近い電位、または接地電位GNDに近い電位に、能動的に制御し、出力部2は、高電圧電源線VDDHと反転出力端VQとの間の導通が同相信号Sおよびバイアス信号VMにより制御され、接地電位電源線GNDと反転出力端VQとの間の導通が同相信号Sにより制御され、反転出力端VQの信号の極性がインバータINV1により反転される。

(もっと読む)

出力バッファ回路

【課題】出力遅延を短縮できる出力バッファ回路を提供する。

【解決手段】信号PenがLレベルからHレベルに切り替わり信号NenがHレベルからLレベルに切り替わった直後において、定電流源Is1が追従しきれずまた切り替わっていない場合には、ノードPは未だHレベルのままであるので、ノードOUTはLレベルのままである。この状態で、切り替え前にHレベルのノードNに接続されていたノードAは、切り替えによりHレベルのノードPへ接続される。これと同時に、インバータinv3の出力部がHレベルからLレベルに切り替わっているので、キャパシタC2を介して、ノードAもHレベルからLレベルに切り替えられる。このとき、ノードPの電位はノードAと等しくなるまで引き下げられ、Lレベルへ遷移する。

(もっと読む)

121 - 140 / 1,091

[ Back to top ]