Fターム[5J056CC00]の内容

論理回路 (30,215) | 構成要素(回路) (5,601)

Fターム[5J056CC00]の下位に属するFターム

定電流源 (480)

ミラー回路、カレントミラー回路 (296)

電源回路 (715)

遅延回路 (349)

フィルタ回路 (82)

積分回路 (27)

微分回路 (11)

比較器 (432)

オペアンプ (171)

シュミット回路 (34)

クランプ回路 (62)

リミッタ回路 (17)

双安定回路(フリップフロップ、ラッチ) (577)

単安定回路 (17)

非安定回路、発振回路 (126)

カウンタ (157)

シフトレジスタ (106)

プリチャージ回路 (44)

ディスチャージ回路 (10)

レベルシフト回路 (574)

ダーリントン (1)

エミッタホロワ (6)

オープンコレクタ (3)

ソースホロワ (26)

オープンドレイン (10)

ドット論理、ワイヤード論理 (8)

表示回路 (13)

昇圧回路(ブートストラップ) (120)

ポンプ回路 (36)

Fターム[5J056CC00]に分類される特許

41 - 60 / 1,091

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr1Cで構成されるインバータ回路1において、トランジスタT2のゲートと高電圧線L3との間に接続されたトランジスタT4,T5と、トランジスタT2のゲートと低電圧線L1との間に接続されたトランジスタT3とのオンオフ動作により、全期間に渡ってトランジスタT1,T2が同時にオンしないようになっている。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

タイミング制御回路、タイミング制御方法、及びシステム

【課題】タイミングマージンの減少を抑制すること。

【解決手段】システム装置21に形成された制御回路36は、可変容量35の容量値を制御し、トレーニング回路45にタイミングトレーニングを実行させる。トレーニング回路45は、メモリ12がデータDQに基づく正常なデータを書き込むことができる設定値の最大値と最小値を出力する。制御回路36は、その最大値及び最小値に基づいてデータDQのウインドウ幅を算出し、より大きなウインドウ幅に対応する容量値を可変容量35に設定する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

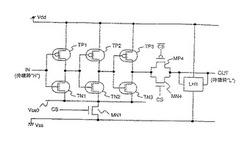

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

差動出力バッファ

【課題】送信状態とスタンバイ状態との間の遷移時間の増大を抑制しつつ、電流の変動を低減する。

【解決手段】メインドライバ1は、差動信号PREP、PRENのレベル変換を行い、バイパス回路2は、メインドライバ1の動作状態とスタンバイ状態との間の遷移時に高電源電位VDDから低電源電位VSSに流れる電流I5の変化量が一定の範囲内に収まるようにメインドライバ1に流れる電流I5をバイパスさせる。

(もっと読む)

不揮発性メモリ用の高速ファンアウトシステムアーキテクチャおよび入出力回路

【課題】 不揮発性メモリ用の高速ファンアウトシステムアーキテクチャおよび入出力回路を提供する。

【解決手段】 さまざまな実施形態において、複数の不揮発性メモリデバイス、例えばNANDフラッシュメモリデバイスが、ファンアウト構造でホストコントローラデバイスに接続され得る。ファンアウト構造によると、各メモリデバイスは読み出し動作および/または書き込み動作を同時に実行できる。各不揮発性メモリデバイスは、高速入力回路および高速出力回路を有し得るので、メモリとの間のデータ転送は、フラッシュメモリ読み書きインターフェースの速度に制限されない。

(もっと読む)

半導体装置

【課題】リーク電流を従来よりも抑えること。

【解決手段】本発明の半導体装置1は、外部から信号を供給可能な入力端子10と、内部回路30と、制御部40と、バッファ回路20とを具備している。制御部40は、起動時から所定時間が経過するまでの間にマスク解除信号MASK“H”を出力する。バッファ回路20は、入力端子10に供給される電圧VDD又は電圧GNDを表す信号をマスク解除信号MASK“H”に応じて内部回路30に出力する。本発明の半導体装置1では、外部から入力端子10に信号が供給されているときにノイズが発生しても、バッファ回路20が入力端子10から内部回路30への伝送を有効にする時間以外は無効にしている。このため、マスク回路26によるバッファ回路20と内部回路30との切り離しにより、内部回路30への貫通電流を防止することができる。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

半導体装置

【課題】 ゲート−ソース逆バイアス駆動の動作原理を定量化し、MOSTのしきい電圧と動作電圧の関係を明らかにすることにより、逆バイアス駆動の原理を活用した複数のMOSTの組み合わせを用いて、動作電圧1V以下の高速低電圧動作を可能にする。

【解決手段】 低VtのMOSTを含む回路のリーク電流を、MOSTのゲート(G)とソース(S)を逆バイアスする各種の駆動方式によって低減する。低VtのMOSTに各種のG−S逆バイアスを加えることにより、リーク電流の少ない1V以下の高速低電圧CMOS論理回路、あるいはメモリ回路が実現される。

(もっと読む)

41 - 60 / 1,091

[ Back to top ]