Fターム[5J056CC00]の内容

論理回路 (30,215) | 構成要素(回路) (5,601)

Fターム[5J056CC00]の下位に属するFターム

定電流源 (480)

ミラー回路、カレントミラー回路 (296)

電源回路 (715)

遅延回路 (349)

フィルタ回路 (82)

積分回路 (27)

微分回路 (11)

比較器 (432)

オペアンプ (171)

シュミット回路 (34)

クランプ回路 (62)

リミッタ回路 (17)

双安定回路(フリップフロップ、ラッチ) (577)

単安定回路 (17)

非安定回路、発振回路 (126)

カウンタ (157)

シフトレジスタ (106)

プリチャージ回路 (44)

ディスチャージ回路 (10)

レベルシフト回路 (574)

ダーリントン (1)

エミッタホロワ (6)

オープンコレクタ (3)

ソースホロワ (26)

オープンドレイン (10)

ドット論理、ワイヤード論理 (8)

表示回路 (13)

昇圧回路(ブートストラップ) (120)

ポンプ回路 (36)

Fターム[5J056CC00]に分類される特許

61 - 80 / 1,091

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

差動信号出力装置、および、携帯機器

【課題】出力信号のスルーレートをより適切に制御することが可能な差動信号出力装置を提供する。

【解決手段】差動信号出力装置は、差動信号およびコモンモード信号を重畳して出力するための第1の送信端子および第2の送信端子を備える。差動信号出力装置は、データ信号に応じて前記差動信号を生成し前記第1の送信端子および前記第2の送信端子に出力する差動信号生成回路を備える。差動信号出力装置は、クロック信号に応じて前記コモンモード信号を生成し前記第1の送信端子および前記第2の送信端子に出力し、且つ、制御信号に応じて前記コモンモード信号のスルーレートを制御するコモンモード信号生成回路を備える。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

レベルシフト回路及び半導体装置

【課題】電源電圧が低電圧化したときの動作不良の発生を抑制することのできるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、第1の高電位電圧VLを信号レベルとする入力信号Siに応じて相補的にスイッチング制御されるNチャネルMOSトランジスタTN1,TN2を有するレベル変換部10を備える。レベルシフト回路1は、第1の高電位電圧VLの低下を検出したことを示す検出信号DSを生成する検出部20と、検出信号DSに応じて、トランジスタTN1,TN2の閾値電圧が低くなるようにトランジスタTN1,TN2のボディバイアスVbbを制御する制御部30とを備える。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体装置

【課題】立ち上がり時間と立ち下がり時間の差を解消しつつ、動作に伴う貫通電流の発生が防止されたレベルシフト回路を提供する。

【解決手段】互いに同じ回路構成を有するレベルシフト回路LV1,LV2と、レベルシフト回路LV1,LV2に相補の入力信号をそれぞれ供給する入力回路と、レベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡する出力回路とを備える。本発明によれば、同じ回路構成を有する2つのレベルシフト回路LV1,LV2を用いるとともに、これらレベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡していることから、レベルシフト回路LV1,LV2の動作速度差による貫通電流の発生がほとんど生じない。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

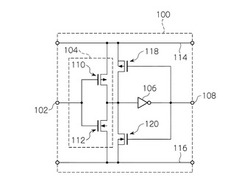

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

電圧発生装置

【課題】低電源電圧状態で、ビットラインプリチャージ電圧又はセルプレート電圧を安定的に駆動し、待機電流IDD2P及び動作電流を最小化すること。

【解決手段】電源電圧のハーフレベルの基準電圧を利用し、異なるレベルのバイアス信号を生成するバイアス信号生成手段と、出力端の電圧レベルに応答してプルダウン駆動信号を生成する駆動信号生成手段と、駆動信号に応答して出力端を駆動する電圧駆動手段と、出力端の電圧レベルに応じてプルアップ駆動信号/プルダウン駆動信号を生成する駆動信号生成手段と、前記プルアップ駆動信号/プルダウン駆動信号に応答して前記出力端をプルアップ駆動/プルダウン駆動するプルアップPMOSトランジスタ/プルダウンNMOSトランジスタと、第1多重化手段と、第2多重化手段とを備える半導体メモリ素子の電圧発生装置。

(もっと読む)

携帯電話

【課題】回路の誤動作や回路面積の増加を防止しつつ一部の回路の電源電圧を

遮断して消費電力を低減させることができる半導体集積回路を提供する。

【解決手段】チップ内部を複数の回路ブロック(11,12,13……)に分

割するとともに、いずれかの回路ブロックへの電源電圧の供給を遮断可能に構成

し、電源電圧の供給を遮断可能な回路ブロックから他の回路ブロックへ出力され

る信号の経路上であって信号が分岐される前の位置に、信号の伝達を遮断可能な

信号ゲート手段(31)と電源遮断直前の信号を記憶可能な記憶手段(32)と

を含むブロック間インタフェース回路(30)を設けるようにした。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

ドライバアンプ回路および通信システム

【課題】バイアス調整回路やプリドライバ回路が不要で、しかも出力波形の波形歪みを低減することが可能なドライバアンプ回路および通信システムを提供する。

【解決手段】スイッチングトランジスタM11〜M14を駆動するゲート電圧を均一にするため、スイッチングトランジスタM11〜M14を電源およびGND側に配置し、さらに、スイッチングトランジスタM11〜M14の駆動振幅を安定させるために、各スイッチングトランジスタM11のドレインと出力ノードND11、ND12間にそれぞれ第1から第4の抵抗素子R11〜R14を接続している。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

半導体集積回路装置

【課題】半導体基板の表側に配置された回路が半導体基板の裏側から解析されることを検出する技術を提供することを目的とする。

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

61 - 80 / 1,091

[ Back to top ]