半導体集積回路およびその制御方法

【課題】内部状態の退避・回復時間が短縮され、待機状態にある回路の消費電力が削減される半導体集積回路を提供する。

【解決手段】半導体集積回路は、対象回路と、バックアップ制御回路とを具備する。対象回路は、スキャンパステスト時にシフトレジスタを形成してテストデータをシリアルに入出力する少なくとも1つのスキャンチェーンを備える。バックアップ制御回路は、対象回路の内部状態を示す内部状態データをメモリに格納し、メモリから内部状態データを読み出す。このスキャンチェーンは、複数のサブスキャンチェーンに分割されている。複数のサブスキャンチェーンは並列に動作する。内部状態データは、複数のサブスキャンチェーンから出力されてメモリに格納される。メモリに格納されている内部状態データは、複数のサブスキャンチェーンに再び設定され、対象回路は、元の内部状態に戻って動作を再開する。

【解決手段】半導体集積回路は、対象回路と、バックアップ制御回路とを具備する。対象回路は、スキャンパステスト時にシフトレジスタを形成してテストデータをシリアルに入出力する少なくとも1つのスキャンチェーンを備える。バックアップ制御回路は、対象回路の内部状態を示す内部状態データをメモリに格納し、メモリから内部状態データを読み出す。このスキャンチェーンは、複数のサブスキャンチェーンに分割されている。複数のサブスキャンチェーンは並列に動作する。内部状態データは、複数のサブスキャンチェーンから出力されてメモリに格納される。メモリに格納されている内部状態データは、複数のサブスキャンチェーンに再び設定され、対象回路は、元の内部状態に戻って動作を再開する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路及びその制御方法に関し、特に、内部状態を退避回復する回路を備える半導体集積回路およびその制御方法に関する。

【背景技術】

【0002】

近年、スタンバイやレジューム機能等の低消費電力モードを備えた半導体集積回路が注目されている。通常、半導体集積回路は、電源供給が停止されると不揮発性メモリを除いてその内部状態は消去されるため、電源供給を再開した時、回路の電源供給を停止する直前の状態から回路の動作を再開させるためには、内部状態を保持しなくてはならない。

【0003】

例えば、特開平6−52070号公報によれば、レジスタに保持された内部状態データを電源供給停止時に外部メモリに退避させ、保持する集積回路が開示されている。この集積回路は、複数のレジスタとデータ退避部とデータ復帰部とを具備し、複数のレジスタは、スキャンチェーンを形成するように接続され、データ退避部は、外部信号に応答し、データ退避モード時に、複数のレジスタにスキャンチェーンを形成させ、形成されたスキャンチェーンを介して各レジスタの保持データを外部に読み出す。このとき、データ退避部は、内部状態データを所定のビット幅のデータに直列/並列変換し、データ入出力部を通じてデータ保護用メモリに格納する。データ復帰部は、外部信号に応答し、データ復帰モード時に、複数のレジスタにスキャンチェーンを形成させ、形成されたスキャンチェーンを介して退避していたデータをもとのレジスタに復帰させる。このとき、データ復帰部は、データ保護用メモリから内部状態データを読出してデータ入出力手段から入力し、所定のビット幅のデータを直列の内部状態データに変換してスキャンチェーンを通じて復帰する。

【0004】

また、特開2004−164647号公報によれば、1つまたは複数のノードを有する回路と、メモリと、システム・バスと、状態保存コントローラとを備えるデータ処理装置に関する技術が開示されている。1つまたは複数のノードを有する回路は、データの処理に用いられる回路であり、全体で回路の状態を定義する1つまたは複数のデータ値を記憶する。メモリは、データを記憶する。システム・バスは、回路とメモリとに結合するシステム・バスであり、回路とメモリの通常の処理動作中にシステム・バスに与えられたメモリ転送要求に応答して回路とメモリとの間で多ビット・データ語を転送する。状態保存コントローラは、回路とシステム・バスに結合し、保存トリガに応答して、回路の状態を定義するデータ値を1つまたは複数のノードから読み取ってメモリ書込み要求のシーケンスをシステム・バス上に生成し、データ値を表す1つまたは複数の状態保存多ビット・データ語をメモリに書き込んで、1つまたは複数の状態保存多ビット・データ語を用いて回路の状態を回復できるようにする。また、関連する技術として、米国公開公報2005/0149799に記載されたものもある。

【0005】

【特許文献1】特開平6−52070号公報

【特許文献2】特開2004−164647号公報

【特許文献3】米国公開公報2005/0149799

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述のように、スキャンチェーンを用いて内部状態を退避・復帰する場合には、スキャンチェーンが直列接続された多数のレジスタによって構成されているために、レジスタに保持された全てのデータをシリアルに退避・復帰するために時間がかかる。また、システムバスを介して内部ノードデータをメモリに書き込み、メモリから読み出すために、システムバスの使用権確保を含むメモリ書き込みシーケンス、メモリ読み出しシーケンスを起動する必要性があるため、やはり内部状態の退避・回復時間が長くなる。

【0007】

本発明は、半導体集積回路を待機状態にしつつ、内部状態の退避・回復時間を短縮することができる半導体集積回路及びその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0009】

本発明の観点では、半導体集積回路は、対象回路(11)と、バックアップ制御回路(12)とを具備する。対象回路(11)は、スキャンパステスト時にシフトレジスタを形成してテストデータをシリアルに入出力する少なくとも1つのスキャンチェーン(15)を備える。バックアップ制御回路(12)は、対象回路(11)の内部状態を示す内部状態データをメモリ(13)に格納し、メモリ(13)から内部状態データを読み出す。このスキャンチェーン(15)は、複数のサブスキャンチェーン(21〜24、31〜34)に分割されている。複数のサブスキャンチェーン(21〜24、31〜34)は並列に動作する。内部状態データは、複数のサブスキャンチェーン(21〜24、31〜34)から出力されてメモリ(13)に格納される。メモリ(13)に格納されている内部状態データは、複数のサブスキャンチェーン(21〜24、31〜34)に再び設定され、対象回路(11)は、元の内部状態に戻って動作を再開する。

【0010】

本発明の他の観点では、内部状態退避回復方法は、動作切替ステップと、退避ステップと、回復ステップと、再開ステップとを具備する。対象回路(11)は、スキャンパステストに使用される少なくとも1つのスキャンチェーン(15)を備える。動作切替ステップは、そのスキャンチェーン(15)を分割して、並列に動作する複数のサブスキャンチェーン(21〜24、31〜34)に構成し直す。退避ステップは、複数のサブスキャンチェーン(21〜24、31〜34)の各々から出力される対象回路(11)の内部状態を示す内部状態データをメモリ(13)に格納する。回復ステップは、メモリ(13)から出力される内部状態データを複数のサブスキャンチェーン(21〜24、31〜34)に再び設定する。再開ステップは、複数のサブスキャンチェーン(21〜24、31〜34)を解放して対象回路(11)の動作を元の状態から再開する。

【発明の効果】

【0011】

本発明によれば、スキャンチェーンを複数のサブスキャンチェーンに分割し、サブスキャンチェーンの出力を並列にメモリに格納することによって、内部状態の退避・回復時間が短縮された半導体集積回路及びその制御方法を提供することが可能になる。

【発明を実施するための最良の形態】

【0012】

図を参照して本発明の第1の実施の形態を説明する。図1は、第1の実施の形態に係る半導体集積回路の構成を示すブロック図である。半導体集積回路は、内部状態が外部に退避される対象回路11と、対象回路11の内部状態を記憶するバックアップメモリ13と、対象回路11の内部状態の退避・回復を制御するバックアップ制御回路12と、対象回路11の電源を制御するスイッチ14とを具備する。対象回路11の内部状態は、対象回路11に内在するフリップフロップに保持される内部ノードデータにより具現化される。

【0013】

バックアップ制御回路12は、対象回路11から指示(WFI)を受けて、対象回路11の動作モード(MD)を切り替え、対象回路11の内部状態を示すデータ即ち内部ノードデータをバックアップメモリ13に退避する。また、バックアップ制御回路12は、外部からの割り込み信号(INT)により起動され、バックアップメモリ13に格納されている内部ノードデータを対象回路11の各ノードに設定し、対象回路11の内部状態を回復する。この内部状態の退避・回復動作に際し、バックアップ制御回路12は、バックアップメモリ13の格納アドレス(ADDR)、書き込み・読み出しタイミング(CTR)を制御する。

【0014】

対象回路11の電源系は、他の回路と分離されている。従って、対象回路11だけの電源を切断することが可能となる。スイッチ14は、この電源の投入切断をバックアップ制御回路12の制御(PWC)に基づいて行う。

【0015】

バックアップメモリ13は、対象回路11の内部状態を示す内部ノードデータを保持する。バックアップメモリ13は、対象回路11の内部ノードデータを格納するだけの容量があればよい。内部ノードデータTOを効率よく取り込むためにデータ幅(ワード長)は広くなっている。例えば、スキャンチェーンが32個、それぞれのスキャンチェーンから4ヵ所の内部ノードデータTOを取り出すとすると、1スキャンクロック毎に128ビットのデータが並列に出力される。そのため、バックアップメモリ13は、128ビット以上のワード長が必要になる。バックアップメモリ13の書き込み/読み出しの動作タイミングCTR、アドレスADDRは、バックアップ制御回路12から与えられる。このバックアップメモリ13は、閾値電圧が高く設定され、低リーク電流のメモリである。従って、バックアップメモリ13の速度はそれほど速くないが、消費電力は少ない。また、バックアップメモリ13として、フラッシュメモリ等の不揮発性メモリを用いると、待機時にバックアップメモリ13の電源も切断することが可能となり、さらに消費電力を削減することができる。

【0016】

この対象回路11の内部状態を示す内部ノードデータは、スキャンチェーン15を介して入出力される。スキャンチェーン15は、半導体集積回路の正常性を試験するスキャンパステストに使用される。スキャンチェーン15は、スキャンパステスト時、テストデータをスキャン入力SIからシリアル入力し、テスト結果をスキャン出力SOから出力する。ここでは説明しないが、バックアップ制御回路12、バックアップメモリ13は、スキャンパステストの対象であってもよい。

【0017】

対象回路11は、待機中に保持すべき内部状態を有する回路部分である。対象回路11は、対象回路11の製造不良等を検出するために実施されるスキャンパステスト用の回路を内蔵している。このスキャンパステスト用回路は、テスト時に対象回路11に内在するフリップフロップが鎖状に接続され、シフトレジスタとしてデータの入出力を行う。このシフトレジスタが、所謂スキャンチェーンと呼ばれる。対象回路11内には、このスキャンチェーン15が少なくとも1つ設定されている。最近の半導体集積回路では、スキャンチェーン15は、32個程度設定されていることが多いが、より多くのスキャンチェーンが設定されていてもよいし、1個だけであってもよい。各スキャンチェーン15は、外部に接続されるスキャン入力SI(SI1〜SIn〜SIN)からスキャンパステスト用のシリアルデータが入力され、外部に接続されるスキャン出力SO(SO1〜SOn〜SON)からスキャンパステスト結果データがシリアルに出力される。それぞれのシリアルデータの入出力は、同期している必要はなく、スキャンチェーン毎に独立して動作していてもよい。以下、スキャンチェーン15は、スキャン入力SIn、スキャン出力SOn(n=1、2、…、N)の回路を例として説明される。

【0018】

対象回路11は、内部の論理回路が動作すると、論理回路に含まれる順序回路(フリップフロップ)にその動作状態が保持される。即ち、フリップフロップは、対象回路11の内部状態を保持している。このフリップフロップに保持された内部ノードデータを退避することにより対象回路11の内部状態が外部に出力でき、データを各フリップフロップに設定することにより対象回路11の内部状態を設定することができる。一方、フリップフロップは、スキャンパステスト時、スキャンチェーン15を形成し、その保持しているデータをシリアル出力することができる。また、スキャンチェーン15は、データをシリアル入力して、スキャンパステストするためのデータを各フリップフロップに設定することができる。従って、このスキャンチェーン15を使うことにより、フリップフロップの状態を読み出し、書き込むことが可能である。

【0019】

対象回路11は、バックアップ制御回路12の制御に基づいて、スキャンチェーン15の出力、即ち、スキャン出力SOとスキャンチェーン15の途中の複数の位置から取り出したデータTOとをバックアップメモリ13に出力する。対象回路11の全てのフリップフロップに保持されるデータが出力されると、対象回路11の内部状態がバックアップメモリ13に退避されたことになる。また、対象回路11は、バックアップ制御回路12の制御に基づいて、バックアップメモリ13から出力されるデータTIを取り込みスキャンチェーン15に設定する。スキャンチェーン15にデータが設定されると、対象回路11の内部状態が回復されたことになる。対象回路11を回復状態から通常動作状態に切り替えると、対象回路11は、通常動作に復帰する。

【0020】

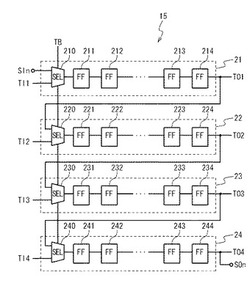

図2にスキャンチェーンが有効になっている時のスキャンチェーン15の構成が示される。スキャンチェーン15は、スキャンテスト時に複数のレジスタを連結して構成される1本のチェーンであり、この1本のチェーンを複数に分割したものがサブスキャンチェーンである。スキャンチェーン15は、複数のサブスキャンチェーンを備える。ここでは、スキャンチェーン15は、4つのサブスキャンチェーン21、22、23、24を備える。サブスキャンチェーン21、22、23、24は、それぞれ同数のフリップフロップを含む。サブスキャンチェーン21、22、23、24は縦続接続され、スキャンパステストの際、1つのスキャンチェーン15として動作する。内部ノードデータの入出力時、サブスキャンチェーン21、22、23、24は並列に動作し、同時にデータを入出力する。サブスキャンチェーン21は、選択回路210と、スキャンチェーンの実体であるフリップフロップ211〜214を備える。同じように、サブスキャンチェーン22は選択回路220とフリップフロップ221〜224を備え、サブスキャンチェーン23は選択回路230とフリップフロップ231〜234を備え、サブスキャンチェーン24は選択回路240とフリップフロップ241〜244を備える。選択回路210、220、230、240は、選択信号TBに基づいて、入力される2つの信号のどちらかを選択して出力する。

【0021】

サブスキャンチェーン21では、選択回路210は、スキャン入力SInと、バックアップメモリ13に格納されていた内部ノードデータTI1とを入力する。選択回路210は、選択信号TBに基づいて、スキャンパステスト時はスキャン入力SInから入力されるデータを選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI1を選択して出力する。フリップフロップ211〜214は鎖状に接続されてシフトレジスタを形成し、選択回路210の出力信号が入力される。フリップフロップ214の出力は、内部ノードデータTO1として出力されるとともに、次段のサブスキャンチェーン22に送られる。

【0022】

サブスキャンチェーン22では、選択回路220は、前段のサブスキャンチェーン21の出力データTO1と、バックアップメモリ13に格納されていた内部ノードデータTI2とを入力する。選択回路220は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO1を選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI2を選択して出力する。フリップフロップ221〜224は、鎖状に接続されてシフトレジスタを形成し、選択回路220の出力信号が入力される。フリップフロップ224の出力は、内部ノードデータTO2として出力されるとともに、次段のサブスキャンチェーン23に送られる。

【0023】

同じように、サブスキャンチェーン23では、選択回路230は、前段のサブスキャンチェーン22の出力データTO2と、バックアップメモリ13に格納されていた内部ノードデータTI3とを入力する。選択回路230は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO2を選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI3を選択して出力する。フリップフロップ231〜234は、鎖状に接続されてシフトレジスタを形成し、選択回路230の出力信号が入力される。フリップフロップ234の出力は、内部ノードデータTO3として出力されるとともに、次段のサブスキャンチェーン24に送られる。

【0024】

同じように、サブスキャンチェーン24では、選択回路240は、前段のサブスキャンチェーン23の出力データTO3と、バックアップメモリ13に格納されていた内部ノードデータTI4とを入力する。選択信号TBに基づいて、選択回路240は、スキャンパステスト時は前段出力データTO3を選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI4を選択して出力する。フリップフロップ241〜244は、鎖状に接続されてシフトレジスタを形成し、選択回路240の出力信号が入力される。フリップフロップ244の出力は、内部ノードデータTO4として出力されるとともに、スキャンチェーン15の出力SOnとして外部に出力される。

【0025】

次にスキャンチェーン15の動作が説明される。対象回路11の本来の機能動作時、フリップフロップ211〜214、フリップフロップ221〜224、フリップフロップ231〜234、フリップフロップ241〜244は、内部論理回路のレジスタとして、対象回路11の内部状態(内部ノードデータ)を保持している。

【0026】

スキャンパステストの場合、対象回路11に内在するフリップフロップは、図2に示されるように、スキャンチェーン15を構成するように接続される。スキャンチェーンに関してはよく知られているため、詳細な説明は省略される。実際には、接続配線されていて、図示されていないフリップフロップに内蔵された選択回路が、スキャンチェーンを形成する時にスキャンチェーンの信号を選択するように設定される。選択回路210、220、230、240は、選択信号TBによりスキャンデータ側のデータを選択して出力するように設定される。従って、サブスキャンチェーン21〜24に含まれるフリップフロップは、連結された1つのシフトレジスタを形成する。スキャンクロックに同期してスキャンデータは、スキャン入力SInから入力され、スキャン出力SOnに向かって順次フリップフロップを移動していく。全てのフリップフロップにスキャンデータが設定されると、各フリップフロップは、一旦スキャンチェーン15の構成から解放され、本来の内部論理回路である対象回路11のデータを取り込む。このとき、各フリップフロップはスキャンデータを出力しているため、各フリップフロップはスキャンパステストの結果を保持することになる。その後、フリップフロップはスキャンチェーン15の構成に戻る。スキャンパステストの結果を保持するシフトレジスタは、スキャンクロックに基づいて、スキャンパステストの結果データをスキャン出力SOnから出力する。

【0027】

内部ノードデータ退避の場合、スキャンチェーン15は、サブスキャンチェーン21〜24が並列に機能するように設定される。選択信号TBは、どちらに設定されていてもよいが、ここではバックアップメモリ13の出力(TI)を選択するように設定される。スキャンパステスト時と同じように、フリップフロップに保持されている内部ノードデータは、クロックに同期して並列にサブスキャンチェーンの出力データTO1〜TO4として順次バックアップメモリ13に出力される。バックアップメモリ13のアドレスADDRは、バックアップ制御回路12によりクロックに同期して更新され、サブスキャンチェーンの出力データTO1〜TO4は、バックアップメモリ13に順に記憶される。サブスキャンチェーンに含まれるフリップフロップの数だけデータを出力すると、このスキャンチェーン15に含まれる全ての内部ノードデータは、バックアップメモリ13に出力されたことになる。従って、スキャンチェーン15の出力SOnをメモリに接続して内部ノードデータを記憶させるより、出力時間は短縮できる。図2に示されるように、スキャンチェーン15をサブスキャンチェーン21〜24のように4分割すると、出力時間は1/4になる。

【0028】

内部ノードデータ回復の場合、即ち、バックアップメモリ13に保持されている内部ノードデータを元のフリップフロップに設定する場合、スキャンチェーン15は、サブスキャンチェーン21〜24が並列に機能するように設定される。選択信号TBは、バックアップメモリ13の出力(TI)を選択するように設定される。バックアップメモリ13から内部ノードデータTI1〜4がサブスキャンチェーン21〜24に入力される。バックアップ制御回路12は、バックアップメモリ13のアドレスADDRを初期設定値からクロック毎に更新して、内部ノードデータTI1〜4が退避された順にサブスキャンチェーン21〜24に供給されるように制御する。サブスキャンチェーン21〜24に供給される内部ノードデータTI1〜4は、選択回路210、220、230、240を介してサブスキャンチェーン内に形成されるシフトレジスタを出力TO1〜4に向けて移動していく。サブスキャンチェーンに含まれるフリップフロップの数だけシフトすると、各フリップフロップには元の内部ノードデータが設定されている。これで対象回路11の内部状態は回復したことになる。その後、バックアップ回復モードを解除すると、対象回路11は通常の動作に復帰する。

【0029】

このように、スキャンチェーン(サブスキャンチェーン)を用いて、内部ノードデータをバックアップメモリ13に退避し、バックアップメモリ13から内部ノードデータを対象回路11に回復する回路を内蔵する半導体集積回路の動作状態が図3を参照して説明される。ここでは、対象回路11は、半導体集積回路に内蔵されるCPU(中央演算処理部)であるとし、CPUが実行しているソフトウェアの処理状態が対象回路11の状態として説明される。図3の左側に半導体集積回路を外部(ソフトウェア)の観点で見たときの動作状態が示される。図3の右側に内部(ハードウェア)の観点で見たときの対象回路11、バックアップ制御回路12、バックアップメモリ13の動作状態が示される。

【0030】

半導体集積回路は、通常の動作において、例えば、周期処理やマンマシンインタフェース処理等により待機状態になることがある。そのとき、CPU11は、WFI(Wait for Interrupt)命令を実行し、待機状態になる。通常、待機状態では、ソフトウェアの実行は停止される。その場合、処理再開を指示する割り込み信号INTが入力されると即時実行再開ができるように、ハードウェアは必要最小限の待機電圧まで電源電圧を引き下げ、消費電力を削減する。さらに消費電力を削減するために、本発明では、図3に破線により囲まれて示されるように、CPU11の電源供給が停止され、待機状態におけるリーク電流が削減される。CPU11の電源がオフされると、CPU11の内部状態がクリアされるため、電源がオフされる前に、CPU11の内部状態がバックアップメモリ13に退避される。

【0031】

CPU11の動作を再開するトリガとなる割り込み信号INTがバックアップ制御回路12に入力されると、CPU11の電源がオンされる。CPU11の内部状態がバックアップメモリ13から回復され、ソフトウェアの実行が再開される。割り込み信号INTが入力されるため、ソフトウェアは割り込み処理をまず実行し、その後通常の処理に戻ることになる。従って、ソフトウェアとしては、電源のオン・オフに影響されずに、待機状態が維持されていたように動作することになる。

【0032】

即ち、対象回路(CPU)11は、WFI命令が発行されるまで通常の作動状態であり、WFI命令によりソフトウェアは停止するため、内部状態は凍結される。WFI命令が発行されると、バックアップ制御回路12とバックアップメモリ13は、待機状態から起動される。バックアップ制御回路12は、対象回路(CPU)11をスキャンチェーンが設定される退避状態にする。バックアップ制御回路12は、対象回路(CPU)11の凍結された内部ノードデータをバックアップメモリ13に退避する。対象回路(CPU)11の全ての内部ノードデータが退避されると、バックアップ制御回路12は、スイッチ14を制御して対象回路(CPU)11の電源供給を停止する。バックアップ制御回路12は、割り込み信号INTが入力されるまで、待機状態になる。バックアップ制御回路12とバックアップメモリ13は、対象回路(CPU)11に比較して回路規模も小さく、また、低消費電力になるように構成されるため、リーク電流は削減される。

【0033】

割り込み信号INTがバックアップ制御回路12に入力されると、バックアップ制御回路12は、待機状態から作動状態に復帰する。まず、バックアップ制御回路12は、スイッチ14を制御して対象回路(CPU)11の電源供給を再開する。次に、バックアップ制御回路12は、対象回路(CPU)11をスキャンチェーンが設定される回復状態にする。バックアップ制御回路12は、バックアップメモリ13に記憶されている内部ノードデータTIをサブスキャンチェーンに供給し、内部状態をリストアする。対象回路(CPU)11の内部状態が元の状態に回復すると、バックアップ制御回路12は、対象回路(CPU)11の回復状態を解除して対象回路(CPU)11を起動する。対象回路(CPU)11は、動作を再開する。バックアップ制御回路12とバックアップメモリ13は、次のWFI命令発行まで待機状態になる。ここでは、対象回路11はCPUであるとして説明されたが、対象回路11はCPUに限らずランダムロジック回路でも同様に実施することが可能である。

【0034】

このように、スキャンチェーン15よりも短いサブスキャンチェーン21〜24にシリアルデータを送り込んで内部状態を再設定することになり、復帰時間は短縮される。上述のように、本発明によれば、より短い時間で内部状態を退避・回復することが可能になり、かつ、待機期間のリーク電流を削減することができる。

【0035】

図4は、さらに最小回復時間を短縮するための経路を設けたスキャンチェーンの構成を示すブロック図である。最小回復時間は、内部状態データの退避が開始された直後に退避の中止、即ち、内部状態データの回復が指示されたときに要する時間である。図4に示されるスキャンチェーン15は、図2に示されるサブスキャンチェーン21〜24の各々の先頭にさらに選択回路が設けられている。

【0036】

このスキャンチェーン15は、サブスキャンチェーン31、32、33、34を備える。サブスキャンチェーン31は、選択回路319、310とフリップフロップ311〜314を備える。同じように、サブスキャンチェーン32は、選択回路329、320とフリップフロップ321〜324を備え、サブスキャンチェーン33は、選択回路339、330とフリップフロップ331〜334を備え、サブスキャンチェーン34は、選択回路349、340とフリップフロップ341〜344を備える。選択回路319、329、339、349を除く部分は、図2に示されるスキャンチェーンと同じである。

【0037】

選択回路319、329、339、349は、選択信号BRに基づいて、バックアップメモリ13が出力する退避された内部ノードデータTIと、サブスキャンチェーンが出力する内部ノードデータTOのいずれかを選択して選択回路310、320、330、340に出力する。

【0038】

サブスキャンチェーン31では、選択回路319は、バックアップメモリ13から入力される内部ノードデータTI1と、サブスキャンチェーン31が出力する内部ノードデータTO1とを入力する。選択回路319は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO1を選択して出力し、内部状態回復時は退避されていた内部ノードデータTI1を選択して出力する。選択回路310は、スキャン入力SInと、選択回路319の出力信号とを入力する。選択回路310は、選択信号TBに基づいて、スキャンパステスト時はスキャン入力信号SInを選択して出力し、内部状態退避・回復時は選択回路319の出力信号を選択して出力する。フリップフロップ311〜314は、鎖状に接続されてシフトレジスタを形成し、選択回路310の出力信号が入力される。フリップフロップ314の出力信号は、内部ノードデータTO1として出力されるとともに、次段のサブスキャンチェーン32に送られる。

【0039】

サブスキャンチェーン32では、選択回路329は、バックアップメモリ13から入力される内部ノードデータTI2と、サブスキャンチェーン32が出力する内部ノードデータTO2とを入力する。選択回路329は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO2を選択して出力し、内部状態回復時は退避されていた内部状態TI2を選択して出力する。選択回路320は、前段のサブスキャンチェーン31の出力データTO1と、選択回路329の出力信号とを入力する。選択回路320は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO1を選択して出力し、内部状態退避・回復時は選択回路329の出力信号を選択して出力する。フリップフロップ321〜324は、鎖状に接続されてシフトレジスタを形成し、選択回路320の出力信号が入力される。フリップフロップ324の出力信号は、内部ノードデータTO2として出力されるとともに、次段のサブスキャンチェーン33に送られる。

【0040】

同じように、サブスキャンチェーン33では、選択回路339は、バックアップメモリ13から入力される内部ノードデータTI3と、サブスキャンチェーン33が出力する内部ノードデータTO3とを入力する。選択回路339は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO3を選択して出力し、内部状態回復時は退避されていた内部状態TI3を選択して出力する。選択回路330は、前段のサブスキャンチェーン32の出力データTO2と、選択回路339の出力データとを入力する。選択回路330は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO2を選択して出力し、内部状態退避・回復時は選択回路339の出力信号を選択して出力する。フリップフロップ331〜334は、鎖状に接続されてシフトレジスタを形成し、選択回路330の出力信号が入力される。フリップフロップ334の出力は、内部ノードデータTO3として出力されるとともに、次段のサブスキャンチェーン34に送られる。

【0041】

同じように、サブスキャンチェーン34では、選択回路349は、バックアップメモリ13から入力される内部ノードデータTI4と、サブスキャンチェーン34が出力する内部ノードデータTO4とを入力する。選択回路349は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO4を選択して出力し、内部状態回復時は退避されていた内部状態TI4を選択して出力する。選択回路340は、前段のサブスキャンチェーン33の出力データTO3と、選択回路349の出力データとを入力する。選択回路340は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO3を選択して出力し、内部状態退避・回復時は選択回路349の出力信号を選択して出力する。フリップフロップ341〜344は、鎖状に接続されてシフトレジスタを形成し、選択回路340の出力信号が入力される。フリップフロップ344の出力は、内部ノードデータTO4として出力されるとともに、スキャンチェーン15の出力SOnとして外部に出力される。

【0042】

図5A、B、Cを参照してスキャンチェーン15の動作が説明される。スキャンチェーンが形成されていない時、フリップフロップ311〜314、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344は、対象回路11の内部状態を保持している。

【0043】

スキャンパステストの場合、図5Aに示されるように、対象回路11に内在するフリップフロップはスキャンチェーンを形成する。このとき、選択信号TBは、スキャンパステスト用のデータを選択するように設定される。選択信号BRの設定は、信号の経路に影響しないのでどちらでもよい。従って、フリップフロップ311〜314、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344は、連続する1つのシフトレジスタを形成する。図5Aに太線で示されるように、スキャンパステスト用データは、スキャン入力SInから入力され、順次フリップフロップを移動して各フリップフロップに設定される。

【0044】

各フリップフロップにスキャンパステスト用データが設定されると、一旦スキャンチェーンは解除され、内部論理の動作チェックが行われる。その結果は、各フリップフロップに取り込まれ、再度スキャンチェーンが形成される。各フリップフロップに設定されたチェック結果は、シフトレジスタを形成しているフリップフロップを移動してスキャン出力SOnから順次出力される。このように、スキャンパステストにおけるデータの入出力が行われる。

【0045】

次に、図5Bを参照して対象回路11の内部ノードデータをバックアップメモリ13に退避する退避動作が説明される。内部ノードデータの退避動作の場合、選択回路310、320、330、340は、それぞれ、選択信号TBに基づいて、選択回路319、329、339、349から入力されるデータを選択して出力するように設定される。選択信号BRは、サブスキャンチェーン31〜34の出力TO1〜TO4をそれぞれ自身の入力TI1〜TI4に戻すように設定される。即ち、図5Bに太線で示されるように、内部ノードデータは、各サブスキャンチェーン内で循環するようにシフトされる。従って、サブスキャンチェーン31に保持されていた内部ノードデータが全て出力データTO1として出力されると、フリップフロップ311〜314には元の内部ノードデータが設定されていることになる。サブスキャンチェーン32、33、34においても同じように、内部ノードデータを全て出力し終わると、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344は、元の内部ノードデータを保持する。

【0046】

これは、内部ノードデータの退避と回復とを同時に行っていることに他ならない。例えば、対象回路11の内部ノードデータをバックアップメモリ13に退避している最中に割り込み信号INTが入力され、復帰動作を開始しなければならない場合、退避動作が完了した時点で対象回路の動作を再開することが可能となる。図2に示されるスキャンチェーン15の構成では、一旦退避動作が開始されると、内部ノードデータを全てバックアップメモリ13に退避し、その後バックアップメモリ13から内部ノードデータをスキャンチェーン15に回復させる必要がある。それに対して、このように、サブスキャンチェーン31〜34の内部ノードデータTO1〜TO4を自身に循環させることにより、退避動作直後に対象回路11の通常動作を再開することが可能となる。従って、退避動作が開始されてから動作回復までの時間を短縮することができる。

【0047】

図5Cを参照してバックアップメモリ13に格納されている内部ノードデータから対象回路11の内部状態を回復する回復動作が説明される。バックアップメモリ13には、図5Bを参照して説明されたように、対象回路11の内部ノードデータが順に格納されている。このデータを対象回路11に回復する場合、選択回路310、320、330、340は、選択信号TBに基づいて、それぞれ選択回路319、329、339、349から入力されるデータを選択して出力するように設定される。選択信号BRは、選択回路319、329、339、349がバックアップメモリ13から出力される内部ノードデータTIを選択して出力するように設定される。

【0048】

即ち、図5Cに太線で示されるように、バックアップメモリ13から入力される内部ノードデータTI1は、サブスキャンチェーン31内をシフトされてフリップフロップ311〜314に設定される。同じように、内部ノードデータTI2は、サブスキャンチェーン32内をシフトされてフリップフロップ321〜324に設定される。内部ノードデータTI3は、サブスキャンチェーン33内をシフトされてフリップフロップ331〜334に設定される。内部ノードデータTI4は、サブスキャンチェーン34内をシフトされてフリップフロップ341〜344に設定される。

【0049】

このように、バックアップメモリ13に保持されている内部ノードデータは、フリップフロップ311〜314、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344に格納され、元の内部状態に戻る。その後、スキャンチェーンが解除されて対象回路11は通常の動作に復帰する。

【0050】

上述において、サブスキャンチェーンは、それぞれ同数のフリップフロップを含むものとして説明したが、スキャンチェーン15に含まれるフリップフロップの総数は、サブスキャンチェーン数の倍数であるとは限らない。従って、各サブスキャンチェーンに含まれるフリップフロップの数が異なる場合、仮の内部ノードデータを保持するダミーのフリップフロップを挿入して数を揃えることが好ましい。また、含まれるフリップフロップの数が等しいサブスキャンチェーン毎に同時にバックアップメモリに出力するように構成することも可能である。その場合、挿入されるダミーフリップフロップの数を少なく、あるいは不用とすることができる。また、サブスキャンチェーン毎に与えるシフトクロックを変えることにより、内蔵するフリップフロップの数が異なるサブスキャンチェーンの内部ノードデータを退避・回復することも可能である。

【0051】

図6は、ダミーフリップフロップを備えたスキャンチェーン15の一例を示すブロック図である。このダミーフリップフロップは、他のスキャンチェーンに属し、スキャンパステストの時、他のスキャンチェーンの一部として動作する。図6に示されるスキャンチェーン15は、図2に示されるスキャンチェーンのフリップフロップ224、241がない状態である。即ち、図6に示されるスキャンチェーン15は、サブスキャンチェーン22、24に含まれるフリップフロップの数が、サブスキャンチェーン21、23より少ない。サブスキャンチェーン22は、スキャンチェーン15に含まれていないフリップフロップ(以降ダミーフリップフロップと称する)224’をフリップフロップ223の後段に接続される。従って、フリップフロップ223は、ダミーフリップフロップ224’と次段のサブスキャンチェーン23の選択回路230とに接続される。ダミーフリップフロップ224’は、フリップフロップ223の出力をバックアップメモリ13に出力する。また、サブスキャンチェーン24は、ダミーフリップフロップ241’を選択回路240の前段に接続される。バックアップメモリ13から出力された内部ノードデータTI4は、ダミーフリップフロップ241’に入力される。ダミーフリップフロプ241’の出力は、選択回路240を介してシフトレジスタを構成するフリップフロップ242〜244に入力される。このように、ダミーフリップフロップ224’、241’をサブスキャンチェーン22、24に接続することにより、サブスキャンチェーン21、23に含まれるフリップフロップと同数のフリップフロップを含むサブスキャンチェーン22’、24’が形成される。従って、サブスキャンチェーン21、22’、23、24’は、同じデータ数の内部状態データをバックアップメモリ13に出力することが可能となる。また、サブスキャンチェーン21、22’、23、24’は、同じデータ数の内部状態データをバックアップメモリ13から取り込んで各フリップフロップに設定することが可能となる。ここでは、過不足のフリップフロップ数はサブスキャンチェーン当たり1回路で説明したが、複数であっても各サブスキャンチェーンのフリップフロップ数を揃えることはできる。また、ダミーフリップフロップは、元のサブスキャンチェーンの前後のどちらに接続されても、さらに前後両側に接続されても同じように動作する。また、このダミーフリップフロップが接続されたサブスキャンチェーンの先頭に第2の選択回路を配置し、図4に示されるように、各サブスキャンチェーンの出力を先頭にフィードバックする構成にすることも可能である。

【0052】

このように、ダミーフリップフロップを接続することにより、スキャンパステスト時のスキャンチェーンにダミーフリップフロップを含むことなく、サブスキャンチェーンに含まれるフリップフロップの数をそろえることができる。このダミーフリップフロップは、バックアップ制御回路と一緒にスキャンチェーンに含めることができ、対象回路のスキャンパステストに影響を与えることを防ぐことができる。

【0053】

次に、図7を参照して第2の実施の形態が説明される。第2の実施の形態では、スキャンチェーンとバックアップメモリとのインタフェースが第1の実施の形態と異なる例が説明される。図7に、半導体集積回路の構成ブロック図が示される。半導体集積回路は、対象回路11とバックアップメモリ13とバックアップ制御回路12とスイッチ14とバスインタフェース部16とを具備する。対象回路11は、内部状態が外部に退避される回路であり、その電源はスイッチ14により制御される。スイッチ14は、バックアップ制御回路12により制御される。対象回路11の内部状態は、バスインタフェース部16によりシステムバス18に乗せられ、バックアップメモリ13に退避される。また、バックアップメモリ13に記憶されている内部状態は、システムバス18に乗せられ、バスインタフェース部16を介して対象回路11に回復される。対象回路11の内部状態の退避・回復は、バックアップ制御回路12により制御される。

【0054】

対象回路11の構成、動作は、図1に示される回路と同じである。従って、スキャンチェーン15に保持される内部状態は、スキャンパステストのときスキャン出力SOとして外部に出力される。対象回路11の内部状態退避のとき、スキャンチェーン15に保持される内部ノードデータは、サブスキャンチェーンに分割されたパスを介してバスインタフェース部16に送られる。このとき、内部ノードデータは、バスインタフェース部16において、バス幅に等しいデータ幅でバスインタフェース部16に送られることが好ましい。バスインタフェース部16は、内部ノードデータの信号レベルやタイミングを調整してシステムバス18に出力する。これに同期して、バックアップメモリ13は、システムバス18から内部ノードデータを取り込み、記憶する。バックアップメモリ13のアドレスADDRは、バックアップ制御回路12から供給される。

【0055】

対象回路11の内部状態回復のとき、バックアップメモリ13に格納されている内部ノードデータは、バックアップ制御回路12から出力されるアドレスADDRに基づいて読み出され、システムバス18に送られる。これに同期して、バスインタフェース部16は、システムバス18からデータを取り込み、対象回路11のサブスキャンチェーンに内部ノードデータTIとして供給する。システムバス18からデータを取り込むタイミング、信号レベルの変換などは、バスインタフェース部16が調整する。サブスキャンチェーンは、第1の実施の形態において説明された動作を行う。

【0056】

このように、内部ノードデータTOは、システムバス18を介してバックアップメモリ13に格納され、バックアップメモリ13に格納される内部ノードデータは、システムバス18を介して対象回路11に内部ノードデータTIとして供給され、対象回路11は、元の内部状態に戻る。

【0057】

システムバス18を介して対象回路11の内部ノードデータをバックアップメモリ13に退避し、バックアップメモリ13から回復することにより、半導体集積回路は、システムバス18に接続されているシステムメモリの一部をバックアップメモリ13として使用することも可能となる。その場合、バックアップ制御回路12は、システムバス18のインタフェース仕様に基づいてメモリをアクセスすることになる。

【0058】

また、システムバス18を介してシステムメモリにアクセス可能となれば、バックアップメモリ13は、対象回路11を内蔵する半導体集積回路の外部にあってもよいことになる。即ち、汎用のインタフェースがサポートされることにより、バックアップメモリとして使用されるメモリの選択の自由度が向上する。

【0059】

上述のように、スキャンチェーンをサブスキャンチェーンに分割することにより、対象回路11の内部ノードデータは、短時間に退避され、回復されるようになる。さらに、対象回路11の内部状態が外部で保持されるため、対象回路11の電源供給を停止することができ、消費電力の低減が可能となる。また、サブスキャンチェーンの各々の先頭に選択回路を挿入し、サブスキャンチェーンの出力を戻すことにより、内部状態の退避動作の中止に応じる回復動作の時間をさらに短縮することが可能となる。

【図面の簡単な説明】

【0060】

【図1】本発明の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【図2】同スキャンチェーンの構成を示すブロック図である。

【図3】同半導体集積回路の動作状態を示す図である。

【図4】同スキャンチェーンの他の構成を示すブロック図である。

【図5A】同他の構成のスキャンチェーンのテスト時の動作を示す図である。

【図5B】同他の構成のスキャンチェーンの退避時の動作を示す図である。

【図5C】同他の構成のスキャンチェーンの回復時の動作を示す図である。

【図6】同ダミーフリップフロップを備えるスキャンチェーンの構成を示すブロック図である。

【図7】同半導体集積回路の他の構成を示すブロック図である。

【符号の説明】

【0061】

11 対象回路

12 バックアップ制御回路

13 バックアップメモリ

14 スイッチ

15 スキャンチェーン

16 バスインタフェース部

18 システムバス

21、22、23、24 サブスキャンチェーン

210、220、230、240 選択回路

211〜214、221〜224、231〜234、241〜244 フリップフロップ

31、32、33、34 サブスキャンチェーン

310、320、330、340 選択回路

311〜314、321〜324、331〜334、341〜344 フリップフロップ

319、329、339、349 選択回路

【技術分野】

【0001】

本発明は、半導体集積回路及びその制御方法に関し、特に、内部状態を退避回復する回路を備える半導体集積回路およびその制御方法に関する。

【背景技術】

【0002】

近年、スタンバイやレジューム機能等の低消費電力モードを備えた半導体集積回路が注目されている。通常、半導体集積回路は、電源供給が停止されると不揮発性メモリを除いてその内部状態は消去されるため、電源供給を再開した時、回路の電源供給を停止する直前の状態から回路の動作を再開させるためには、内部状態を保持しなくてはならない。

【0003】

例えば、特開平6−52070号公報によれば、レジスタに保持された内部状態データを電源供給停止時に外部メモリに退避させ、保持する集積回路が開示されている。この集積回路は、複数のレジスタとデータ退避部とデータ復帰部とを具備し、複数のレジスタは、スキャンチェーンを形成するように接続され、データ退避部は、外部信号に応答し、データ退避モード時に、複数のレジスタにスキャンチェーンを形成させ、形成されたスキャンチェーンを介して各レジスタの保持データを外部に読み出す。このとき、データ退避部は、内部状態データを所定のビット幅のデータに直列/並列変換し、データ入出力部を通じてデータ保護用メモリに格納する。データ復帰部は、外部信号に応答し、データ復帰モード時に、複数のレジスタにスキャンチェーンを形成させ、形成されたスキャンチェーンを介して退避していたデータをもとのレジスタに復帰させる。このとき、データ復帰部は、データ保護用メモリから内部状態データを読出してデータ入出力手段から入力し、所定のビット幅のデータを直列の内部状態データに変換してスキャンチェーンを通じて復帰する。

【0004】

また、特開2004−164647号公報によれば、1つまたは複数のノードを有する回路と、メモリと、システム・バスと、状態保存コントローラとを備えるデータ処理装置に関する技術が開示されている。1つまたは複数のノードを有する回路は、データの処理に用いられる回路であり、全体で回路の状態を定義する1つまたは複数のデータ値を記憶する。メモリは、データを記憶する。システム・バスは、回路とメモリとに結合するシステム・バスであり、回路とメモリの通常の処理動作中にシステム・バスに与えられたメモリ転送要求に応答して回路とメモリとの間で多ビット・データ語を転送する。状態保存コントローラは、回路とシステム・バスに結合し、保存トリガに応答して、回路の状態を定義するデータ値を1つまたは複数のノードから読み取ってメモリ書込み要求のシーケンスをシステム・バス上に生成し、データ値を表す1つまたは複数の状態保存多ビット・データ語をメモリに書き込んで、1つまたは複数の状態保存多ビット・データ語を用いて回路の状態を回復できるようにする。また、関連する技術として、米国公開公報2005/0149799に記載されたものもある。

【0005】

【特許文献1】特開平6−52070号公報

【特許文献2】特開2004−164647号公報

【特許文献3】米国公開公報2005/0149799

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述のように、スキャンチェーンを用いて内部状態を退避・復帰する場合には、スキャンチェーンが直列接続された多数のレジスタによって構成されているために、レジスタに保持された全てのデータをシリアルに退避・復帰するために時間がかかる。また、システムバスを介して内部ノードデータをメモリに書き込み、メモリから読み出すために、システムバスの使用権確保を含むメモリ書き込みシーケンス、メモリ読み出しシーケンスを起動する必要性があるため、やはり内部状態の退避・回復時間が長くなる。

【0007】

本発明は、半導体集積回路を待機状態にしつつ、内部状態の退避・回復時間を短縮することができる半導体集積回路及びその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0009】

本発明の観点では、半導体集積回路は、対象回路(11)と、バックアップ制御回路(12)とを具備する。対象回路(11)は、スキャンパステスト時にシフトレジスタを形成してテストデータをシリアルに入出力する少なくとも1つのスキャンチェーン(15)を備える。バックアップ制御回路(12)は、対象回路(11)の内部状態を示す内部状態データをメモリ(13)に格納し、メモリ(13)から内部状態データを読み出す。このスキャンチェーン(15)は、複数のサブスキャンチェーン(21〜24、31〜34)に分割されている。複数のサブスキャンチェーン(21〜24、31〜34)は並列に動作する。内部状態データは、複数のサブスキャンチェーン(21〜24、31〜34)から出力されてメモリ(13)に格納される。メモリ(13)に格納されている内部状態データは、複数のサブスキャンチェーン(21〜24、31〜34)に再び設定され、対象回路(11)は、元の内部状態に戻って動作を再開する。

【0010】

本発明の他の観点では、内部状態退避回復方法は、動作切替ステップと、退避ステップと、回復ステップと、再開ステップとを具備する。対象回路(11)は、スキャンパステストに使用される少なくとも1つのスキャンチェーン(15)を備える。動作切替ステップは、そのスキャンチェーン(15)を分割して、並列に動作する複数のサブスキャンチェーン(21〜24、31〜34)に構成し直す。退避ステップは、複数のサブスキャンチェーン(21〜24、31〜34)の各々から出力される対象回路(11)の内部状態を示す内部状態データをメモリ(13)に格納する。回復ステップは、メモリ(13)から出力される内部状態データを複数のサブスキャンチェーン(21〜24、31〜34)に再び設定する。再開ステップは、複数のサブスキャンチェーン(21〜24、31〜34)を解放して対象回路(11)の動作を元の状態から再開する。

【発明の効果】

【0011】

本発明によれば、スキャンチェーンを複数のサブスキャンチェーンに分割し、サブスキャンチェーンの出力を並列にメモリに格納することによって、内部状態の退避・回復時間が短縮された半導体集積回路及びその制御方法を提供することが可能になる。

【発明を実施するための最良の形態】

【0012】

図を参照して本発明の第1の実施の形態を説明する。図1は、第1の実施の形態に係る半導体集積回路の構成を示すブロック図である。半導体集積回路は、内部状態が外部に退避される対象回路11と、対象回路11の内部状態を記憶するバックアップメモリ13と、対象回路11の内部状態の退避・回復を制御するバックアップ制御回路12と、対象回路11の電源を制御するスイッチ14とを具備する。対象回路11の内部状態は、対象回路11に内在するフリップフロップに保持される内部ノードデータにより具現化される。

【0013】

バックアップ制御回路12は、対象回路11から指示(WFI)を受けて、対象回路11の動作モード(MD)を切り替え、対象回路11の内部状態を示すデータ即ち内部ノードデータをバックアップメモリ13に退避する。また、バックアップ制御回路12は、外部からの割り込み信号(INT)により起動され、バックアップメモリ13に格納されている内部ノードデータを対象回路11の各ノードに設定し、対象回路11の内部状態を回復する。この内部状態の退避・回復動作に際し、バックアップ制御回路12は、バックアップメモリ13の格納アドレス(ADDR)、書き込み・読み出しタイミング(CTR)を制御する。

【0014】

対象回路11の電源系は、他の回路と分離されている。従って、対象回路11だけの電源を切断することが可能となる。スイッチ14は、この電源の投入切断をバックアップ制御回路12の制御(PWC)に基づいて行う。

【0015】

バックアップメモリ13は、対象回路11の内部状態を示す内部ノードデータを保持する。バックアップメモリ13は、対象回路11の内部ノードデータを格納するだけの容量があればよい。内部ノードデータTOを効率よく取り込むためにデータ幅(ワード長)は広くなっている。例えば、スキャンチェーンが32個、それぞれのスキャンチェーンから4ヵ所の内部ノードデータTOを取り出すとすると、1スキャンクロック毎に128ビットのデータが並列に出力される。そのため、バックアップメモリ13は、128ビット以上のワード長が必要になる。バックアップメモリ13の書き込み/読み出しの動作タイミングCTR、アドレスADDRは、バックアップ制御回路12から与えられる。このバックアップメモリ13は、閾値電圧が高く設定され、低リーク電流のメモリである。従って、バックアップメモリ13の速度はそれほど速くないが、消費電力は少ない。また、バックアップメモリ13として、フラッシュメモリ等の不揮発性メモリを用いると、待機時にバックアップメモリ13の電源も切断することが可能となり、さらに消費電力を削減することができる。

【0016】

この対象回路11の内部状態を示す内部ノードデータは、スキャンチェーン15を介して入出力される。スキャンチェーン15は、半導体集積回路の正常性を試験するスキャンパステストに使用される。スキャンチェーン15は、スキャンパステスト時、テストデータをスキャン入力SIからシリアル入力し、テスト結果をスキャン出力SOから出力する。ここでは説明しないが、バックアップ制御回路12、バックアップメモリ13は、スキャンパステストの対象であってもよい。

【0017】

対象回路11は、待機中に保持すべき内部状態を有する回路部分である。対象回路11は、対象回路11の製造不良等を検出するために実施されるスキャンパステスト用の回路を内蔵している。このスキャンパステスト用回路は、テスト時に対象回路11に内在するフリップフロップが鎖状に接続され、シフトレジスタとしてデータの入出力を行う。このシフトレジスタが、所謂スキャンチェーンと呼ばれる。対象回路11内には、このスキャンチェーン15が少なくとも1つ設定されている。最近の半導体集積回路では、スキャンチェーン15は、32個程度設定されていることが多いが、より多くのスキャンチェーンが設定されていてもよいし、1個だけであってもよい。各スキャンチェーン15は、外部に接続されるスキャン入力SI(SI1〜SIn〜SIN)からスキャンパステスト用のシリアルデータが入力され、外部に接続されるスキャン出力SO(SO1〜SOn〜SON)からスキャンパステスト結果データがシリアルに出力される。それぞれのシリアルデータの入出力は、同期している必要はなく、スキャンチェーン毎に独立して動作していてもよい。以下、スキャンチェーン15は、スキャン入力SIn、スキャン出力SOn(n=1、2、…、N)の回路を例として説明される。

【0018】

対象回路11は、内部の論理回路が動作すると、論理回路に含まれる順序回路(フリップフロップ)にその動作状態が保持される。即ち、フリップフロップは、対象回路11の内部状態を保持している。このフリップフロップに保持された内部ノードデータを退避することにより対象回路11の内部状態が外部に出力でき、データを各フリップフロップに設定することにより対象回路11の内部状態を設定することができる。一方、フリップフロップは、スキャンパステスト時、スキャンチェーン15を形成し、その保持しているデータをシリアル出力することができる。また、スキャンチェーン15は、データをシリアル入力して、スキャンパステストするためのデータを各フリップフロップに設定することができる。従って、このスキャンチェーン15を使うことにより、フリップフロップの状態を読み出し、書き込むことが可能である。

【0019】

対象回路11は、バックアップ制御回路12の制御に基づいて、スキャンチェーン15の出力、即ち、スキャン出力SOとスキャンチェーン15の途中の複数の位置から取り出したデータTOとをバックアップメモリ13に出力する。対象回路11の全てのフリップフロップに保持されるデータが出力されると、対象回路11の内部状態がバックアップメモリ13に退避されたことになる。また、対象回路11は、バックアップ制御回路12の制御に基づいて、バックアップメモリ13から出力されるデータTIを取り込みスキャンチェーン15に設定する。スキャンチェーン15にデータが設定されると、対象回路11の内部状態が回復されたことになる。対象回路11を回復状態から通常動作状態に切り替えると、対象回路11は、通常動作に復帰する。

【0020】

図2にスキャンチェーンが有効になっている時のスキャンチェーン15の構成が示される。スキャンチェーン15は、スキャンテスト時に複数のレジスタを連結して構成される1本のチェーンであり、この1本のチェーンを複数に分割したものがサブスキャンチェーンである。スキャンチェーン15は、複数のサブスキャンチェーンを備える。ここでは、スキャンチェーン15は、4つのサブスキャンチェーン21、22、23、24を備える。サブスキャンチェーン21、22、23、24は、それぞれ同数のフリップフロップを含む。サブスキャンチェーン21、22、23、24は縦続接続され、スキャンパステストの際、1つのスキャンチェーン15として動作する。内部ノードデータの入出力時、サブスキャンチェーン21、22、23、24は並列に動作し、同時にデータを入出力する。サブスキャンチェーン21は、選択回路210と、スキャンチェーンの実体であるフリップフロップ211〜214を備える。同じように、サブスキャンチェーン22は選択回路220とフリップフロップ221〜224を備え、サブスキャンチェーン23は選択回路230とフリップフロップ231〜234を備え、サブスキャンチェーン24は選択回路240とフリップフロップ241〜244を備える。選択回路210、220、230、240は、選択信号TBに基づいて、入力される2つの信号のどちらかを選択して出力する。

【0021】

サブスキャンチェーン21では、選択回路210は、スキャン入力SInと、バックアップメモリ13に格納されていた内部ノードデータTI1とを入力する。選択回路210は、選択信号TBに基づいて、スキャンパステスト時はスキャン入力SInから入力されるデータを選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI1を選択して出力する。フリップフロップ211〜214は鎖状に接続されてシフトレジスタを形成し、選択回路210の出力信号が入力される。フリップフロップ214の出力は、内部ノードデータTO1として出力されるとともに、次段のサブスキャンチェーン22に送られる。

【0022】

サブスキャンチェーン22では、選択回路220は、前段のサブスキャンチェーン21の出力データTO1と、バックアップメモリ13に格納されていた内部ノードデータTI2とを入力する。選択回路220は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO1を選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI2を選択して出力する。フリップフロップ221〜224は、鎖状に接続されてシフトレジスタを形成し、選択回路220の出力信号が入力される。フリップフロップ224の出力は、内部ノードデータTO2として出力されるとともに、次段のサブスキャンチェーン23に送られる。

【0023】

同じように、サブスキャンチェーン23では、選択回路230は、前段のサブスキャンチェーン22の出力データTO2と、バックアップメモリ13に格納されていた内部ノードデータTI3とを入力する。選択回路230は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO2を選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI3を選択して出力する。フリップフロップ231〜234は、鎖状に接続されてシフトレジスタを形成し、選択回路230の出力信号が入力される。フリップフロップ234の出力は、内部ノードデータTO3として出力されるとともに、次段のサブスキャンチェーン24に送られる。

【0024】

同じように、サブスキャンチェーン24では、選択回路240は、前段のサブスキャンチェーン23の出力データTO3と、バックアップメモリ13に格納されていた内部ノードデータTI4とを入力する。選択信号TBに基づいて、選択回路240は、スキャンパステスト時は前段出力データTO3を選択して出力し、内部状態退避・回復時はメモリ13に記憶されている内部ノードデータTI4を選択して出力する。フリップフロップ241〜244は、鎖状に接続されてシフトレジスタを形成し、選択回路240の出力信号が入力される。フリップフロップ244の出力は、内部ノードデータTO4として出力されるとともに、スキャンチェーン15の出力SOnとして外部に出力される。

【0025】

次にスキャンチェーン15の動作が説明される。対象回路11の本来の機能動作時、フリップフロップ211〜214、フリップフロップ221〜224、フリップフロップ231〜234、フリップフロップ241〜244は、内部論理回路のレジスタとして、対象回路11の内部状態(内部ノードデータ)を保持している。

【0026】

スキャンパステストの場合、対象回路11に内在するフリップフロップは、図2に示されるように、スキャンチェーン15を構成するように接続される。スキャンチェーンに関してはよく知られているため、詳細な説明は省略される。実際には、接続配線されていて、図示されていないフリップフロップに内蔵された選択回路が、スキャンチェーンを形成する時にスキャンチェーンの信号を選択するように設定される。選択回路210、220、230、240は、選択信号TBによりスキャンデータ側のデータを選択して出力するように設定される。従って、サブスキャンチェーン21〜24に含まれるフリップフロップは、連結された1つのシフトレジスタを形成する。スキャンクロックに同期してスキャンデータは、スキャン入力SInから入力され、スキャン出力SOnに向かって順次フリップフロップを移動していく。全てのフリップフロップにスキャンデータが設定されると、各フリップフロップは、一旦スキャンチェーン15の構成から解放され、本来の内部論理回路である対象回路11のデータを取り込む。このとき、各フリップフロップはスキャンデータを出力しているため、各フリップフロップはスキャンパステストの結果を保持することになる。その後、フリップフロップはスキャンチェーン15の構成に戻る。スキャンパステストの結果を保持するシフトレジスタは、スキャンクロックに基づいて、スキャンパステストの結果データをスキャン出力SOnから出力する。

【0027】

内部ノードデータ退避の場合、スキャンチェーン15は、サブスキャンチェーン21〜24が並列に機能するように設定される。選択信号TBは、どちらに設定されていてもよいが、ここではバックアップメモリ13の出力(TI)を選択するように設定される。スキャンパステスト時と同じように、フリップフロップに保持されている内部ノードデータは、クロックに同期して並列にサブスキャンチェーンの出力データTO1〜TO4として順次バックアップメモリ13に出力される。バックアップメモリ13のアドレスADDRは、バックアップ制御回路12によりクロックに同期して更新され、サブスキャンチェーンの出力データTO1〜TO4は、バックアップメモリ13に順に記憶される。サブスキャンチェーンに含まれるフリップフロップの数だけデータを出力すると、このスキャンチェーン15に含まれる全ての内部ノードデータは、バックアップメモリ13に出力されたことになる。従って、スキャンチェーン15の出力SOnをメモリに接続して内部ノードデータを記憶させるより、出力時間は短縮できる。図2に示されるように、スキャンチェーン15をサブスキャンチェーン21〜24のように4分割すると、出力時間は1/4になる。

【0028】

内部ノードデータ回復の場合、即ち、バックアップメモリ13に保持されている内部ノードデータを元のフリップフロップに設定する場合、スキャンチェーン15は、サブスキャンチェーン21〜24が並列に機能するように設定される。選択信号TBは、バックアップメモリ13の出力(TI)を選択するように設定される。バックアップメモリ13から内部ノードデータTI1〜4がサブスキャンチェーン21〜24に入力される。バックアップ制御回路12は、バックアップメモリ13のアドレスADDRを初期設定値からクロック毎に更新して、内部ノードデータTI1〜4が退避された順にサブスキャンチェーン21〜24に供給されるように制御する。サブスキャンチェーン21〜24に供給される内部ノードデータTI1〜4は、選択回路210、220、230、240を介してサブスキャンチェーン内に形成されるシフトレジスタを出力TO1〜4に向けて移動していく。サブスキャンチェーンに含まれるフリップフロップの数だけシフトすると、各フリップフロップには元の内部ノードデータが設定されている。これで対象回路11の内部状態は回復したことになる。その後、バックアップ回復モードを解除すると、対象回路11は通常の動作に復帰する。

【0029】

このように、スキャンチェーン(サブスキャンチェーン)を用いて、内部ノードデータをバックアップメモリ13に退避し、バックアップメモリ13から内部ノードデータを対象回路11に回復する回路を内蔵する半導体集積回路の動作状態が図3を参照して説明される。ここでは、対象回路11は、半導体集積回路に内蔵されるCPU(中央演算処理部)であるとし、CPUが実行しているソフトウェアの処理状態が対象回路11の状態として説明される。図3の左側に半導体集積回路を外部(ソフトウェア)の観点で見たときの動作状態が示される。図3の右側に内部(ハードウェア)の観点で見たときの対象回路11、バックアップ制御回路12、バックアップメモリ13の動作状態が示される。

【0030】

半導体集積回路は、通常の動作において、例えば、周期処理やマンマシンインタフェース処理等により待機状態になることがある。そのとき、CPU11は、WFI(Wait for Interrupt)命令を実行し、待機状態になる。通常、待機状態では、ソフトウェアの実行は停止される。その場合、処理再開を指示する割り込み信号INTが入力されると即時実行再開ができるように、ハードウェアは必要最小限の待機電圧まで電源電圧を引き下げ、消費電力を削減する。さらに消費電力を削減するために、本発明では、図3に破線により囲まれて示されるように、CPU11の電源供給が停止され、待機状態におけるリーク電流が削減される。CPU11の電源がオフされると、CPU11の内部状態がクリアされるため、電源がオフされる前に、CPU11の内部状態がバックアップメモリ13に退避される。

【0031】

CPU11の動作を再開するトリガとなる割り込み信号INTがバックアップ制御回路12に入力されると、CPU11の電源がオンされる。CPU11の内部状態がバックアップメモリ13から回復され、ソフトウェアの実行が再開される。割り込み信号INTが入力されるため、ソフトウェアは割り込み処理をまず実行し、その後通常の処理に戻ることになる。従って、ソフトウェアとしては、電源のオン・オフに影響されずに、待機状態が維持されていたように動作することになる。

【0032】

即ち、対象回路(CPU)11は、WFI命令が発行されるまで通常の作動状態であり、WFI命令によりソフトウェアは停止するため、内部状態は凍結される。WFI命令が発行されると、バックアップ制御回路12とバックアップメモリ13は、待機状態から起動される。バックアップ制御回路12は、対象回路(CPU)11をスキャンチェーンが設定される退避状態にする。バックアップ制御回路12は、対象回路(CPU)11の凍結された内部ノードデータをバックアップメモリ13に退避する。対象回路(CPU)11の全ての内部ノードデータが退避されると、バックアップ制御回路12は、スイッチ14を制御して対象回路(CPU)11の電源供給を停止する。バックアップ制御回路12は、割り込み信号INTが入力されるまで、待機状態になる。バックアップ制御回路12とバックアップメモリ13は、対象回路(CPU)11に比較して回路規模も小さく、また、低消費電力になるように構成されるため、リーク電流は削減される。

【0033】

割り込み信号INTがバックアップ制御回路12に入力されると、バックアップ制御回路12は、待機状態から作動状態に復帰する。まず、バックアップ制御回路12は、スイッチ14を制御して対象回路(CPU)11の電源供給を再開する。次に、バックアップ制御回路12は、対象回路(CPU)11をスキャンチェーンが設定される回復状態にする。バックアップ制御回路12は、バックアップメモリ13に記憶されている内部ノードデータTIをサブスキャンチェーンに供給し、内部状態をリストアする。対象回路(CPU)11の内部状態が元の状態に回復すると、バックアップ制御回路12は、対象回路(CPU)11の回復状態を解除して対象回路(CPU)11を起動する。対象回路(CPU)11は、動作を再開する。バックアップ制御回路12とバックアップメモリ13は、次のWFI命令発行まで待機状態になる。ここでは、対象回路11はCPUであるとして説明されたが、対象回路11はCPUに限らずランダムロジック回路でも同様に実施することが可能である。

【0034】

このように、スキャンチェーン15よりも短いサブスキャンチェーン21〜24にシリアルデータを送り込んで内部状態を再設定することになり、復帰時間は短縮される。上述のように、本発明によれば、より短い時間で内部状態を退避・回復することが可能になり、かつ、待機期間のリーク電流を削減することができる。

【0035】

図4は、さらに最小回復時間を短縮するための経路を設けたスキャンチェーンの構成を示すブロック図である。最小回復時間は、内部状態データの退避が開始された直後に退避の中止、即ち、内部状態データの回復が指示されたときに要する時間である。図4に示されるスキャンチェーン15は、図2に示されるサブスキャンチェーン21〜24の各々の先頭にさらに選択回路が設けられている。

【0036】

このスキャンチェーン15は、サブスキャンチェーン31、32、33、34を備える。サブスキャンチェーン31は、選択回路319、310とフリップフロップ311〜314を備える。同じように、サブスキャンチェーン32は、選択回路329、320とフリップフロップ321〜324を備え、サブスキャンチェーン33は、選択回路339、330とフリップフロップ331〜334を備え、サブスキャンチェーン34は、選択回路349、340とフリップフロップ341〜344を備える。選択回路319、329、339、349を除く部分は、図2に示されるスキャンチェーンと同じである。

【0037】

選択回路319、329、339、349は、選択信号BRに基づいて、バックアップメモリ13が出力する退避された内部ノードデータTIと、サブスキャンチェーンが出力する内部ノードデータTOのいずれかを選択して選択回路310、320、330、340に出力する。

【0038】

サブスキャンチェーン31では、選択回路319は、バックアップメモリ13から入力される内部ノードデータTI1と、サブスキャンチェーン31が出力する内部ノードデータTO1とを入力する。選択回路319は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO1を選択して出力し、内部状態回復時は退避されていた内部ノードデータTI1を選択して出力する。選択回路310は、スキャン入力SInと、選択回路319の出力信号とを入力する。選択回路310は、選択信号TBに基づいて、スキャンパステスト時はスキャン入力信号SInを選択して出力し、内部状態退避・回復時は選択回路319の出力信号を選択して出力する。フリップフロップ311〜314は、鎖状に接続されてシフトレジスタを形成し、選択回路310の出力信号が入力される。フリップフロップ314の出力信号は、内部ノードデータTO1として出力されるとともに、次段のサブスキャンチェーン32に送られる。

【0039】

サブスキャンチェーン32では、選択回路329は、バックアップメモリ13から入力される内部ノードデータTI2と、サブスキャンチェーン32が出力する内部ノードデータTO2とを入力する。選択回路329は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO2を選択して出力し、内部状態回復時は退避されていた内部状態TI2を選択して出力する。選択回路320は、前段のサブスキャンチェーン31の出力データTO1と、選択回路329の出力信号とを入力する。選択回路320は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO1を選択して出力し、内部状態退避・回復時は選択回路329の出力信号を選択して出力する。フリップフロップ321〜324は、鎖状に接続されてシフトレジスタを形成し、選択回路320の出力信号が入力される。フリップフロップ324の出力信号は、内部ノードデータTO2として出力されるとともに、次段のサブスキャンチェーン33に送られる。

【0040】

同じように、サブスキャンチェーン33では、選択回路339は、バックアップメモリ13から入力される内部ノードデータTI3と、サブスキャンチェーン33が出力する内部ノードデータTO3とを入力する。選択回路339は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO3を選択して出力し、内部状態回復時は退避されていた内部状態TI3を選択して出力する。選択回路330は、前段のサブスキャンチェーン32の出力データTO2と、選択回路339の出力データとを入力する。選択回路330は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO2を選択して出力し、内部状態退避・回復時は選択回路339の出力信号を選択して出力する。フリップフロップ331〜334は、鎖状に接続されてシフトレジスタを形成し、選択回路330の出力信号が入力される。フリップフロップ334の出力は、内部ノードデータTO3として出力されるとともに、次段のサブスキャンチェーン34に送られる。

【0041】

同じように、サブスキャンチェーン34では、選択回路349は、バックアップメモリ13から入力される内部ノードデータTI4と、サブスキャンチェーン34が出力する内部ノードデータTO4とを入力する。選択回路349は、選択信号BRに基づいて、内部状態退避時はフィードバックされるように内部ノードデータTO4を選択して出力し、内部状態回復時は退避されていた内部状態TI4を選択して出力する。選択回路340は、前段のサブスキャンチェーン33の出力データTO3と、選択回路349の出力データとを入力する。選択回路340は、選択信号TBに基づいて、スキャンパステスト時は前段出力データTO3を選択して出力し、内部状態退避・回復時は選択回路349の出力信号を選択して出力する。フリップフロップ341〜344は、鎖状に接続されてシフトレジスタを形成し、選択回路340の出力信号が入力される。フリップフロップ344の出力は、内部ノードデータTO4として出力されるとともに、スキャンチェーン15の出力SOnとして外部に出力される。

【0042】

図5A、B、Cを参照してスキャンチェーン15の動作が説明される。スキャンチェーンが形成されていない時、フリップフロップ311〜314、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344は、対象回路11の内部状態を保持している。

【0043】

スキャンパステストの場合、図5Aに示されるように、対象回路11に内在するフリップフロップはスキャンチェーンを形成する。このとき、選択信号TBは、スキャンパステスト用のデータを選択するように設定される。選択信号BRの設定は、信号の経路に影響しないのでどちらでもよい。従って、フリップフロップ311〜314、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344は、連続する1つのシフトレジスタを形成する。図5Aに太線で示されるように、スキャンパステスト用データは、スキャン入力SInから入力され、順次フリップフロップを移動して各フリップフロップに設定される。

【0044】

各フリップフロップにスキャンパステスト用データが設定されると、一旦スキャンチェーンは解除され、内部論理の動作チェックが行われる。その結果は、各フリップフロップに取り込まれ、再度スキャンチェーンが形成される。各フリップフロップに設定されたチェック結果は、シフトレジスタを形成しているフリップフロップを移動してスキャン出力SOnから順次出力される。このように、スキャンパステストにおけるデータの入出力が行われる。

【0045】

次に、図5Bを参照して対象回路11の内部ノードデータをバックアップメモリ13に退避する退避動作が説明される。内部ノードデータの退避動作の場合、選択回路310、320、330、340は、それぞれ、選択信号TBに基づいて、選択回路319、329、339、349から入力されるデータを選択して出力するように設定される。選択信号BRは、サブスキャンチェーン31〜34の出力TO1〜TO4をそれぞれ自身の入力TI1〜TI4に戻すように設定される。即ち、図5Bに太線で示されるように、内部ノードデータは、各サブスキャンチェーン内で循環するようにシフトされる。従って、サブスキャンチェーン31に保持されていた内部ノードデータが全て出力データTO1として出力されると、フリップフロップ311〜314には元の内部ノードデータが設定されていることになる。サブスキャンチェーン32、33、34においても同じように、内部ノードデータを全て出力し終わると、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344は、元の内部ノードデータを保持する。

【0046】

これは、内部ノードデータの退避と回復とを同時に行っていることに他ならない。例えば、対象回路11の内部ノードデータをバックアップメモリ13に退避している最中に割り込み信号INTが入力され、復帰動作を開始しなければならない場合、退避動作が完了した時点で対象回路の動作を再開することが可能となる。図2に示されるスキャンチェーン15の構成では、一旦退避動作が開始されると、内部ノードデータを全てバックアップメモリ13に退避し、その後バックアップメモリ13から内部ノードデータをスキャンチェーン15に回復させる必要がある。それに対して、このように、サブスキャンチェーン31〜34の内部ノードデータTO1〜TO4を自身に循環させることにより、退避動作直後に対象回路11の通常動作を再開することが可能となる。従って、退避動作が開始されてから動作回復までの時間を短縮することができる。

【0047】

図5Cを参照してバックアップメモリ13に格納されている内部ノードデータから対象回路11の内部状態を回復する回復動作が説明される。バックアップメモリ13には、図5Bを参照して説明されたように、対象回路11の内部ノードデータが順に格納されている。このデータを対象回路11に回復する場合、選択回路310、320、330、340は、選択信号TBに基づいて、それぞれ選択回路319、329、339、349から入力されるデータを選択して出力するように設定される。選択信号BRは、選択回路319、329、339、349がバックアップメモリ13から出力される内部ノードデータTIを選択して出力するように設定される。

【0048】

即ち、図5Cに太線で示されるように、バックアップメモリ13から入力される内部ノードデータTI1は、サブスキャンチェーン31内をシフトされてフリップフロップ311〜314に設定される。同じように、内部ノードデータTI2は、サブスキャンチェーン32内をシフトされてフリップフロップ321〜324に設定される。内部ノードデータTI3は、サブスキャンチェーン33内をシフトされてフリップフロップ331〜334に設定される。内部ノードデータTI4は、サブスキャンチェーン34内をシフトされてフリップフロップ341〜344に設定される。

【0049】

このように、バックアップメモリ13に保持されている内部ノードデータは、フリップフロップ311〜314、フリップフロップ321〜324、フリップフロップ331〜334、フリップフロップ341〜344に格納され、元の内部状態に戻る。その後、スキャンチェーンが解除されて対象回路11は通常の動作に復帰する。

【0050】

上述において、サブスキャンチェーンは、それぞれ同数のフリップフロップを含むものとして説明したが、スキャンチェーン15に含まれるフリップフロップの総数は、サブスキャンチェーン数の倍数であるとは限らない。従って、各サブスキャンチェーンに含まれるフリップフロップの数が異なる場合、仮の内部ノードデータを保持するダミーのフリップフロップを挿入して数を揃えることが好ましい。また、含まれるフリップフロップの数が等しいサブスキャンチェーン毎に同時にバックアップメモリに出力するように構成することも可能である。その場合、挿入されるダミーフリップフロップの数を少なく、あるいは不用とすることができる。また、サブスキャンチェーン毎に与えるシフトクロックを変えることにより、内蔵するフリップフロップの数が異なるサブスキャンチェーンの内部ノードデータを退避・回復することも可能である。

【0051】

図6は、ダミーフリップフロップを備えたスキャンチェーン15の一例を示すブロック図である。このダミーフリップフロップは、他のスキャンチェーンに属し、スキャンパステストの時、他のスキャンチェーンの一部として動作する。図6に示されるスキャンチェーン15は、図2に示されるスキャンチェーンのフリップフロップ224、241がない状態である。即ち、図6に示されるスキャンチェーン15は、サブスキャンチェーン22、24に含まれるフリップフロップの数が、サブスキャンチェーン21、23より少ない。サブスキャンチェーン22は、スキャンチェーン15に含まれていないフリップフロップ(以降ダミーフリップフロップと称する)224’をフリップフロップ223の後段に接続される。従って、フリップフロップ223は、ダミーフリップフロップ224’と次段のサブスキャンチェーン23の選択回路230とに接続される。ダミーフリップフロップ224’は、フリップフロップ223の出力をバックアップメモリ13に出力する。また、サブスキャンチェーン24は、ダミーフリップフロップ241’を選択回路240の前段に接続される。バックアップメモリ13から出力された内部ノードデータTI4は、ダミーフリップフロップ241’に入力される。ダミーフリップフロプ241’の出力は、選択回路240を介してシフトレジスタを構成するフリップフロップ242〜244に入力される。このように、ダミーフリップフロップ224’、241’をサブスキャンチェーン22、24に接続することにより、サブスキャンチェーン21、23に含まれるフリップフロップと同数のフリップフロップを含むサブスキャンチェーン22’、24’が形成される。従って、サブスキャンチェーン21、22’、23、24’は、同じデータ数の内部状態データをバックアップメモリ13に出力することが可能となる。また、サブスキャンチェーン21、22’、23、24’は、同じデータ数の内部状態データをバックアップメモリ13から取り込んで各フリップフロップに設定することが可能となる。ここでは、過不足のフリップフロップ数はサブスキャンチェーン当たり1回路で説明したが、複数であっても各サブスキャンチェーンのフリップフロップ数を揃えることはできる。また、ダミーフリップフロップは、元のサブスキャンチェーンの前後のどちらに接続されても、さらに前後両側に接続されても同じように動作する。また、このダミーフリップフロップが接続されたサブスキャンチェーンの先頭に第2の選択回路を配置し、図4に示されるように、各サブスキャンチェーンの出力を先頭にフィードバックする構成にすることも可能である。

【0052】

このように、ダミーフリップフロップを接続することにより、スキャンパステスト時のスキャンチェーンにダミーフリップフロップを含むことなく、サブスキャンチェーンに含まれるフリップフロップの数をそろえることができる。このダミーフリップフロップは、バックアップ制御回路と一緒にスキャンチェーンに含めることができ、対象回路のスキャンパステストに影響を与えることを防ぐことができる。

【0053】

次に、図7を参照して第2の実施の形態が説明される。第2の実施の形態では、スキャンチェーンとバックアップメモリとのインタフェースが第1の実施の形態と異なる例が説明される。図7に、半導体集積回路の構成ブロック図が示される。半導体集積回路は、対象回路11とバックアップメモリ13とバックアップ制御回路12とスイッチ14とバスインタフェース部16とを具備する。対象回路11は、内部状態が外部に退避される回路であり、その電源はスイッチ14により制御される。スイッチ14は、バックアップ制御回路12により制御される。対象回路11の内部状態は、バスインタフェース部16によりシステムバス18に乗せられ、バックアップメモリ13に退避される。また、バックアップメモリ13に記憶されている内部状態は、システムバス18に乗せられ、バスインタフェース部16を介して対象回路11に回復される。対象回路11の内部状態の退避・回復は、バックアップ制御回路12により制御される。

【0054】

対象回路11の構成、動作は、図1に示される回路と同じである。従って、スキャンチェーン15に保持される内部状態は、スキャンパステストのときスキャン出力SOとして外部に出力される。対象回路11の内部状態退避のとき、スキャンチェーン15に保持される内部ノードデータは、サブスキャンチェーンに分割されたパスを介してバスインタフェース部16に送られる。このとき、内部ノードデータは、バスインタフェース部16において、バス幅に等しいデータ幅でバスインタフェース部16に送られることが好ましい。バスインタフェース部16は、内部ノードデータの信号レベルやタイミングを調整してシステムバス18に出力する。これに同期して、バックアップメモリ13は、システムバス18から内部ノードデータを取り込み、記憶する。バックアップメモリ13のアドレスADDRは、バックアップ制御回路12から供給される。

【0055】

対象回路11の内部状態回復のとき、バックアップメモリ13に格納されている内部ノードデータは、バックアップ制御回路12から出力されるアドレスADDRに基づいて読み出され、システムバス18に送られる。これに同期して、バスインタフェース部16は、システムバス18からデータを取り込み、対象回路11のサブスキャンチェーンに内部ノードデータTIとして供給する。システムバス18からデータを取り込むタイミング、信号レベルの変換などは、バスインタフェース部16が調整する。サブスキャンチェーンは、第1の実施の形態において説明された動作を行う。

【0056】

このように、内部ノードデータTOは、システムバス18を介してバックアップメモリ13に格納され、バックアップメモリ13に格納される内部ノードデータは、システムバス18を介して対象回路11に内部ノードデータTIとして供給され、対象回路11は、元の内部状態に戻る。

【0057】

システムバス18を介して対象回路11の内部ノードデータをバックアップメモリ13に退避し、バックアップメモリ13から回復することにより、半導体集積回路は、システムバス18に接続されているシステムメモリの一部をバックアップメモリ13として使用することも可能となる。その場合、バックアップ制御回路12は、システムバス18のインタフェース仕様に基づいてメモリをアクセスすることになる。

【0058】

また、システムバス18を介してシステムメモリにアクセス可能となれば、バックアップメモリ13は、対象回路11を内蔵する半導体集積回路の外部にあってもよいことになる。即ち、汎用のインタフェースがサポートされることにより、バックアップメモリとして使用されるメモリの選択の自由度が向上する。

【0059】

上述のように、スキャンチェーンをサブスキャンチェーンに分割することにより、対象回路11の内部ノードデータは、短時間に退避され、回復されるようになる。さらに、対象回路11の内部状態が外部で保持されるため、対象回路11の電源供給を停止することができ、消費電力の低減が可能となる。また、サブスキャンチェーンの各々の先頭に選択回路を挿入し、サブスキャンチェーンの出力を戻すことにより、内部状態の退避動作の中止に応じる回復動作の時間をさらに短縮することが可能となる。

【図面の簡単な説明】

【0060】

【図1】本発明の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【図2】同スキャンチェーンの構成を示すブロック図である。

【図3】同半導体集積回路の動作状態を示す図である。

【図4】同スキャンチェーンの他の構成を示すブロック図である。

【図5A】同他の構成のスキャンチェーンのテスト時の動作を示す図である。

【図5B】同他の構成のスキャンチェーンの退避時の動作を示す図である。

【図5C】同他の構成のスキャンチェーンの回復時の動作を示す図である。

【図6】同ダミーフリップフロップを備えるスキャンチェーンの構成を示すブロック図である。

【図7】同半導体集積回路の他の構成を示すブロック図である。

【符号の説明】

【0061】

11 対象回路

12 バックアップ制御回路

13 バックアップメモリ

14 スイッチ

15 スキャンチェーン

16 バスインタフェース部

18 システムバス

21、22、23、24 サブスキャンチェーン

210、220、230、240 選択回路

211〜214、221〜224、231〜234、241〜244 フリップフロップ

31、32、33、34 サブスキャンチェーン

310、320、330、340 選択回路

311〜314、321〜324、331〜334、341〜344 フリップフロップ

319、329、339、349 選択回路

【特許請求の範囲】

【請求項1】

スキャンパステスト時にシフトレジスタを形成してテストデータをシリアルに入出力する少なくとも1つのスキャンチェーンを備える対象回路と、

前記対象回路の内部状態を示す内部状態データをメモリに格納し、前記メモリから読み出すバックアップ制御回路と

を具備し、

前記スキャンチェーンは、複数のサブスキャンチェーンに分割され、前記複数のサブスキャンチェーンは並列に動作し、

前記内部状態データは、前記複数のサブスキャンチェーンから出力されて前記メモリに格納され、

前記メモリに格納されている前記内部状態データは、前記複数のサブスキャンチェーンに再び設定される

半導体集積回路。

【請求項2】

前記複数のサブスキャンチェーンの各々は、

シフトレジスタを形成する複数のフリップフロップと、

前記バックアップ制御回路の制御に基づいて、前記スキャンパステストを行うための前記テストデータと、前記メモリから出力される前記内部状態データとのいずれかを選択して前記複数のフリップフロップに出力する第1選択回路と

を備える

請求項1に記載の半導体集積回路。

【請求項3】

前記複数のサブスキャンチェーンの各々は、更に、第2選択回路を備え、

前記第2選択回路は、前記バックアップ制御回路の制御に基づいて、前記メモリから出力される前記内部状態データと、前記第2選択回路を備えるサブスキャンチェーンの出力データとのいずれかを選択して出力し、

前記第1選択回路は、前記バックアップ制御回路の制御に基づいて、前記第2選択回路から出力される選択データと、前記テストデータとのいずれかを選択して前記複数のフリップフロップに出力する

請求項2に記載の半導体集積回路。

【請求項4】

前記複数のサブスキャンチェーンの各々は、同数の前記複数のフリップフロップを備える

請求項2または請求項3に記載の半導体集積回路。

【請求項5】

前記複数のサブスキャンチェーンは、前記複数のサブスキャンチェーンの各々が備える前記複数のフリップフロップの最大数に揃えるように、仮の内部状態データを保持するダミーフリップフロップを備える

請求項2または請求項3に記載の半導体集積回路。

【請求項6】

前記複数のサブスキャンチェーンは、さらに、前記複数のサブスキャンチェーンの各々の入力から出力までの間に同数のフリップフロップが含まれるように、前記スキャンチェーンとは異なる第2スキャンチェーンに接続される第2ダミーフリップフロップを備え、

前記複数のフリップフロップは、前記第2ダミーフリップフロップを介して前記メモリに接続される

請求項2から請求項5のいずれかに記載の半導体集積回路。

【請求項7】

前記第2ダミーフリップフロップは、前記複数のフリップフロップの最終段の出力と、前記メモリの入力との間に設けられる

請求項6に記載の半導体集積回路。

【請求項8】

前記第2ダミーフリップフロップは、前記メモリの出力と、前記第1選択回路の入力との間に設けられる

請求項6または請求項7に記載の半導体集積回路。

【請求項9】

前記複数のサブスキャンチェーンのうち、同数の前記フリップフロップを備えるサブスキャンチェーン毎に前記内部状態データを出力して前記メモリに記憶する

請求項2から請求項8のいずれかに記載の半導体集積回路。

【請求項10】

前記複数のサブスキャンチェーンの各々は、独立に制御されるクロック信号により保持するデータをシフトする

請求項1から請求項9のいずれかに記載の半導体集積回路。

【請求項11】

前記メモリを内部に具備する

請求項1から請求項10のいずれかに記載の半導体集積回路。

【請求項12】

前記メモリは、高い閾値電圧に設定された低リーク電流のメモリである

請求項11に記載の半導体集積回路。

【請求項13】

前記メモリは、書き換え可能な不揮発性メモリである

請求項11に記載の半導体集積回路。

【請求項14】

前記バックアップ制御回路の制御信号に応答して、前記対象回路に供給される電源を投入/切断するスイッチを更に備え、

前記バックアップ制御回路は、前記内部状態データを前記メモリに記憶させた後に、前記スイッチを制御して前記対象回路の電源を切断する

請求項1から請求項13のいずれかに記載の半導体集積回路。

【請求項15】

前記バックアップ制御回路は、

外部から入力される割り込み信号に基づいて、前記スイッチを制御して前記対象回路の電源を投入し、

前記メモリに格納される前記内部状態データを前記複数のサブスキャンチェーンに再び設定する

請求項14に記載の半導体集積回路。

【請求項16】

さらに、前記内部状態データをシステムバスに乗せるバスインタフェース部を備え、

前記内部状態データは、前記システムバスを介して前記メモリに記憶される

請求項1から請求項15に記載の半導体集積回路。

【請求項17】

前記メモリは、前記システムバスに接続され、前記対象回路内に前記スキャンチェーンが形成されていない時に前記対象回路が使用するシステムメモリの一部である

請求項16に記載の半導体集積回路。

【請求項18】

対象回路のスキャンパステストに使用される少なくとも1つのスキャンチェーンを、並列に動作する複数のサブスキャンチェーンに構成し直す動作切替ステップと、

前記複数のサブスキャンチェーンの各々から出力される前記対象回路の内部状態を示す内部状態データをメモリに格納する退避ステップと、

前記メモリから出力される前記内部状態データを前記複数のサブスキャンチェーンに再び設定する回復ステップと、

前記複数のサブスキャンチェーンを解放して前記対象回路の動作を再開する再開ステップと

を具備する内部状態退避回復方法。

【請求項19】

前記退避ステップの後に前記対象回路の電源を切断する電源切断ステップと、

外部から入力される割り込み信号に応答して前記対象回路の電源を投入する電源投入ステップと

をさらに備え、

前記電源投入ステップにより前記対象回路に電源が投入された直後に前記回復ステップが実行される

請求項18に記載の内部状態退避回復方法。

【請求項20】

メモリと、

スキャンパステスト時に複数のフリップフロップを接続してシフトレジスタを形成しテストデータをシリアルに入出力する連続したスキャンチェーンであって、退避時には複数のサブスキャンチェーンに分割されるスキャンチェーンと、

前記退避時に前記複数のサブスキャンチェーンに保持されたデータを前記メモリに並列に格納する制御回路と

を備えることを特徴とする半導体集積回路。

【請求項21】

前記制御回路は、復帰時に前記メモリに保持されたデータを、前記複数のサブスキャンチェーンに並列に書き込むことを特徴とする請求項20記載の半導体集積回路。

【請求項1】

スキャンパステスト時にシフトレジスタを形成してテストデータをシリアルに入出力する少なくとも1つのスキャンチェーンを備える対象回路と、

前記対象回路の内部状態を示す内部状態データをメモリに格納し、前記メモリから読み出すバックアップ制御回路と

を具備し、

前記スキャンチェーンは、複数のサブスキャンチェーンに分割され、前記複数のサブスキャンチェーンは並列に動作し、

前記内部状態データは、前記複数のサブスキャンチェーンから出力されて前記メモリに格納され、

前記メモリに格納されている前記内部状態データは、前記複数のサブスキャンチェーンに再び設定される

半導体集積回路。

【請求項2】

前記複数のサブスキャンチェーンの各々は、

シフトレジスタを形成する複数のフリップフロップと、

前記バックアップ制御回路の制御に基づいて、前記スキャンパステストを行うための前記テストデータと、前記メモリから出力される前記内部状態データとのいずれかを選択して前記複数のフリップフロップに出力する第1選択回路と

を備える

請求項1に記載の半導体集積回路。

【請求項3】

前記複数のサブスキャンチェーンの各々は、更に、第2選択回路を備え、

前記第2選択回路は、前記バックアップ制御回路の制御に基づいて、前記メモリから出力される前記内部状態データと、前記第2選択回路を備えるサブスキャンチェーンの出力データとのいずれかを選択して出力し、

前記第1選択回路は、前記バックアップ制御回路の制御に基づいて、前記第2選択回路から出力される選択データと、前記テストデータとのいずれかを選択して前記複数のフリップフロップに出力する

請求項2に記載の半導体集積回路。

【請求項4】

前記複数のサブスキャンチェーンの各々は、同数の前記複数のフリップフロップを備える

請求項2または請求項3に記載の半導体集積回路。

【請求項5】

前記複数のサブスキャンチェーンは、前記複数のサブスキャンチェーンの各々が備える前記複数のフリップフロップの最大数に揃えるように、仮の内部状態データを保持するダミーフリップフロップを備える

請求項2または請求項3に記載の半導体集積回路。

【請求項6】

前記複数のサブスキャンチェーンは、さらに、前記複数のサブスキャンチェーンの各々の入力から出力までの間に同数のフリップフロップが含まれるように、前記スキャンチェーンとは異なる第2スキャンチェーンに接続される第2ダミーフリップフロップを備え、

前記複数のフリップフロップは、前記第2ダミーフリップフロップを介して前記メモリに接続される

請求項2から請求項5のいずれかに記載の半導体集積回路。

【請求項7】

前記第2ダミーフリップフロップは、前記複数のフリップフロップの最終段の出力と、前記メモリの入力との間に設けられる

請求項6に記載の半導体集積回路。

【請求項8】

前記第2ダミーフリップフロップは、前記メモリの出力と、前記第1選択回路の入力との間に設けられる

請求項6または請求項7に記載の半導体集積回路。

【請求項9】

前記複数のサブスキャンチェーンのうち、同数の前記フリップフロップを備えるサブスキャンチェーン毎に前記内部状態データを出力して前記メモリに記憶する

請求項2から請求項8のいずれかに記載の半導体集積回路。

【請求項10】

前記複数のサブスキャンチェーンの各々は、独立に制御されるクロック信号により保持するデータをシフトする

請求項1から請求項9のいずれかに記載の半導体集積回路。

【請求項11】

前記メモリを内部に具備する

請求項1から請求項10のいずれかに記載の半導体集積回路。

【請求項12】

前記メモリは、高い閾値電圧に設定された低リーク電流のメモリである

請求項11に記載の半導体集積回路。

【請求項13】

前記メモリは、書き換え可能な不揮発性メモリである

請求項11に記載の半導体集積回路。

【請求項14】

前記バックアップ制御回路の制御信号に応答して、前記対象回路に供給される電源を投入/切断するスイッチを更に備え、

前記バックアップ制御回路は、前記内部状態データを前記メモリに記憶させた後に、前記スイッチを制御して前記対象回路の電源を切断する

請求項1から請求項13のいずれかに記載の半導体集積回路。

【請求項15】

前記バックアップ制御回路は、

外部から入力される割り込み信号に基づいて、前記スイッチを制御して前記対象回路の電源を投入し、

前記メモリに格納される前記内部状態データを前記複数のサブスキャンチェーンに再び設定する

請求項14に記載の半導体集積回路。

【請求項16】

さらに、前記内部状態データをシステムバスに乗せるバスインタフェース部を備え、

前記内部状態データは、前記システムバスを介して前記メモリに記憶される

請求項1から請求項15に記載の半導体集積回路。

【請求項17】

前記メモリは、前記システムバスに接続され、前記対象回路内に前記スキャンチェーンが形成されていない時に前記対象回路が使用するシステムメモリの一部である

請求項16に記載の半導体集積回路。

【請求項18】

対象回路のスキャンパステストに使用される少なくとも1つのスキャンチェーンを、並列に動作する複数のサブスキャンチェーンに構成し直す動作切替ステップと、

前記複数のサブスキャンチェーンの各々から出力される前記対象回路の内部状態を示す内部状態データをメモリに格納する退避ステップと、

前記メモリから出力される前記内部状態データを前記複数のサブスキャンチェーンに再び設定する回復ステップと、

前記複数のサブスキャンチェーンを解放して前記対象回路の動作を再開する再開ステップと

を具備する内部状態退避回復方法。

【請求項19】

前記退避ステップの後に前記対象回路の電源を切断する電源切断ステップと、

外部から入力される割り込み信号に応答して前記対象回路の電源を投入する電源投入ステップと

をさらに備え、

前記電源投入ステップにより前記対象回路に電源が投入された直後に前記回復ステップが実行される

請求項18に記載の内部状態退避回復方法。

【請求項20】

メモリと、

スキャンパステスト時に複数のフリップフロップを接続してシフトレジスタを形成しテストデータをシリアルに入出力する連続したスキャンチェーンであって、退避時には複数のサブスキャンチェーンに分割されるスキャンチェーンと、

前記退避時に前記複数のサブスキャンチェーンに保持されたデータを前記メモリに並列に格納する制御回路と

を備えることを特徴とする半導体集積回路。

【請求項21】

前記制御回路は、復帰時に前記メモリに保持されたデータを、前記複数のサブスキャンチェーンに並列に書き込むことを特徴とする請求項20記載の半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図6】

【図7】

【公開番号】特開2007−157027(P2007−157027A)

【公開日】平成19年6月21日(2007.6.21)

【国際特許分類】

【出願番号】特願2005−354492(P2005−354492)

【出願日】平成17年12月8日(2005.12.8)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成19年6月21日(2007.6.21)

【国際特許分類】

【出願日】平成17年12月8日(2005.12.8)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]